НИИСИ РАН, г.Москва

реклама

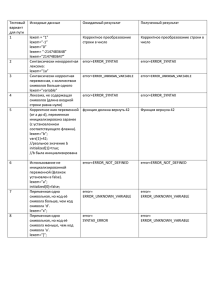

МЕТОДЫ КОРРЕКЦИИ КРАТНЫХ ОШИБОК В СБИС ОЗУ Краснюк А.А., Черкасов И.Г., Петров К.А. НИИ системных исследований РАН, г. Москва Схемотехнические методы защиты данных P2 P2 P0 P3 P0 P3 L N0 N0 N2 N2 LL==11мкм мкм L = = P1 P1 1 1, ,7 м 7 мк км м N1N1 N3 N3 P2 P3 L N0 N1 = 7 1, P0 P1 N2 N3 м мк L = 3,5 мкм Современные многоядерные микропроцессоры 400 Гбит/с. Конструктивнотопологические меры Возможные корректирующие коды для элементов памяти СБИС ОЗУ The following list shows common error correction capabilities for memory devices: ● SEC (single error correction) Hamming codes ● SEC-DED (single error correction double error detection) Hsiao codes ● SEC-DED-SBD (single error correction/double error detection/single byte error detection) Reddy codes ● SBC-DBD (single byte error correction/double byte error detection) finite fieldbased codes. ● DEC-TED (double error correction/triple error detection) Bose-ChaudhuriHocquenghem codes. (с) IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems Унифицированный функциональный элемент XOR Топология ячейки XOR Архитектура кодера Hsiao Результаты моделирования кодеров–декодеров для 4–х и 64–х разрядных элементов микропроцессоров Тестовый кодер декодер Hsiao Временные диаграммы работы Детектирующая способность кодека Кодер Рида-Соломона Организация помехоустойчивого ЗУ по Риду– Соломону Данные ЗУ представляются в форме числа, например 123456790029984477857644356727 Определяются соответствующие А и В: А:В=0,123456790029984477857644356727 Запись в ЗУ признаков А и В Спасибо за внимание The more you know, the more you learn; The more you learn, the more you can do; The more you can do, the more opportunity! --- Richard W. Hamming