PRINTED

CIRCUITS

HANDBOOK

To Ann

ABOUT THE EDITOR

Clyde F. Coombs, Jr. recently retired from Hewlett-Packard, where he had worked as an electronics engineer and manager. One of the most successful editors in professional publishing

today, he developed and edited all five previous editions of the Printed Circuits Handbook,

and also edited the Electronic Instrument Handbook and the Communications Network Test

and Measurement Handbook, three of McGraw-Hill’s best-selling technical handbooks.

Copyright © 2008 by The McGraw-Hill Companies. Click here for terms of use.

PRINTED

CIRCUITS

HANDBOOK

Clyde F. Coombs, Jr.

Editor-in-Chief

Sixth Edition

New York Chicago San Francisco Lisbon

London Madrid Mexico City Milan

New Delhi San Juan Seoul

Singapore Sydney Toronto

Copyright © 2008 by The McGraw-Hill Companies. All rights reserved. Manufactured in the United States of America. Except as

permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form

or by any means, or stored in a database or retrieval system, without the prior written permission of the publisher.

0-07-151079-6

The material in this eBook also appears in the print version of this title: 0-07-146734-3.

All trademarks are trademarks of their respective owners. Rather than put a trademark symbol after every occurrence of a

trademarked name, we use names in an editorial fashion only, and to the benefit of the trademark owner, with no intention of

infringement of the trademark. Where such designations appear in this book, they have been printed with initial caps.

McGraw-Hill eBooks are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate

training programs. For more information, please contact George Hoare, Special Sales, at george_hoare@mcgraw-hill.com or (212)

904-4069.

TERMS OF USE

This is a copyrighted work and The McGraw-Hill Companies, Inc. (“McGraw-Hill”) and its licensors reserve all rights in and to the

work. Use of this work is subject to these terms. Except as permitted under the Copyright Act of 1976 and the right to store and

retrieve one copy of the work, you may not decompile, disassemble, reverse engineer, reproduce, modify, create derivative works

based upon, transmit, distribute, disseminate, sell, publish or sublicense the work or any part of it without McGraw-Hill’s prior

consent. You may use the work for your own noncommercial and personal use; any other use of the work is strictly prohibited. Your

right to use the work may be terminated if you fail to comply with these terms.

THE WORK IS PROVIDED “AS IS.” McGRAW-HILL AND ITS LICENSORS MAKE NO GUARANTEES OR WARRANTIES

AS TO THE ACCURACY, ADEQUACY OR COMPLETENESS OF OR RESULTS TO BE OBTAINED FROM USING THE

WORK, INCLUDING ANY INFORMATION THAT CAN BE ACCESSED THROUGH THE WORK VIA HYPERLINK OR

OTHERWISE, AND EXPRESSLY DISCLAIM ANY WARRANTY, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. McGraw-Hill

and its licensors do not warrant or guarantee that the functions contained in the work will meet your requirements or that its operation will be uninterrupted or error free. Neither McGraw-Hill nor its licensors shall be liable to you or anyone else for any

inaccuracy, error or omission, regardless of cause, in the work or for any damages resulting therefrom. McGraw-Hill has no

responsibility for the content of any information accessed through the work. Under no circumstances shall McGraw-Hill and/or its

licensors be liable for any indirect, incidental, special, punitive, consequential or similar damages that result from the use of or

inability to use the work, even if any of them has been advised of the possibility of such damages. This limitation of liability shall

apply to any claim or cause whatsoever whether such claim or cause arises in contract, tort or otherwise.

DOI: 10.1036/0071467343

Professional

Want to learn more?

We hope you enjoy this

McGraw-Hill eBook! If

you’d like more information about this book,

its author, or related books and websites,

please click here.

For more information about this title, click here

CONTENTS

List of Contributors

Preface xxiii

Part 1

xxi

Lead-Free Legislation

Chapter 1. Legislation and Impact on Printed Circuits

1.1

1.2

1.3

1.4

1.5

1.6

1.3

Legislation Overview / 1.3

Waste Electrical and Electronic Equipment (WEEE) / 1.3

Restriction of Hazardous Substances (RoHS) / 1.3

RoHS’ Impact on the Printed Circuit Industry / 1.6

Lead-Free perspecives / 1.10

Other Legislative Initiatives / 1.10

Part 2

Printed Circuit Technology Drivers

Chapter 2. ELECTRONIC PACKAGING AND HIGH-DENSITY

INTERCONNECTIVITY

2.3

2.1 Introduction / 2.3

2.2 Measuring the Interconnectivity Revolution (HDI) / 2.3

2.3 Hierarchy of Interconnections / 2.6

2.4 Factors Affecting Selection of Interconnections / 2.7

2.5 ICS and Packages / 2.10

2.6 Density Evaluations / 2.14

2.7 Methods to Increase PWB Density / 2.16

References / 2.21

Chapter 3. Semiconductor Packaging Technology

3.1

3.1 Introduction / 3.1

3.2 Single-Chip Packaging / 3.5

3.3 Multichip Packages / 3.15

3.4 Optical Interconnects / 3.18

3.5 High-Density/High-Performance Packaging Summary / 3.21

3.6 Roadmap Information / 3.21

References / 3.21

Chapter 4. Advanced Component Packaging

4.1

4.1 Introduction / 4.1

4.2 Lead-Free / 4.2

4.3 System-on-a-Chip (SOC) versus System-on-a-Package (SOP) / 4.3

v

vi

CONTENTS

4.4 Multichip Modules / 4.5

4.5 Multichip Packaging / 4.6

4.6 Enabling Technologies / 4.10

4.7 Acknowledgment / 4.18

References / 4.18

Chapter 5. Types of Printed Wiring Boards

5.1

5.1 Introduction / 5.1

5.2 Classification of Printed Wiring Boards / 5.1

5.3 Organic and Nonorganic Substrates / 5.3

5.4 Graphical and Discrete-Wire Boards / 5.3

5.5 Rigid and Flexible Boards / 5.5

5.6 Graphically Produced Boards / 5.6

5.7 Molded Interconnection Devices / 5.10

5.8 Plated-Through-Hole (PTH) Technologies / 5.10

5.9 Summary / 5.13

References / 5.14

Part 3

Materials

Chapter 6. Introduction to Base Materials

6.3

6.1 Introduction / 6.1

6.2 Grades and Specifications / 6.3

6.3 Properties Used to Classify Base Materials / 6.9

6.4 Types of FR-4 / 6.13

6.5 Laminate Identification Scheme / 6.14

6.6 Prepreg Identification Scheme / 6.18

6.7 Laminate and Prepreg Manufacturing Processes / 6.18

References / 6.24

Chapter 7. Base Material Components

7.1

7.1 Introduction / 7.1

7.2 Epoxy Resin Systems / 7.1

7.3 Other Resin Systems / 7.5

7.4 Additives / 7.7

7.5 Reinforcements / 7.12

7.6 Conductive Materials / 7.18

References / 7.25

Chapter 8. Properties of Base Materials

8.1

8.1 Introduction / 8.1

8.2 Thermal, Physical, and Mechanical Properties / 8.1

8.3 Electrical Properties / 8.13

References / 8.16

Chapter 9. Base Materials Performance Issues

9.1

9.2

9.3

9.4

9.5

Introduction / 9.1

Methods of Increasing Circuit Density / 9.2

Copper foil / 9.2

Laminate Constructions / 9.7

Prepreg Options and Yield-Per-Ply Values / 9.9

9.1

CONTENTS

vii

9.6 Dimensional Stability / 9.10

9.7 High-Density Interconnect/Microvia Materials / 9.13

9.8 CAF Growth / 9.15

9.9 Electrical Performance / 9.22

References / 9.33

Chapter 10. The Impact of Lead-Free Assembly on Base Materials

10.1

10.1 Introduction / 10.1

10.2 RoHS Basics / 10.1

10.3 Base Material Compatibility Issues / 10.2

10.4 The Impact of Lead-Free Assembly on Base Material Components / 10.4

10.5 Critical Base Material Properties / 10.4

10.6 Impact on Printed Circuit Reliability and Material Selection / 10.18

10.7 Summary / 10.21

References / 10.22

Chapter 11. Selecting Base Materials for Lead-Free Assembly Applications

11.1

11.1 Introduction / 11.1

11.2 Pcb fabrication and Assembly Interactions / 11.1

11.3 Selecting the Right Base Material for Specific Application / 11.6

11.4 Example Application of this Tool / 11.14

11.5 Discussion of the Range of Peak Temperatures for Lead-Free Assembly / 11.15

11.6 Lead-Free Applications and Ipc-4101 Specification Sheets / 11.15

11.7 Additional Base material Options for Lead-Free Applications / 11.16

11.8 Summary / 11.17

References / 11.18

Chapter 12. Laminate Qualification and Testing

12.1

12.2

12.3

12.4

12.5

12.6

12.7

Introduction / 12.1

Industry Standards / 12.2

Laminate Test Strategy / 12.4

Initial Tests / 12.5

Full Material Characterization / 12.9

Characterization Test Plan / 12.22

Manufacturability in the Shop / 12.23

Part 4

Engineering and Design

Chapter 13. Physical Characteristics of the PCB

13.1

13.2

13.3

13.4

13.5

13.6

13.7

12.1

13.3

Classes of PCB Designs / 13.3

Types of PCBs or Packages for Electronic Circuits / 13.9

Methods of Attaching Components / 13.14

Component Package Types / 13.15

Materials Choices / 13.18

Fabrication Methods / 13.22

Choosing a Package Type and Fabrication Vendor / 13.24

Chapter 14. The PCB Design Process

14.1 Objective of the PCB Design Process / 14.1

14.2 Design Processes / 14.1

14.1

viii

CONTENTS

14.3

14.4

14.5

14.6

Design Tools / 14.6

Selecting a Set of Design Tools / 14.10

Interfacing Cae, Cad, and CAM Tools to Each Other / 14.11

Inputs to the Design Process / 14.11

Chapter 15. Electrical and Mechanical Design Parameters

15.1

15.1 Printed Circuit Design Requirements / 15.1

15.2 Introduction to Electrical Signal Integrity / 15.1

15.3 Introduction to Electromagnetic Compatibility / 15.3

15.4 Noise Budget / 15.4

15.5 Designing for Signal Integrity and Electromagnetic Compatibility / 15.4

15.6 Mechanical Design Requirements / 15.9

References / 15.17

Chapter 16. Current Carrying Capacity in Printed Circuits

16.1

16.1 Introduction / 16.1

16.2 Conductor (Trace) Sizing Charts / 16.1

16.3 Current Carrying Capacity / 16.2

16.4 Charts / 16.6

16.5 Baseline Charts / 16.10

16.6 Odd-Shaped Geometries and the “Swiss Cheese” Effect / 16.19

16.7 Copper Thickness / 16.20

References / 16.21

Chapter 17. PCB Design for Thermal Performance

17.1

17.1 Introduction / 17.1

17.2 The PCB as a Heat Sink Soldered to the Component / 17.2

17.3 Optimizing the PCB for Thermal Performance / 17.3

17.4 Conducting Heat to the Chassis / 17.12

17.5 PCB Requirements for High-Power Heat Sink Attach / 17.14

17.6 Modeling the Thermal Performance of the PCB / 17.15

References / 17.18

Chapter 18. Information Formating and Exchange

18.1

18.1 Introduction to Data Exchange / 18.1

18.2 The Data Exchange Process / 18.3

18.3 Data Exchange Formats / 18.9

18.4 Drivers for Evolution / 18.22

18.5 Acknowledgment / 18.23

References / 18.23

Chapter 19. Planning for Design, Fabrication, and Assembly

19.1 Introduction / 19.1

19.2 General Considerations / 19.3

19.3 New Product Design / 19.4

19.4 Layout Trade-off Planning / 19.10

19.5 PWB Fabrication Trade-off Planning / 19.17

19.6 Assembly Trade-Off Planning / 19.24

References / 19.27

19.1

CONTENTS

Chapter 20. Manufacturing Information, Documentation,

and Transfer Including CAM Tooling for Fab and Assembly

20.1

20.2

20.3

20.4

20.5

20.6

20.7

20.8

20.1

Introduction / 20.1

Manufacturing Information / 20.2

Initial Design Review / 20.7

Design Input / 20.15

Design Analysis and Review / 20.19

The CAM-Tooling Process / 20.19

Additional Processes / 20.31

Acknowledgment / 20.32

Chapter 21. Embedded Components

21.1

21.2

21.3

21.4

21.5

21.6

ix

21.1

Introduction / 21.1

Definitions and Example / 21.1

Applications and Trade-Offs / 21.2

Designing for Embedded Component Applications / 21.3

Materials / 21.6

Material Supply Types / 21.9

Part 5

High Density Interconnection

Chapter 22. Introduction to High-Density Interconnection (HDI) Technology

22.3

22.1 Introduction / 22.3

22.2 Definitions / 22.3

22.3 HDI Structures / 22.7

22.4 Design / 22.11

22.5 Dielectric Materials and Coating Methods / 22.13

22.6 HDI Manufacturing Processes / 22.26

References / 22.34

Bibliography-Additional Reading / 22.35

Chapter 23. Advanced High-Density Interconnection (HDI) Technologies

23.1

23.1 Introduction / 23.1

23.2 Definitions of HDI Process Factors / 23.1

23.3 HDI Fabrication Processes / 23.3

23.4 Next-Generation HDI Processes / 23.33

References

23.37

Part 6

Fabrication

Chapter 24. Drilling Processes

24.1

24.2

24.3

24.4

24.5

24.6

24.7

Introduction / 24.3

Materials / 24.4

Machines / 24.11

Methods / 24.15

Hole Quality / 24.18

Postdrilling Inspection / 24.20

Drilling Cost Per Hole / 24.20

24.3

x

CONTENTS

Chapter 25. Precision Interconnect Drilling

25.1

25.2

25.3

25.4

25.5

25.6

25.7

25.1

Introduction / 25.1

Factors Affecting High-Density Drilling / 25.1

Laser versus Mechanical / 25.2

Factors Affecting High-Density Drilling / 25.5

Depth-Controlled Drilling Methods / 25.10

High-Aspect-Ratio Drilling / 25.10

Innerlayer Inspection of Multilayer Boards / 25.13

Chapter 26. Imaging

26.1

26.1 Introduction / 26.1

26.2 Photosensitive Materials / 26.2

26.3 Dry-Film Resists / 26.4

26.4 Liquid Photoresists / 26.7

26.5 Electrophoretic Depositable Photoresists / 26.8

26.6 Resist Processing / 26.8

26.7 Design for Manufacturing / 26.27

References / 26.29

Chapter 27. Multilayer Materials and Processing

27.1

27.1 Introduction / 27.1

27.2 Printed Wiring Board Materials / 27.2

27.3 Multilayer Construction Types / 27.16

27.4 ML-PWB Processing and Flows / 27.37

27.5 Lamination Process / 27.51

27.6 Lamination Process Control and Troubleshooting / 27.59

27.7 Lamination Overview / 27.63

27.8 ML-PWB Summary / 27.63

References / 27.63

Chapter 28. Preparing Boards for Plating

28.1

28.1 Introduction / 28.1

28.2 Process Decisions / 28.1

28.3 Process Feedwater / 28.3

28.4 Multilayer PTH Preprocessing / 28.4

28.5 Electroless Copper / 28.8

28.6 Acknowledgment / 28.11

References / 28.11

Chapter 29. Electroplating

29.1

29.2

29.3

29.4

29.5

29.6

29.7

29.8

29.9

29.10

29.11

29.12

Introduction / 29.1

Electroplating Basics / 29.1

High-Aspect Ratio Hole and Microvia Plating / 29.2

Horizontal Electroplating / 29.4

Copper Electroplating General Issues / 29.6

Acid Copper Sulfate Solutions and Operation / 29.14

Solder (Tin-Lead) Electroplating / 29.19

Tin Electroplating / 29.21

Nickel Electroplating / 29.23

Gold Electroplating / 29.25

Platinum Metals / 29.28

Silver Electroplating / 29.29

29.1

CONTENTS

xi

29.13 Laboratory Process control / 29.29

29.14 Acknowledgment / 29.31

References / 29.31

Chapter 30. Direct Plating

30.1

30.1 Direct Metallization Technology / 30.1

References / 30.11

Chapter 31. PWB Manufacture Using Fully Electroless Copper

31.1

31.1 Fully Electroless Plating / 31.1

31.2 The Additive Process and its Variations / 31.2

31.3 Pattern-Plating Additive / 31.2

31.4 Panel-Plate Additive / 31.7

31.5 Partly Additive / 31.8

31.6 Chemistry of Electroless Plating / 31.9

31.7 Fully Electroless Plating Issues / 31.12

References / 31.14

Chapter 32. Printed Circuit Board Surface Finishes

32.1

32.1 Introduction / 32.1

32.2 Alternative Finishes / 32.3

32.3 Hot Air Solder Level (Hasl or Hal) / 32.4

32.4 Electroless Nickel Immersion Gold (ENIG) / 32.6

32.5 Organic Solderability Preservative (OSP) / 32.8

32.6 Immersion Silver / 32.10

32.7 Immersion Tin / 32.11

32.8 Other Surface Finishes / 32.13

32.9 Assembly Compatibility / 32.14

32.10 Reliability Test Methods / 32.17

32.11 Special Topics / 32.18

32.12 Failure Modes / 32.19

32.13 Comparing Surface Finish Properties / 32.23

References / 32.23

Chapter 33. Solder Mask

33.1

33.2

33.3

33.4

33.5

33.6

33.7

33.8

Introduction / 33.1

Trends and Challenges for Solder Mask / 33.2

Types of Solder Mask / 33.3

Solder Mask Selection / 33.4

Solder Mask Application and Processing / 33.9

VIA Protection / 33.18

Solder Mask Final Properties / 33.19

Legend and Marking (Nomenclature) / 33.19

Chapter 34. Etching Process and Technologies

34.1

34.2

34.3

34.4

34.5

34.6

34.7

33.1

Introduction / 34.1

General Etching Considerations and Procedures / 34.2

Resist Removal / 34.4

Etching Solutions / 34.6

Other Materials for Board Construction / 34.18

Metals Other than Copper / 34.19

Basics of Etched Line Formation / 34.20

34.1

xii

CONTENTS

34.8 Equipment and Techniques / 34.26

References / 34.29

Chapter 35. Machining and Routing

35.1

35.2

35.3

35.4

35.5

35.6

Introduction / 35.1

Punching Holes (Piercing) / 35.1

Blanking, Shearing, and Cutting of Copper-Clad Laminates / 35.3

Routing / 35.6

Scoring / 35.13

Acknowledgment / 35.15

Part 7

Bare Board Test

Chapter 36. Bare Board Test Objectives and Definitions

36.1

36.2

36.3

36.4

38.1

Introduction / 38.1

System Alternatives / 38.1

Universal Grid Systems / 38.3

Flying-Probe/Moving-Probe Test Systems / 38.17

Verification and Repair / 38.21

Test Department Planning and Management / 38.22

Chapter 39. HDI Bare Board Special Testing Methods

39.1

39.2

39.3

39.4

39.5

39.6

39.7

39.8

39.9

39.10

37.1

Introduction / 37.1

Nonelectrical Testing Methods / 37.1

Basic Electrical Testing Methods / 37.2

Specialized Electrical Testing Methods / 37.9

Data and Fixture Preparation / 37.13

Combined Testing Methods / 37.20

Chapter 38. Bare Board Test Equipment

38.1

38.2

38.3

38.4

38.5

38.6

36.3

Introduction / 36.3

The Impact of HDI / 36.3

Why Test? / 36.4

Circuit Board Faults / 36.6

Chapter 37. Bare Board Test Methods

37.1

37.2

37.3

37.4

37.5

37.6

35.1

Introduction / 39.1

Fine-Pitch Tilt-Pin Fixtures / 39.2

Bending Beam Fixtures / 39.3

Flying Probe / 39.3

Coupled Plate / 39.3

Shorting Plate / 39.4

Conductive Rubber Fixtures / 39.5

Optical Inspection / 39.5

Noncontact Test Methods / 39.5

Combinational Test Methods / 39.7

39.1

CONTENTS

Part 8

Assembly

Chapter 40. Assembly Processes

40.1

40.2

40.3

40.4

40.5

40.6

40.7

40.8

40.9

xiii

40.3

Introduction / 40.3

Through-Hole Technology / 40.5

Surface-Mount Technology / 40.16

Odd-Form Component Assembly / 40.42

Process Control / 40.48

Process Equipment Selection / 40.54

Repair and Rework / 40.57

Conformal Coating, Encapsulation, and Underfill Materials / 40.64

Acknowledgment / 40.66

Chapter 41. Conformal Coating

41.1

41.1 Introduction / 41.1

41.2 Types of Conformal Coatings / 41.3

41.3 Product Preparation / 41.6

41.4 Application Processes / 41.7

41.5 Cure, Inspection, and Finishing / 41.11

41.6 Repair Methods / 41.13

41.7 Design for Conformal Coating / 41.14

References / 41.17

Part 9

Solderability Technology

Chapter 42. Solderability: Incoming Inspection and Wet Balance Technique

42.1

42.2

42.3

42.4

42.5

42.6

42.7

42.8

42.3

Introduction / 42.3

Solderability / 42.4

Solderability Testing—a Scientific Approach / 42.8

The Influence of Temperature on Test Results / 42.13

Interpreting the Results: Wetting Balance Solderability Testing / 42.14

Globule Testing / 42.15

PCB Surface Finishes and Solderability Testing / 42.16

Component Solderability / 42.22

Chapter 43. Fluxes and Cleaning

43.1 Introduction / 43.1

43.2 Assembly Process / 43.2

43.3 Surface Finishes / 43.3

43.4 Soldering Flux / 43.5

43.5 Flux Form Versus Soldering Process / 43.6

43.6 Rosin Flux / 43.7

43.7 Water-Soluble Flux / 43.8

43.8 Low Solids Flux / 43.9

43.9 Cleaning Issues / 43.10

43.10 Summary / 43.12

References / 43.12

43.1

xiv

CONTENTS

Part 10

Solder Materials and Processes

Chapter 44. Soldering Fundamentals

44.1

44.2

44.3

44.4

44.5

44.6

44.7

44.3

Introduction / 44.3

Elements of a Solder Joint / 44.4

The Solder Connection to the Circuit Board / 44.4

The solder Connection to the Electrical Component / 44.5

Common Metal-Joining Methods / 44.5

Solder Overview / 44.9

Soldering Basics / 44.9

Chapter 45. Soldering Materials and Metallurgy

45.1

45.1 Introduction / 45.1

45.2 Solders / 45.2

45.3 Solder Alloys and Corrosion / 45.4

45.4 PB-Free Solders: Search for Alternatives and Implications / 45.5

45.5 PB-Free Elemental Alloy Candidates / 45.5

45.6 Board Surface Finishes / 45.11

References / 45.19

Chapter 46. Solder Fluxes

46.1

46.1 Introduction to Fluxes / 46.1

46.2 Flux Activity and Attributes / 46.2

46.3 Flux: Ideal Versus Reality / 46.3

46.4 Flux Types / 46.4

46.5 Water-Clean (Aqueous) Fluxes / 46.4

46.6 No-Clean Flux / 46.7

46.7 Other Fluxing Caveats / 46.9

46.8 Soldering Atmospheres / 46.12

References / 46.15

Chapter 47. Soldering Techniques

47.1

47.1 Introduction / 47.1

47.2 Mass Soldering Methods / 47.1

47.3 Oven Reflow Soldering / 47.1

47.4 Wave Soldering / 47.28

47.5 Wave Solder Defects / 47.39

47.6 Vapor-Phase Reflow Soldering / 47.42

47.7 Laser Reflow Soldering / 47.43

47.8 Tooling and the Need for Coplanarity and Intimate Contact / 47.50

47.9 Additional Information Sources / 47.53

47.10 Hot-Bar Soldering / 47.53

47.11 Hot-Gas Soldering / 47.58

47.12 Ultrasonic Soldering / 47.59

References / 47.61

Chapter 48. Soldering Repair and Rework

48.1 Introduction / 48.1

48.2 Hot-Gas Repair / 48.1

48.1

CONTENTS

xv

48.3 Manual Solder Fountain / 48.5

48.4 Automated Solder Fountain / 48.6

48.5 Laser / 48.6

48.6 Considerations for Repair / 48.6

Reference / 48.7

Part 11

Nonsolder Interconnection

Chapter 49. Press-Fit Interconnection

49.3

49.1 Introduction / 49.3

49.2 The Rise of Press-Fit Technology / 49.3

49.3 Compliant Pin Configurations / 49.4

49.4 Press-Fit Considerations / 49.6

49.5 Press-Fit Pin Materials / 49.7

49.6 Surface Finishes and Effects / 49.8

49.7 Equipment / 49.10

49.8 Assembly Process / 49.11

49.9 Press Routines / 49.12

49.10 PWB Design and Board Procurement Tips / 49.14

49.11 Press-Fit Process Tips / 49.15

49.12 Inspection and Testing / 49.16

49.13 Soldering and Press-Fit Pins / 49.17

References / 49.17

Chapter 50. Land Grid Array Interconnect

50.1

50.1 Introduction / 50.1

50.2 LGA and the Environment / 50.1

50.3 Elements of the LGA System / 50.2

50.4 Assembly / 50.5

50.5 Printed Circuit Assembly (PCA) Rework / 50.7

50.6 Design Guidelines / 50.8

Reference / 50.8

Part 12 Quality

Chapter 51. Acceptability and Quality of Fabricated Boards

51.1

51.2

51.3

51.4

51.5

51.6

51.7

51.8

51.9

51.10

51.11

51.12

Introduction / 51.3

Specific Quality and Acceptability Criteria by PCB Type / 51.4

Methods for Verification of Acceptability / 51.6

Inspection Lot Formation / 51.7

Inspections Categories / 51.8

Acceptability and Quality After Simulated Solder Cycle(s) / 51.8

Nonconforming PCBS and Material Review Board (MRB) Function / 51.10

The Cost of the Assembled PCB / 51.11

How to Develop Acceptability and Quality Criteria / 51.11

Class of Service / 51.13

Inspection Criteria / 51.13

Reliability Inspection Using Accelerated Environmental Exposure / 51.32

51.3

xvi

CONTENTS

Chapter 52. Acceptability of Printed Circuit Board Assemblies

52.1

52.1 Understanding Customer Requirements / 52.1

52.2 Handling to Protect the PCBA / 52.7

52.3 PCBA Hardware Acceptability Considerations / 52.10

52.4 Component Installation or Placement Requirements / 52.15

52.5 Component and PCB Solderability Requirements / 52.25

52.6 Solder-Related Defects / 52.25

52.7 PCBA Laminate Condition, Cleanliness, and Marking Requirements / 52.32

52.8 PCBA Coatings / 52.34

52.9 Solderless Wrapping of Wire to Posts (Wire Wrap) / 52.35

52.10 PCBA Modifications / 52.37

References / 52.39

Chapter 53. Assembly Inspection

53.1

53.1 Introduction / 53.1

53.2 Definition of Defects, Faults, Process Indicators, and Potential Defects / 53.3

53.3 Reasons for Inspection / 53.4

53.4 Lead-Free Impact on Inspection / 53.6

53.5 Miniaturization and Higher Complexity / 53.8

53.6 Visual Inspection / 53.8

53.7 Automated Inspection / 53.12

53.8 Three-Dimensional Automated Solder Paste Inspection / 53.14

53.9 PRE-Reflow Aoi / 53.16

53.10 Post-Reflow Automated Inspection / 53.17

53.11 Implementation of Inspection Systems / 53.23

53.12 Design Implications of Inspection Systems / 53.24

References / 53.25

Chapter 54. Design for Testing

54.1

54.1 Introduction / 54.1

54.2 Definitions / 54.2

54.3 AD HOC Design for Testability / 54.2

54.4 Structured Design for Testability / 54.4

54.5 Standards-Based Testing / 54.5

References / 54.12

Chapter 55. Loaded Board Testing

55.1

55.1 Introduction / 55.1

55.2 The process of Test / 55.1

55.3 Definitions / 55.4

55.4 Testing Approaches / 55.7

55.5 In-Circuit Test Techniques / 55.11

55.6 Alternatives to Conventional Electrical Tests / 55.17

55.7 Tester Comparison / 55.19

References / 55.20

Part 13

Reliability

Chapter 56. Conductive Anodic Filament Formation

56.1 Introduction / 56.3

56.2 Understanding CAF Formation / 56.3

56.3

CONTENTS

xvii

56.3 Electrochemical Migration and Formation of CAF / 56.7

56.4 Factors that Affect CAF Formation / 56.10

56.5 Test Method for CAF-Resistant Materials / 56.14

56.6 Manufacturing Tolerance Considerations / 56.14

References / 56.15

Chapter 57. Reliability of Printed Circuit Assemblies

57.1

57.1 Fundamentals of Reliability / 57.2

57.2 Failure Mechanisms of PCBS and Their Interconnects / 57.4

57.3 Influence of Design on Reliability / 57.19

57.4 Impact of PCB Fabrication and Assembly on Reliability / 57.20

57.5 Influence of Materials Selection on Reliability / 57.27

57.6 Burn-in, Acceptance Testing, and Accelerated Reliability Testing / 57.36

57.7 Summary / 57.45

References / 57.45

Further Reading / 57.47

Chapter 58. Component-to-PWB Reliability: The Impact of Design

Variables and Lead Free

58.1

58.1 Introduction / 58.1

58.2 Packaging Challenges / 58.2

58.3 Variables that Impact Reliability / 58.5

References / 58.30

Chapter 59. Component-to-PWB Reliability: Estimating Solder-Joint

Reliability and the Impact of Lead-Free Solders

59.1

59.1 Introduction / 59.1

59.2 Thermomechanical Reliability / 59.3

59.3 Mechanical Reliability / 59.20

59.4 Finite Element Analysis (FEA) / 59.27

References / 59.35

Part 14

Environmental Issues

Chapter 60. Process Waste Minimization and Treatment

60.1 Introduction / 60.3

60.2 Regulatory Compliance / 60.3

60.3 Major Sources and Amounts of Wastewater

in a Printed Circuit Board Fabrication Facility / 60.5

60.4 Waste Minimization / 60.6

60.5 Pollution Prevention Techniques / 60.8

60.6 Recycling and Recovery Techniques / 60.15

60.7 Alternative Treatments / 60.18

60.8 Chemical Treatment Systems / 60.21

60.9 Advantages and Disadvantages of Various Treatment Alternatives / 60.26

60.3

xviii

CONTENTS

Part 15

Flexible Circuits

Chapter 61. Flexible Circuit Applications and Materials

61.1

61.2

61.3

61.4

61.5

61.6

61.7

61.8

61.9

61.10

61.11

Introduction to Flexible Circuits / 61.3

Applications of Flexible Circuits / 61.6

High-Density Flexible Circuits / 61.6

Materials for Flexible Circuits / 61.8

Substrate Material Properties / 61.9

Conductor Materials / 61.13

Copper-Clad Laminates / 61.14

Coverlay Material / 61.19

Stiffener Materials / 61.22

Adhesive materials / 61.22

Restriction of Hazardous Substances

(RoHS) Issues / 61.23

Chapter 62. Design of Flexible Circuits

62.1

62.2

62.3

62.4

62.5

62.6

62.7

63.1

Introduction / 63.1

Special Issues with HDI Flexible Circuits / 63.1

Basic Process Elements / 63.3

New Processes for Fine Traces / 63.14

Coverlay Processes / 63.24

Surface Treatment / 63.30

Blanking / 63.31

Stiffener Processes / 63.33

Packaging / 63.33

Roll-to-Roll Manufacturing / 63.34

Dimension Control / 63.36

Chapter 64. Termination of Flexible Circuits

64.1

64.2

64.3

64.4

64.5

64.6

62.1

Introduction / 62.1

Design Procedure / 62.1

Types of Flexible Circuits / 62.2

Circuit Designs for Flexibility / 62.12

Electrical Design of the Circuits / 62.15

Circuit Designs for Higher Reliability / 62.16

Circuit Designs for RoHS Compliance / 62.17

Chapter 63. Manufacturing of Flexible Circuits

63.1

63.2

63.3

63.4

63.5

63.6

63.7

63.8

63.9

63.10

63.11

61.3

64.1

Introduction / 64.1

Selection of Termination Technologies / 64.1

Permanent Connections / 64.4

Semipermanent Connections / 64.11

Nonpermanent Connections / 64.13

High-Density Flexible Circuit Termination / 64.20

Chapter 65. Multilayer Flex and Rigid/Flex

65.1 Introduction / 65.1

65.2 Multilayer Rigid/flex / 65.1

65.1

CONTENTS

Chapter 66. Special Constructions of Flexible Circuits

66.1

66.2

66.3

66.4

66.5

66.6

66.7

66.1

Introduction / 66.1

Flying-Lead Construction / 66.1

Tape Automated Bonding / 66.8

Microbump Arrays / 66.10

Thick-Film Conductor Flex Circuits / 66.12

Shielding of the Flexible Cables / 66.13

Functional Flexible Circuits / 66.14

Chapter 67. Quality Assurance of Flexible Circuits

67.1

67.2

67.3

67.4

67.5

67.6

67.7

67.8

67.9

xix

Introduction / 67.1

Basic Concepts in Flexible Circuit Quality Assurance / 67.1

Automatic Optical Inspection Systems / 67.2

Dimensional Measurements / 67.3

Electrical Tests / 67.3

Inspection Sequence / 67.3

Raw Materials / 67.6

Flexible Circuit Feature Inspection / 67.6

Standards and Specifications for Flexible Circuits / 67.8

Appendix A.1

Glossary G.1

Index I.1

67.1

This page intentionally left blank

LIST OF CONTRIBUTORS

Cisco Systems, San Jose, CA, (CHAPS. 58, 59)

Mudasir Ahmad

University of Arkansas, Fayetteville, AR (CHAP. 4)

Simon Ang

Avery Environmental Services, Saratoga, CA (CHAP. 60)

Joyce M. Avery

David W. Bergman IPC, Bannockburn, IL (APPENDIX)

Mark Brillhart

Palo Alto, CA (CHAPS. 58, 59)

William Brown

University of Arkansas, Fayetteville, AR (CHAP. 4)

Jody Byrum Lockheed Martin, Newtown, PA (CHAP. 41)

Brian F. Conaghan Parelec, Rocky Hill, NJ (CHAP. 26)

Don Cullen MacDermid Inc., Waterbury, CT (CHAP. 32)

Lockheed Martin, Dallas,TX (CHAP. 27)

C. D. Dupriest

Darvin Edwards

Texas Instruments, Dallas, TX (CHAP. 17)

Sylvia Ehrler

Feinmetall, GmbH, Herrenberg, Germany (CHAP. 12)

Bini Elhanan

Valor Computerized Systems Inc., Yavne, Israel (CHAP. 18)

Hewlett-Packard Co, Singapore (CHAPS. 1, 44–50)

Gary M. Freedman

MacDermid Inc., Waterbury, CT (CHAP. 21)

Dennis Fritz

Hewlett-Packard, Palo Alto, CA (CHAP. 57)

Judith Glazer

Marshall Gurian Consulting,Tempe, AZ (CHAP. 34)

Marshall I. Gurian

Terry Haney

Excellon Automation Co., Rancho Dominquez, CA (CHAP. 25)

Ralph J. Hersey, Jr. Lawrence Livermore National Laboratory, Livermore, CA (CHAP. 15)

Mentor Graphics, Longmont, CO (CHAPS. 2, 19, 20, 22, 23)

Happy T. Holden

Stacy Kalisz Johnson

Mike Jouppi

Agilent Technologies, Gilbert AZ (CHAP. 53)

Thermal Management Inc., Centennial, CO (CHAP. 16)

Edward J. Kelley

Isola Group, Chandler, AZ (CHAPS. 6–11)

Peter G. Moleux

Peter Moleux and Associates, Newton Centre, MA (CHAP. 60)

Kester, Itasca, IL (CHAP. 43)

Gregory C. Munie

Hayao Nakahara N.T. Information, Huntington, NY (CHAPS. 5, 30, 31)

Robert (Bob) Neves

Microtek Laboratories, Anaheim, CA and Changzhou, China (CHAP. 51)

Dominique K. Numakura

Gerard O’Brien

Stig Oresjo

DKN Research, Haverhill, MA (CHAPS. 61–67)

S.T. and S. Company, Bayport, NY (CHAP. 42)

Agilent Technologies, Loveland, CO (CHAP. 53)

Kenneth P. Parker

Agilent Technologies, Loveland, CO (CHAPS. 54, 55)

xxi

Copyright © 2008 by The McGraw-Hill Companies. Click here for terms of use.

xxii

LIST OF CONTRIBUTORS

Mel Parrish STI Electronics Inc., Madison AL (CHAP. 52)

Tarak A. Railkar Texas Instruments, Dallas, TX (CHAP. 4)

Lee W. Ritchey

3Com, Santa Clara, CA (CHAPS. 13, 14)

Hewlett-Packard Co., Palo Alto, CA (CHAP. 12)

Michael Roesch

Gary Roper One Source Group, Dallas, TX (CHAP. 35)

JWS Consulting PLC, Phoenix, AZ (CHAP. 3)

John W. Stafford

Valerie St. Cyr

Teradyne Inc., North Reading, PA (CHAP. 27)

University of Toronto, Canada (CHAP. 43, 56)

Laura J. Turbini

Hans Vandervelde

Laminating Company of America (LCOA), Garden Grove, CA (CHAP. 24)

David A. Vahghan

Taiyo America Inc., Carson City, NV (CHAP. 33)

Paul T. Vianco

Sandia National Laboratories, Albuquerque, NM (CHAP. 40)

Jim Watkowski

Mac Dermid Inc., Waterbury, CT (CHAP. 28, 29)

David J. Wilkie

Everett Charles Technologies, Pomona, CA (CHAPS. 36–39)

PREFACE

With the implementation of the European Union (EU) directive on Restriction of Hazardous

Substances (RoHS), the printed circuit industry has been forced to undergo a revolution in

technology that is unprecedented in its history. The result is commonly called lead-free, a term

that the reader will find used throughout this book, even though the restrictions are on several materials in addition to lead, as described in Chapter 1. The reason for this emphasis is

that the biggest impact on the industry is the elimination of lead in the solder that is used for

interconnection of the components and the board.

These changes are not driven by demands from the marketplace or the advancement of

technology; rather, they have been legislated for reasons perceived to benefit society in general. Although the net effect, either positive or negative, on the global environment of elimination of lead in printed circuit assemblies has been the source of great debate, the reality is

that it has been adopted worldwide and is a fact of life for all those who design, fabricate, and

assemble printed circuits.

Tin-lead solder has been the basis for interconnections since the beginning of the use of

printed circuits, and all associated materials and processes have been developed with the use of

that material in mind. As a result, the abrupt shift to new solder alloys poses many questions

about the related or affected processes and technologies that must now adapt and change to

meet the lead-free requirements. Past experience or previous literature cannot be relied on to

provide answers to these questions. The purpose of this book is to provide this information as

specifically and in as much detail as possible, using industry standards, where they exist, or best

practice that has a sound technical foundation and has been shown to work.

The most obvious change is in the metallurgy of the solder and in mating surfaces. However, all alternative solder alloys melt at a higher temperature than eutectic solder, and this

has required new base materials, new assembly processes, as well as new test, inspection, and

reliability criteria and methods. With specific regard to the lead-free alternative alloys, we

start with the periodic table of elements and describe what elements are candidates for use,

and what the effect each has when incorporated into an alloy. Thus we rely on physics and

material science to help define the appropriate alternative for a given application. Similarly,

to help the reader choose the best base material for the higher assembly and operating temperatures and higher component speeds, we describe the chemistry of the material.

The issues of defining and predicting reliability of products in this new situation have

absorbed a great deal of corporate resources since the EU directive was announced. The predictive models and history were based on tin-lead alloys, and new models are needed for leadfree alloys. For this edition, we have added new material and expanded existing discussions on

this subject.

Although the lead-free technology revolution has gotten much more attention, there have

also been important evolutionary changes in the technology as the industry continues to meet

the need for higher circuit and component density and faster circuits. As a result, printed circuit boards continue to be designed to be ever smaller, or larger, to suit the requirements of

specific applications. This book updates the reader on these advancements. In addition, with

the continuing global nature of the printed circuit industry, along with the constant pressure to

decrease both time to market and time to volume, there is a growing need for international

standards covering layout and design information and communications that enable each organizational element in the supply chain to function effectively with minimum manual intervention and delays for design clarification. For the first time, we have added chapters that describe

xxiii

Copyright © 2008 by The McGraw-Hill Companies. Click here for terms of use.

xxiv

PREFACE

these parts of the overall process. In addition, we have introduced discussions on embedded

components and conformal coatings, both important issues in many applications of the

technology.

This edition addresses these new elements of the printed circuit processes, both revolutionary and evolutionary, while still maintaining its foundation on the basics of the technology. No

matter how sophisticated the leading edge of the technology becomes, at the core of all

printed circuits is the plated-through hole in its various forms. This remains one of the most

important technical achievements of the twentieth century. Although based on the platedthrough hole, printed circuits technology has evolved over the years to be more reliable, efficient, and reproducible, but the process described in the first edition of this book is still

recognizable in the sixth. As a result, those new to the technology will still find introductory

information, while experienced practitioners will find industry standard methods and best

practices to help them with the most recent developments.

As the industry has grown, it has become more specialized. This has created the need to

standardize documentation and communication techniques as well as to understand the specific capabilities of all suppliers in the overall value delivery chain. The result is that process

capabilities and limitations at each step must be known, the board must be designed with these

clearly in mind, and consistent acceptability criteria must be agreed to in advance, before the

responsibility for the board passes from designer to fabricator to assembler to end user. This

has created a community of people who have not been intimately involved in printed circuit

issues before, and who now find a working knowledge of printed circuits critical for performance in their jobs. This book provides information for these people as well. They not only will

find the basic information useful in understanding the issues, but also find specific guidelines

on the development and management of the value chain for the success of all.

Although the industry’s preferred term for the subject of this book is printed wiring or

etched wiring, the term printed circuits has passed into the world’s languages as representing

the process and products described. As a result, we will use the terms interchangeably.

The impact of all these changes in the printed circuit technology is reflected in this book,

as over 75 percent of the chapters are either revised or new to this edition. That means that

this sixth edition contains the most new information since the first edition.

The continuing cooperation and support of the leadership and staff of the IPC-Association

Connecting Electronic Industries (IPC) are acknowledged, not just for this edition, but for all

the previous editions. IPC, under the leadership of Ray Pritchard, now retired, and Dieter

Bergman, celebrated its 50th anniversary in 2007, and it would be impossible to overemphasize the contribution it has made, not just to the electronics industry but to a world that

increasingly relies on electronic products. Special appreciation goes to Jack Crawford for the

help in identifying and providing IPC material critical for the preparation of this edition.

Finally, I want to acknowledge and thank the authors, who have given so liberally of their

time and skill in preparing the chapters for this book. They have made a great contribution to

the literature and to the industry.

Clyde F. Coombs, Jr.

Editor-in-Chief

P

●

A

●

R

●

T

●

1

LEAD-FREE LEGISLATION

Copyright © 2008 by The McGraw-Hill Companies. Click here for terms of use.

This page intentionally left blank

CHAPTER 1

LEGISLATION AND IMPACT

ON PRINTED CIRCUITS

Gary M. Freedman

Hewlett-Packard Corporation, Business Critical Systems, Singapore

1.1 LEGISLATION OVERVIEW

The dramatic rise in output and rapid obsolescence of consumer and commercial electronic

goods has prompted the European Union (EU) to draft two pieces of environmental legislation that impact the electronics industry:

●

●

Directive 2002-96-EC 27 Jan 2003 of the European Parliament and of the Council on Waste

Electrical & Electronic Equipment, commonly abbreviated as WEEE.

Directive 2002-95-EC of the European Parliament and of the Council 27 Jan 2003, which

restricts the use of certain hazardous substances in electrical and electronic equipment.This

directive is also known as RoHS (Restriction of Hazardous Substances).

1.2 WASTE ELECTRICAL AND ELECTRONIC EQUIPMENT (WEEE)

This European Community Directive was fully effective in August 2005. It requires manufacturers selling electrical or electronic equipment to member countries of the European

Union to be responsible for end-of-life disposal of their finished goods.The directive attempts

to limit the stream of waste materials to landfills, encourage recycling, and pressure equipment designs and materials to be more environmentally friendly.The end results are tariffs for

purchasing electronic products to help with disposal costs and encouraging electronic manufacturers to institute take-back programs for recycling. The list of affected goods is very long.

Table 1.1 includes examples of affected products.

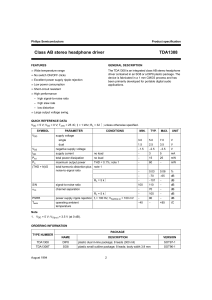

The directive also mandates that the symbol shown in Fig. 1.1 be placed conspicuously on

products signifying separate collection for disposal.

1.3 RESTRICTION OF HAZARDOUS SUBSTANCES (RoHS)

The second piece of legislation has the biggest impact on the electronics industry. The RoHS

directive makes it illegal to manufacture or import into the member states of the EU any electrical or electronic equipment that contains restricted materials––materials that have been the

1.3

Copyright © 2008 by The McGraw-Hill Companies. Click here for terms of use.

1.4

PRINTED CIRCUITS HANDBOOK

TABLE 1.1 Examples of Products Affected by the WEEE Directive

Category

Examples

Large household appliances

Small household appliances

IT and telecommunications

equipment

Consumer equipment

Lighting equipment

Electrical and electronic

tools

Washers, dryers, refrigerators, freezers, microwave ovens, air conditioners, etc.

Vacuum cleaners, toasters, irons, clocks, hair dryers, etc.

Computers, printers, monitors, copying equipment, calculators, data storage

equipment, projectors, telephones, etc.

Radios, televisions, cameras, audio equipment, musical instruments, etc.

Light bulbs, lamps, other lighting equipment, etc.

Tools for drilling, sawing, sewing, turning, milling, sanding, grinding, cutting,

shearing, making holes, punching, folding, bending, riveting, nailing, welding,

soldering, etc.

Electric trains; car racing sets; video game consoles; computers for biking, diving,

running, rowing, etc.; sports equipment with electric or electronic components;

slot machines; etc.

Equipment for radiotherapy, cardiology, dialysis, and nuclear medicine; pulmonary

ventilators; laboratory equipment for in vitro fertilization, diagnosis, analyzers,

freezers, etc.

Smoke detectors, thermostats, instruments for measuring and weighing, laboratory

equipment, industrial monitoring equipment, etc.

Automatic dispensers for hot drinks, cold drinks, bottles, cans, solid products,

money, etc.

Toys, leisure and sports

equipment

Medical devices

Monitoring and control

instruments

Automatic dispensers

FIGURE 1.1

disposal.

Symbol for separate collection for

mainstay of electronics manufacturing. The legislation took

full effect on July 1, 2006. Its implications are far reaching and

apply to all electrical and electronic equipment unless specifically addressed by the main body of the legislation or an

exemption. Definitions of terms within the RoHS legislation

have been slow to come; some of the exemptions have yet to

be fully defined, whereas others have been revised. Imprecision of the legislation delayed early adoption within the electronics industry. As a result, there is no standard industry set

of materials and evaluation of alternative materials for manufacturability or for long-term reliability. Chapter 45 on

“Soldering Materials” lists and describes alternative materials

to tin-lead solder. Chapters 58 and 59 on “Reliability” provide information on methods to predict product life.

1.3.1 RoHS Restricted Materials

The RoHS directive targets six widely used materials (see Table 1.2).

1.3.2 Analysis for RoHS Compliance

The directive focuses on the smallest homogeneous part or material that can be separated

from the mass of a component or assembly. As an example, take the case of a plastic packaged

integrated circuit (IC) with a copper (Cu) lead-frame, where the lead-frame is plated with

some surface finish for solderability. The surface finish would be evaluated for RoHS compliance separate from the whole package or even from the weight of the lead-frame itself.

Instead, the weight-percent of (Pb) within the surface finish would be evaluated on the ratio of

the weight of any Pb to the weight of the surface finish plated upon the lead-frame. Similarly,

any Pb alloyed within the Cu lead-frame would be evaluated based on the total weight of the

assayed Pb to the total weight of the Cu lead-frame. Similarly, the IC’s encapsulant would be

evaluated for the weight of any PBB or PBDE as compared to the weight of the encapsulant

in which it is contained or upon which it is coated.

LEGISLATION AND IMPACT ON PRINTED CIRCUITS

1.5

TABLE 1.2 Materials Impacted by “Restriction of Hazardous Substances” Legislation

Substance

Symbol or

Abbreviation

Maximum

Allowable

Value (Wt%)

+6

Hexavalent

chromium

Cr

0.1

Cadmium

Cd

0.01

Mercury

Hg

0.1

Lead

Pb

0.1

Polybrominated

biphenyls

Polybrominated

diphenyl ethers

PBB

0.1

PBDE

0.1

Uses in Electronics

Platings, especially for surface passivation of environmentally

unstable metals, pigments, and plastics; colorant as lead

chromate; hexavalent chromate finish for plated metal

enclosures, fasteners, clips, and screws

Platings, ink pigments, paint pigments, batteries, detectors, and

thick film circuits

Pigments, curing catalyst for plastics and foams, switch contacts,

batteries PVC stabilizer, and colorant

Solder PWB surface finish; component terminations; surface

finish; PVC stabilizer and colorant; plastics colorant as lead

chromate; cables and harnesses; sheet metal plating (to reduce

risk of Zn whiskers); alloy agent for steel, copper, aluminum, etc.

Circuit board flame retardant and other electrical insulators

Circuit board flame retardant and other electrical insulators, and

flame retardant for plastics

1.3.3 Analytical Methods for RoHS Compliance

The RoHS legislation does not set forth specific recommendations for analysis, nor is there wide

consensus within the electronics community on standard analytical screening methods for determining compliance with RoHS legislation. Simple wet chemistry spot tests can be conducted for

presence or absence of Cr+6, Hg, Cd, and Pb. These tests, if conducted properly, have good sensitivity for qualitative analysis. Atomic absorption spectrophotometry (AAS), x-ray fluorescence

(XRF), energy dispersive spectroscopy (EDS or EDAX), infrared (IR) or ultraviolet (UV)

spectrophotometry, and gas chromatography-mass spectroscopy (GC-MS, that is effective for

PBB or PBDE) are but a few of the methods requiring expensive analytical instrumentation.

Quantitative data can be gleaned from these and other methods, but capital investment is high,

trained personnel are required, and use of traceable calibration standards are a must.

1.3.4 Exceptions and Exclusions

The RoHS legislation exempts numerous applications of the four targeted elemental species.

Most are not relevant to the discussion of printed circuit board soldering. Relevant applications are listed in Table 1.3.

TABLE 1.3 RoHS Exemptions as per the Second Amendment of RoHS Legislation*

Lead in high melting temperature type solders (i.e., lead-based alloys containing 85 percent by weight or more lead)

Lead in solders for servers; storage and storage array systems; network infrastructure equipment for switching,

signaling, and transmission; and network management for telecommunications

Lead in electronic ceramic parts (e.g., piezoelectronic devices)

Lead as a coating material for the thermal conduction module c-ring

Lead in solders consisting of more than two elements for the connection between the pins and the package of

microprocessors with a lead content of more than 80 percent and less than 85 percent by weight

Lead in solders to complete a viable electrical connection between semiconductor die and carrier within

integrated circuit Flip Chip packages

Cadmium and its compounds in electrical contacts and cadmium plating except for applications banned under

Directive 91-338-EEC

* Source: L 280-18 EN Official Journal of the European Union 25.10.2005, 2nd Amendment Annex to Directive 2002-95-EC.

1.6

PRINTED CIRCUITS HANDBOOK

It should be noted that even in cases where Pb is removed from a component or solder,

that the package must be otherwise RoHS-compliant.

Although counterintuitive, the directive declares an exemption for Pb-based interconnects

where the Pb content is greater than 85 percent. This exemption is meant to address specific

devices, such as ceramic ball grid arrays (CBGAs), ceramic column grid arrays (CCGAs), flipchip devices, and other high-Pb interconnection schemes. CBGAs and CCGAs rely on high

Pb-content balls or columns, respectively, which melt at higher temperatures than eutectic

Sn-Pb and thus will not collapse upon reflow. Since these ceramic devices are heavy, if the solder

balls or columns beneath were to collapse, then interconnect-to-interconnect shorting would

take place. Several years are typically needed to determine reliability impact of metallurgical

changes to IC packages. In the case of these area-array devices, the high-lead content solder

connection is an integral part of the package and not just a link between a component lead

and bonding pad on a circuit board. Further, these packages are generally used in high-end

systems such as telecommunications equipment and powerful computers. The RoHS legislation exempts such equipment from restrictions on Pb until 2010. In the meantime, package

manufacturers are working to find and test reliable replacements for Pb-based solders for

high-end packages. Some smaller ICs have already made the switch to Pb-free interconnects.

Other exclusions or exemptions detailed in the current RoHS directive are Cd and Pb in batteries, Pb in video monitor screens, and Hg in fluorescent light bulbs. It is curious to note that

RoHS legislation targets Pb in solders even though solder represents a minor use of Pb (it is

estimated to comprise less than 10 percent of world Pb usage). Conversely, the exempted

Pb-acid storage battery is the major consumer of Pb accounting for more than 85 percent

worldwide Pb usage.

In August 2006, additional exemptions were allowed for the RoHS legislation. As will be

discussed in subsequent chapters, lead has been used to reduce or eliminate the occurrence of

tin whiskers (metallic dendrites of tin that grow from pure tin surfaces). Metallic whiskers,

such as from tin or zinc, are known to pose a reliability risk in terms of electrical shorting

between oppositely charged conductors. Therefore, the RoHS legislation has been amended

to allow lead in surface finishes of components with pitch ≤0.65 mm for tin whisker repression. This applies to NiFe (Alloy 42, also known as Kovar) lead-frames as well as to components with copper lead-frames. Curiously, the exemption does not cover connectors.

1.4 RoHS’ IMPACT ON THE PRINTED CIRCUIT INDUSTRY

Never has there been such a sweeping change in electronics manufacturing as imparted by

WEEE and RoHS––particularly the latter. Every industry is being impacted either by

processes and materials or materials availability.

1.4.1 Components

Generally, ICs, passive devices, and connectors are not rated to survive temperature excursions much above that of eutectic Sn-Pb solder and are rated only to survive a brief thermal

cycle. IC makers and component manufacturers have worked to understand the impact of the

higher process temperatures required for Pb-free soldering.

Plastic encapsulated components are known to absorb water from the atmosphere.As these

components are heated to reflow soldering temperature, the water expands and can cause

component cracking. This phenomenon is popularly known as “popcorning” since the plastic

package often bulges prior to cracking and remains deformed upon cooling. To counter this,

plastic packaged components are “baked out” prior to soldering.The higher temperature regimes

of most lead-free solders will exacerbate the issue of popcorning requiring more attention to

component drying cycles. In addition, the higher reflow temperature of Pb-free soldering has

LEGISLATION AND IMPACT ON PRINTED CIRCUITS

1.7

necessitated revamping of the classification schedule for package moisture sensitivity. This is

especially relevant to components that are not hermetically sealed. Also, longer bake-out

cycles are likely required.

Many components, such as ICs and passive devices (resistors, capacitors, and so on), may

not be suited for the higher process temperatures generally associated with lead-free soldering.

The higher temperature may result in changes to electrical characteristics, cracking, melting, or

other component damage or degradation. Only components certified by the parts manufacturer or by the user should be considered for Pb-free assembly.

The manufacturer of each component assigns it a moisture sensitivity classification that

dictates how long the component can be stored in a normal workplace environment before

requiring a controlled bake-out cycle. Detailed information can be found about component

moisture sensitivity classification, storage conditions, and bake-out requirements in joint industry

standards J-STD-0201 and J-STD-033.2

In addition to changes in moisture sensitivity, component laminates, encapsulants, or overmolding compounds may be prone to degradation as a result of the higher temperature exposures and times. Other negative attributes are associated with the move to Pb-free solders. Most

of the Pb-free solders are poorer wetting (slower to spread on a solderable surface), have grainer

appearance (which is not necessarily a negative attribute, but different from what is generally

accepted as a positive attribute in lead-based solder joints).

With the advent of Pb-free solders as a mainstream technology, electrical components

meant for surface mounting are being reformulated or requalified to withstand the higher requisite temperatures of Pb-free processing. Similarly, standards organizations such as the Joint

Electron Devices Engineering Council (JEDEC) have respecified the maximum safe temperature regime for components due to the generally higher reflow soldering temperature

required for Pb-free soldering. The process engineer must consult component manufacturer’s

specifications to establish safe reflow parameters for Pb-free soldering.

1.4.2 Workmanship Standards

The most widely used workmanship standard, IPC-A-610, has been rewritten to accommodate the inspection of Pb-free soldered assemblies. The changes were introduced with version

D of that document. Inspection personnel require retraining to give proper attention to the

changes and renewed inspection criteria.

1.4.3 Laminates

Many of the widely used printed wiring board (PWB) laminates for leaded (Pb’d) solder

assembly will not endure the higher temperatures of Pb-free processing. Only laminates with

characteristic high-glass transition temperature (Tg) and high-decomposition temperature

(Td) should be investigated for use in the Pb-free process. PWB laminates are more likely to

sag during Pb-free reflow. Some may even darken in color or delaminate when exposed to

Pb-free soldering temperatures. Careful attention to material selection and testing is a must

for Pb-free soldering. Reformulation of circuit board laminates for higher temperature use is

required to reduce the possibility of warpage, charring, delamination, sagging, via- or barrelcracking, and so on. High-temperature PWB laminates are available but are typically more

expensive than those used for Sn-Pb processing.

1

J-STD-020: Joint IPC-JEDEC Standard for Moisture-Reflow Sensitivity Classification for Nonhermetic Solid State

Surface Mount Devices, Joint Electron Device Engineering Council (JEDEC),Arlington,VA, USA, and IPC-Association

Connecting Electronic Industries, Bannockburn, IL, USA.

2

J-STD-033: Joint IPC-JEDEC Standard for Handling, Packing, Shipping, and Use of Moisture-Reflow Sensitive

Surface Mount Devices, JEDEC, Arlington, VA, USA, and IPC, Bannockburn, IL, USA.

1.8

PRINTED CIRCUITS HANDBOOK

1.4.4 Solder Flux

Some of the fluxes in use for tin-lead soldering may not be compatible with the higher reflow

temperatures associated with most Pb-free alloys. Critical materials in the flux may boil off,

decompose, or oxidize before thorough fluxing can take place. Also, the flux must remain on

metal surfaces to be bonded until reflow occurs since it serves as an oxygen barrier. Were the

flux to disappear too soon, reoxidation of the solder and bonding surfaces may occur, which

will retard solder wetting. Fluxes for Pb-free solders must be tailored to the composition of

the new solder alloys and their inherently higher soldering process temperatures, and to the

Pb-free surface finishes on component leads and PWB bonding pads.

1.4.5 Hygiene

Distinct health benefits are associated with the removal of Pb from printed circuit assemblies.

Pb’s toxicity is well documented, and the most serious problems are associated with direct

ingestion of Pb-bearing materials (for example, children ingesting peeling Pb-based paint or

lead in drinking water from Pb-soldered plumbing). This accumulating heavy metal dissolves

slowly in the human body. Although there is conflicting evidence as to whether Pb from solder

can leach into the water table from landfills at a rate that warrants concern, it is in everyone’s

best interest to explore alternative solder alloys and migrate from Pb-based solders.

Printed circuit board assembly operations will certainly benefit in that the labor force will

encounter lower toxicity. Solder dross generated during wave soldering or disturbed while

performing wave solder maintenance is a major source of Pb inhalation in manufacturing

plants. Airborne dross is also generated at solder fountain operations, hot-air rework, and

even during hand soldering. The move to a Pb-free environment will also eliminate concerns

for ingested fines from Pb-contaminated hands.

1.4.6 Lead Replacement Cost

In the United States and other countries, some legislative initiatives aimed at restricting the

use of Pb have failed. This failure spurred research for solder replacement alloys. Several corporations and universities devised Pb-free solders, some of which were patented. As is the

case with any patented item or process, the rights to invention reside with the inventor or

sponsoring corporation in the short term, and several of these alloys may not be used freely.

In some cases, only slight modifications in alloy composition separate commonly available

solder alloys from patented solder compositions. The cost of patent licensing, whether by the

end user or solder manufacturer, will be borne largely by the end user.

In almost every case, the cost of Pb-free solder is at minimum 20 percent higher than for

Sn-Pb solder. PWB laminates are more costly, as are many of the components. Energy costs go

up with the need for higher reflow soldering temperatures. There is significant cost in training

of personnel to deal with the change to a Pb-free environment. Separate lines for Pb’d and Pbfree solder may be required.

Both tin and lead are abundant, easy to refine, and thus inexpensive. This is not the case for

some of the constituents of lead-free solders being considered, such as indium (In), gallium (Ga),

and silver (Ag). Even bismuth (Bi) is a minor constituent of Pb ore and comes largely from Pb

refining. In wave soldering, a large volume (hundreds of pounds) of solder is required to fill the

wave solder reservoir (solder pot). The cost and availability of some of the lead-free alloys make

them impractical for the large volume of the solder pot. Compare Sn-Pb solder at roughly USD

$1.50 per pound to Sn-0.7Cu at USD $2.30 and Sn2Ag0.8Cu0.5Sb at USD $4.00 per pound.

Granted, with lead being such a heavy element, price per pound is not the best metric; price per

unit volume is a more significant measure. Nonetheless, moving away from the Sn-Pb binary

LEGISLATION AND IMPACT ON PRINTED CIRCUITS

1.9

eutectic will mean significantly higher manufacturing materials costs. Also, during wave soldering, the molten and flowing wave will tend to dissolve certain surface finishes, which may eventually build up and change the composition of the solder alloy. Different solder alloys have

different metals dissolution properties. Therefore, using the same lead-free solder alloy for wave

soldering as for reflow may be impractical.

Some of the overt costs and impacts of moving to lead-free solders were mentioned

previously in this chapter. There are other potentially hidden costs. Soldering equipment

may not have the bandwidth to handle the higher temperatures of some of the pb-free alloys.

Reflow ovens may need to be constructed out of different materials to handle long-term

effects of the higher temperatures. Fan bushings and polymeric seals to maintain inert atmosphere

integrity may not withstand much above the temperature regimes required for Sn-Pb processing.

These same considerations apply to wave soldering. Hand soldering irons will require higher

temperatures, and more boards will likely have to be scrapped due to localized charring while

trying to attain reflow during the hand soldering operation or at repair. Board materials, fluxes,

and such may require reformulating, which is also likely to drive costs higher.

1.4.7 Equipment Changes

In some cases, soldering equipment changes are required to accommodate higher process

temperatures and contact with materials other than Sn and Pb. Such changes are discussed in

more detail in Chap. 47.

1.4.8 Scrapping and Material Mistakes

There will be costs associated with segregating materials (Pb’d versus Pb-free) and associated increased floor space for carrying two inventories (Pb’d and Pb-free). Noncompliant

materials will have to be scrapped or sold off to those still using leaded processes. It is anticipated that in the early throes of the conversion to Pb-free, parts inventories occasionally will

be inadvertently mixed, which may impact finished goods reliability and also make these

products unacceptable for import to Europe after July 1, 2006, due to tenets of the RoHS

directive.

1.4.9 Training

Every facet of manufacturing is touched by this change, whether it is the soldering process,

solder joint inspection, electrical testing, material inventories, bill-of-materials verification,

purchase specifications, inventory separation, and incoming materials inspection. The adaptations of RoHS and Pb-free standards for printed circuit assembly certainly require the

most extensive changes that the electronics industry has ever needed to make. Great care

has to go into training of personnel at every level of printed circuit assembly (PCA) building and support.

1.4.10 Reliability Testing

The change of materials and solders to accommodate the elimination of Pb necessitates reliability testing of the Pb-free assemblies to ensure that reliability is comparable to that of Sn-Pb

assemblies. Reliability test methods, parameters, and models will have to be refined to match

material properties of Pb-free assemblies.

1.10

PRINTED CIRCUITS HANDBOOK

1.4.11 In-Circuit Test (ICT)

Since the process temperature for most lead-frees are higher than for eutectic- or near-eutectic

Sn-Pb solder, any flux residues associated with No-Clean soldering are more thoroughly

baked onto PWB surface metals. This inhibits electrical test probe contact. Even with today’s

No-Clean solder pastes and with Sn-Pb solders, electrical probing can be a challenge. Often

the residues that cover test points necessitate multiple seating cycles of the test probes to penetrate the flux residue.

1.5 LEAD-FREE PERSPECTIVES

The relative benefits of removing or reducing lead remain controversial. Some studies have

shown a net negative effect due to the energy materials and processes required for the production and use of replacement lead-free materials. Whatever the long-term environmental

impact, the short-term consequences clearly create a technical challenge to ensure reliable, costeffective printed circuit assemblies. There are neither drop-in replacements for Sn-Pb solder

nor industry wide consensus for a single-solder alloy. The alloys that are most promising have

significant challenges due to raw materials pricing, limited reliability data, and yet-to-be-determined interactions with other materials. It has taken many years to understand the properties

of Sn-Pb solder, its metallurgical behavior, solder joint properties, and soldering methodologies. Any new solders will have to undergo scrutiny to determine key characteristics of

process and reliability. Since the paradigm for characterizing solders and reliability has been

honed through the millennia-long use of Sn-Pb solder, the development cycle for Pb-free solder should be significantly streamlined. On the other hand, the rapid changeover to Pb-free

solder brings with it risks with regard to process effectiveness and control, as well as the longterm reliability of the end product. These risks will require continuous reevaluations of the

solder alloy choice, appropriate surface finishes, soldering conditions, materials compatibility

(PWB, IC packages, and such), redefinition of solder volume requirements for reliable solder

joint strength, and even some equipment changes.As a result, the Chap. 45 on “Solder Materials”

contains a detailed discussion of “lead-free” alloys and materials and offer several choices on

materials and discussion of their characteristics.

Since nearly all the practical Pb-free alloy choices have a higher melting temperature, a requisite higher energy consumption and energy cost is associated with the new soldering materials. Equipment changes needed for Pb-free processing will be discussed in Chaps. 46 and 47.

Also, as Pb-based solder will remain in use until at least 2010 as per RoHS, another likely

mode of failure will be the inadvertent use of Pb-free solder with Pb’d packages or Pb’d solder with Pb-free packages. Although there is some backward and forward compatibility in

terms of solders, packages, and surface finishes, there are also some difficulties. Some packages meant for use in the Pb’d process will not tolerate the higher soldering temperatures

associated with most Pb-free solders. In the case of a Pb-free ball grid array (BGA) soldered

with Pb’d solder, or vice versa, it is already known that there will be a negative impact to the

resultant solder joint reliability for the leading Pb-free candidate solders. Increased tensile

strength with increased brittleness is commonly reported for the tin-silver-copper system––a

leading replacement candidate.

China, Japan, and Korea have legislative initiatives taking shape that are similar to the EU’s,

WEEE, and RoHS directives. This is the case for several U.S. states also. There is no escaping

the fact that Pb-free soldering will be the mainstay of all future electronics interconnections.

P

●

A

●

R

●

T

●

2

PRINTED CIRCUIT

TECHNOLOGY DRIVERS

Copyright © 2008 by The McGraw-Hill Companies. Click here for terms of use.

This page intentionally left blank

CHAPTER 2

ELECTRONIC PACKAGING

AND HIGH-DENSITY

INTERCONNECTIVITY*

Clyde F. Coombs Jr.

Editor-In-Chief, Los Altos, California

Happy T. Holden

Westwood Associates, Loveland, Colorado

2.1 INTRODUCTION

All electronic components must be interconnected and assembled to form a functional and

operating system. The design and the manufacture of these interconnections have evolved

into a separate discipline called electronic packaging. Since the early 1950s, the basic building

block of electronic packaging is the printed wiring board (PWB), and it will remain that into

the foreseeable future. This book outlines the basic design approaches and manufacturing

processes needed to produce these PWBs.

This chapter outlines the basic considerations, the main choices, and the potential tradeoffs that must be accounted for in the selection of the interconnection methods for electronic

systems. Its main emphasis is on the analysis of potential effects that the selection of various

printed wiring board types and design alternatives could have on the cost and performance of

the complete electronic product.

2.2 MEASURING THE INTERCONNECTIVITY REVOLUTION (HDI)

The continuing increase in component performance and lead density, along with the reduction in package sizes, has required that PWB technology find corresponding ways to increase

the interconnection density of the substrate. With the introduction and continued refinement

of such packaging techniques as the ball grid array (BGA), chip-scale packaging (CSP), and

chip-on-board (COB), traditional PWB technology has approached a point where alternative

ways of providing high-density interconnection have had to be developed. (See Chaps. 3 and

* Adapted from Coombs, Clyde F. Jr., Printed Circuits Handbook (4th ed.), chap. 1, “Electronic Packaging and Interconnectivity,” (McGraw-Hill, New York, 1996.)

2.3

Copyright © 2008 by The McGraw-Hill Companies. Click here for terms of use.

2.4

PRINTED CIRCUITS HANDBOOK

4 for detailed discussions of component and packaging technologies.) This has been called at

times high-density interconnects (HDI), the interconnection revolution, or the density revolution, because doing the same things in the same way, only smaller, was no longer sufficient.

2.2.1 Interconnect Density Elements

The extent of these interconnect density issues is not always observable, but the chart1 in Fig. 2.1

can help one define and understand it. The chart portrays the interrelationship between

component packaging, surface-mount technology (SMT) assembly, and PWB density. As can

be seen, these three elements are interlinked. A change in one has a significant effect on the

overall interconnection density. The metrics are as follows:

Assembly

(parts & leads

per sq. inch)

Components

(ave. leads

per part)

PWB

(inches

per sq. inch)

FIGURE 2.1 Representation of the metrics of assembly, component, and PWB technologies and their general relationship to each other.

●

●