Сброс процессора

реклама

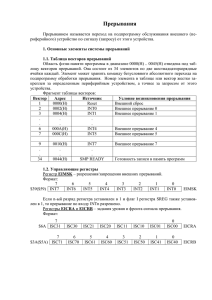

Управление работой процессора Лекция 4 Курс «Архитектура БЭВМ» Следующ ее состояни е ЗАГРУЗК А РАБОТА Состояния процессора СТОП и условия переходов СБОЙ Исходное состояни е Пошаговый режим ЗАГРУЗКА СТОП Перекл ючател и загрузк и Переключате ль рестарта, приказ запуска в команде SYGNAL PROCESSOR Переключатели сброса процессора, приказ "Стоп" в команде SYGNAL PROCESSOR, завершение шага в пошаговом режиме работы, останов по совпадению адресов РАБОТА СБОЙ Непрерывный режим - Сброс - Сбой оборудова ния Слово состояния программы PSW Текущее слово состояния программы PSW, как и управляющие регистры, содержит информацию, необходимую для управления процессом исполнения команд программы. Форматы PSW: - для z/Architecture 128 бит - для архитектуры ESA/390 64 бита Внешнее управление Предусмотрено пять инициируемых извне функций процессора: – сброс процессора – начальный сброс процессора – сброс подсистемы – сброс с очисткой – сброс по питанию Сброс процессора Сброс процессора обеспечивает очистку указателей сбоев оборудования и устраняет неопределенность состояния процессора, возникающую в результате таких сбоев, в том числе путем сохранения состояния для последующего анализа и восстановления. Сброс процессора обеспечивает: • прекращение выполнения текущей команды или других действий, например прерываний; • сброс всех условий прерываний, кроме внешних плавающих прерываний; • все предварительно выбранные команды и операнды, а также подготовленные для записи в память результаты сбрасываются; • очищаются строки буферов ALB, TLB; • если сброс вызван переключателем "загрузка - нормальная" любого из процессоров конфигурации: – устанавливается режим архитектуры ESA/390, – текущее PSW трансформируется в формат ESA/390 и сохраняется для последующего восстановления режима z/Architecture по команде SIGNAL PROCESSOR. Начальный сброс процессора Начальный сброс процессора включает: операции сброса процессора с последующими дополнительными операциями очистки и инициализации: • если сброс вызван переключателем "загрузка - нормальная", в данном процессоре и во всех процессорах конфигурации устанавливается режим архитектуры ESA/390; • содержимое текущего PSW, старого PSW, регистров префикса, таймера CP, компаратора времени, программируемого регистра TOD и регистра управления операциями с ПТ устанавливается в 0; • в управляющих регистрах устанавливаются начальные состояния, соответствующие режиму z/Architecture. Сброс подсистемы Сброс подсистемы предназначен для тех элементов конфигурации, которые не являются процессорами, путем выполнения следующих действий: • в канальной подсистеме выполняется сброс системы ввода-вывода, включая сброс прерываний ввода-вывода и передачу системного сброса в устройства ввода-вывода; • сбрасываются плавающие прерывания в конфигурации. Сброс с очисткой Сброс с очисткой объединяет операции начального сброса процессора со следующими операциями инициализации: • во всех процессорах конфигурации устанавливается режим архитектуры ESA/390; • регистры общего назначения, регистры с плавающей точкой, регистры доступа устанавливаются в 0; • содержимое основной памяти в конфигурации и соответствующие ключи памяти обнуляются; • блокировки, применяемые в любом процессоре конфигурации при исполнении команды PERFORM LOCKED OPERATION, отменяются; • выполняется сброс подсистемы. Сброс по питанию Сброс по питанию выполняется при включении питания. Сброс по питанию включает сброс регистров GR, FPR, AR в нулевое состояние и установку режима ESA/390 в случае сброса для конфигурирования или режима, в котором находятся другие процессоры. Сброс по питанию может сопровождаться сбросом TOD часов, основной и расширенной памяти и канальной подсистемы. Средства временной синхронизации (Timing) Цель - отсчет времени и взаимная синхронизация процессоров: • часы для отсчета реального времени и ведения даты и времени суток TOD сlock; • компаратор времени, предназначенный для выработки прерывания, когда показания часов TOD превышают установленное программой значение; • процессорный таймер (CPU Timer), обеспечивающий измерение прошедшего времени и выработку прерывания в случае истечения заданного интервала времени. Часы TOD Состояния часов TOD: Часы могут находиться в одном из следующих состояний: • Выставлены (CR0, бит TOD-clocksync-control), • Не выставлены, • Остановлены (команда SET CLOCK), • Неисправны или • Отключены. Установка показаний часов TOD: В многопроцессорных конфигурациях одновременное выполнение команд SET CLOCK в разных процессорах блокируется. Каждый процессор системы содержит 32-разрядный программируемый регистр TOD, младшие 16 бит которого содержат поле Programmable Field, загружаемое в память вместе с показаниями часов командой STORE CLOCK EXTENDED. Это позволяет идентифицировать показания часов для разных конфигураций. Компаратор времени • Загрузка - SET CLOCK COMPARATOR • Чтение - STORE CLOCK COMPARATOR • В некоторых моделях с целью повышения разрешающей способности компаратора сравниваются более 48 бит. • Компаратор вырабатывает прерывание в следующих случаях: – часы идут и уставка в компараторе меньше показаний часов в сравниваемых разрядах; – часы в неисправном или отключенном состоянии. Процессорный таймер Процессорный таймер - двоичный счетчик в формате, соответствующем старшим 64-м разрядам счетчика часов, исключая старший бит 0, рассматриваемый как знаковый. • Таймер декрементируется вычитанием 1 из разряда 51 каждую микросекунду. • Прерывание от таймера вырабатывается при достижении отрицательного значения, то есть, при установке 1 в разряде 0. • Загрузка в таймер выполняется командой SET CPU TIMER, а чтение - командой STORE CPU TIMER. Расхождения в отсчетах времени (Timer Stepping) • В реальной системе TOD сlock (часы для отсчета реального времени и ведения даты и времени суток и CPU Timer (процессорный таймер) отсчитывают время с одинаковой скоростью. • В виртуальной системе CPU Timer запускается только тогда, когда к ней обращается Диспетчер, поэтому может получиться, что его отсчет окажется медленнее, чем у TOD сlock Мультипроцессирование Цель - распараллеливание вычислительных процессов с разделением данных и ресурсов и обеспечение высокой готовности системы. Мультипроцессирование – это взаимодействие процессоров через общую память и средства межпроцессорных обменов. Основу мультипроцессирования составляют: • общая разделяемая память; • межпроцессорное взаимодействие; • синхронизация часов. • • • Largest z900 has 16 CPUs (model 216) Largest z990 has 32 CPUs (model D32) Largest z9 EC has 54 CPUs (model S54) Общая разделяемая память • Префиксная область (Prefix area) уникальная для каждого CPU Общие разделяемые данные должны обновляться (interlocked) с помощью специальных команд : • – TEST AND SET (antique) • – COMPARE AND SWAP • – PERFORM LOCKED OPERATION Процессоры CPUs взаимодействуют через команду SIGNAL PROCESSOR (SIGP) и внешние прерывания Дополнительные средства мультипроцессирования Дополнительными средствами являются внешние прерывания. Канальная подсистема, включая все подканалы, в мультипроцессорной конфигурации может быть доступна всем процессорам. Прерывания по вводу-выводу являются плавающими, то есть могут быть обработаны любым процессором. Сериализация! Реализация мультипроцессирования • Разделяемая память - обращение нескольких процессоров в одни и те же ячейки, определяемые одним и тем же абсолютным адресом. • Адрес процессора в системе, присваиваемый каждому процессору при инсталляции системы и не изменяемый при ее реконфигурациях. • Команда Signal Processor - основное средство взаимодействия процессоров путем сигнализации и получения ответа. • В каждом процессоре предусмотрены средства для передачи, получения и выполнения приказов, а также формирования ответа для процессора, исполняющего команду Signal Processor. • Адресуемый процессор формирует для процессора, исполняющего команду Signal Processor, код состояния. Выделение памяти и префиксация Assigned Storage Locations and Prefixing Механизм префиксации Команда SIGP Стартовая последовательность для мультипроцессирования (Start-up Sequence for Multiprocessing Operating System) • Запуск CPU 0, другие CPUs в состоянии stop • Команда SIGP установки архитектуры “set architecture” для переключения CEC из ESA/390 в z/Architecture • Задание префиксных областей (prefix area) (выделение места в памяти) для других CPUs • Инициализация перезапуска новых PSWs в префиксных областях других CPUs • Команды SIGP “set prefix” всем другим CPUs • Команды SIGP“restart” всем другим CPUs Прерывания • Прерывания процессора позволяют обеспечить быструю реакцию процессора при возникновении особых условий в самом процессоре, в подсистеме ввода-вывода, в других процессорах и вне системы. • Прерывания допускаются только в режиме РАБОТА, за исключением прерывания для рестарта, которое может быть выполнено в режимах РАБОТА или СТОП. • Инициируются прерывания запросами от устройств, в которых возникают условия прерываний. Классы прерываний Прерывание по вызову супервизора 2. Программные прерывания 3. Прерывания от схем контроля 4. Внешние прерывания 5. Прерывания вводавывода 6. Прерывание рестарта 1. There are six classes of interrupts: • – Supervisor call • – Program • – Machine check • – External • – Input/output • – Restart Each class is associated with a pair of old/new PSWs in the assigned storage locations Код прерываний Причина прерывания внутри класса уточняется кодом прерывания этого класса, который в процессе прерывания заносится в отдельную область памяти, закрепленную за данным классом. В зависимости от класса длина кода прерывания может быть 16, 32 или 64 бита. Код прерывания используется прерывающей программой для определения процедуры, выполнение которой необходимо для обработки прерывания. Класс прерываний = область памяти PSW в выделенном месте памяти Адреса размещения PSW, кодов и масок прерываний Классы Прерыван ий Адреса памяти для размещения PSW Адреса памяти для кода прерыван ия Маска прерываний Стар Новое о е в PSW в управляющих регистрах Внешние 304 432 7 CR0[48-50, 52-54, 57, 59] 134-135 Вводавывод а 368 496 6 CR6[32-39] 184-191 От схем Контроля 352 480 13 CR14[35-39] 232-239 Програм мные 336 464 1 20-23 CR0[33], CR1[57], CR8[32-47], CR9[32-36], FPC? 142-143 Рестарта 288 416 - - - Механизм приоритетов запросов на прерывание Прерывания обрабатываются в следующем порядке: • прерывание по вызову супервизора; • программные прерывания; • прерывания от схем контроля, допускающие отложенную обработку; • внешние прерывания; • прерывания ввода-вывода; • прерывание рестарта. Старые и новые PWS Функционирование процессора Исполнение команд • Основной функцией процессора является выборка и исполнение команд, включая выборку и сохранение операндов. • Биты 31, 32 текущего PSW определяют разрядность формируемых эффективных адресов: 24, 31 или 64 разряда. • Адреса команд задаются из программного счетчика, размещенного в поле слова состояния программы PSW (разряды 64 ÷ 127 или 33 ÷ 63). • Адрес очередной команды определяется путем увеличения адреса текущей команды в поле PSW на длину выбранной команды, либо из команд переходов. • Адреса операндов формируются с использованием различных полей адресных частей команд: R, B, X, D, I, L, M. • При формировании адресов обращений в ОП используется 64разрядный формат, но число используемых разрядов определяется режимом адресации. Исполнение команд • Исполнение команд • На практике действительная программы должно быть в последовательность выборки их концептуальной команд и операндов может не последовательности. совпадать с концептуальной. • Очередная команда может • Из-за необходимости быть выбрана и исполнена распараллеливания процессов после завершения действий, выборки и исполнения команд в связанных со всеми каждом процессоре, а также с предшествующими взаимного влияния процессоров, командами. работающих с общей памятью. В режимах реального, В режимах с регистрами доступа и главного и вторичного АП базового АП Текущая команда может модифицировать очередную команду Модификация очередной команды текущей командой недопустима Система блокировок обращений • Цели: - сохранение концептуальной последовательности исполнения команд в процессорах - Исключение ситуаций, когда в памяти имеются промежуточные значения операндов, доступных другим абонентам из-за фрагментарного выполнения команды Механизм блокировок обращений • Основан на сравнении эффективных адресов, формируемых процессором для обращения в память. • При совпадении адресов, связанных с одной или несколькими соседними командами, может быть выполнена блокировка. • Сравниваемые эффективные адреса являются виртуальными и их совпадение не обязательно означает обращение в одну и ту же ячейку памяти • Разные виртуальные адреса могут соответствовать одной и той же ячейке реальной памяти. Сериализация (Serialization) Под сериализацией понимается завершение всех обращений в память, концептуально предшествующих точке сериализации. Сериализацию могут вызвать: – Выполнение прерывания, – Сброс процессора или – Выполнение определенных команд Выборка команд из памяти • Включает чтение 1 ÷ 3 полуслов по адресу из текущего PSW • Допускается выборка команд как операндов, заданных в адресной части исполняемой команды. • Допускается предварительная выборка команд, сброс которых выполняется при сериализации, вкл/выкл DAT и в других случаях Варианты завершения исполнения команд: 1. Окончание Completion 2. Подавление исполнения команды Suppression 3. Аннулирование команды Nullification 4. Прекращение выполнения команды Termination Обобщенный формат строки таблицы трассировки 1÷12 бит 2÷142 байт Идентификатор типа трассировки Поля сохраняемых параметров Для адресации таблицы трассировки используется реальный адрес текущей строки, находящийся в управляющем регистре CR12. В этом же регистре указываются четыре управляющих бита разрешения перечисленных выше функций трассировки. Трассировка включает реализацию 4-х функций: • Трассировка переходов • Трассировка ASN • Неявная трассировка • Неявная трассировка • Неявная трассировка • Трассировка режимов • Прямая трассировка • Прямая трассировка Регистрация программных событий (PER) Применяется для регистрации информации о программных событиях, которая может использоваться в процессах отладки программ. Программные события: • Выполнение команды перехода при успешных условиях перехода. • Выборка команд из определенной области памяти. • Изменения содержимого определенной области памяти. • Выполнение команды записи в реальное адресное пространство (STORE USING REAL ADDRESS). Регистрация программных событий Управление регистрацией PER-событий CR9 EM B S CR10 Начальный адрес области памяти PER CR11 Конечный адрес области памяти PER Процесс регистрации программных событий включается битом R в PSW для разрешения прерывания по записи программных событий Адреса ячеек ОП 0 150÷151 PERC 15 000 ATMID 0 152÷159 161 63 PER Address 0 0000 AI 8 PAID Производительность системы и PER Для отключения механизма PER в программе следует • сбросить бит R в PSW и/или • замаскировать регистрацию кодом EM в CR9