Сброс процессора

реклама

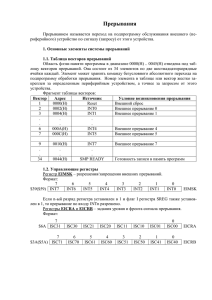

Основы построения БЭВМ Лекция 2, вторая часть (2 часа) Управление работой процессора 2.8. Состояния процессора Процессор z/Architecture может находиться в одном из четырех взаимоисключающих состояний: • СТОП - команды и прерывания (кроме прерывания для рестарта) не выполняются. • РАБОТА - команды и прерывания исполняются в соответствии с управляющими кодами в слове состояния программы, управляющих регистрах и режимом, заданным оператором. • ЗАГРУЗКА - состояние устанавливается в процессе первоначальной загрузки в соответствии с ESA/390. • СБОЙ - переход в это состояние вызывается машинными сбоями, выявленными в процессе функционирования процессора. Следую щее сост оян ие ЗАГРУЗК СТОП РАБОТА СБОЙ Состояния процессора и условия переходов А Исходно е состо яние Пошаговый режим ЗАГРУЗ КА СТОП Переключ атели загруз ки Переключате ль рестарта, приказ запуска в команде SYGNAL PROCESSO R Переключатели сброса процессора, приказ "Стоп" в команде SYGNAL PROCESSOR, завершение шага в пошаговом режиме работы, останов по совпадению адресов РАБОТА СБОЙ Непрерывный режим - Сброс - Сбой обо руд ова ния Слово состояния программы PSW Текущее слово состояния программы PSW, как и управляющие регистры, содержит информацию, необходимую для управления процессом исполнения команд программы. Форматы PSW: - для z/Architecture 128 бит - для предшествующей ей архитектуры ESA/390 64 бита Внешнее управление Предусмотрено пять инициируемых извне функций процессора: – – – – – сброс процессора; начальный сброс процессора; сброс подсистемы; сброс с очисткой; сброс по питанию. Сброс процессора • Сброс процессора обеспечивает очистку указателей сбоев оборудования и устраняет неопределенность состояния процессора, возникающую в результате таких сбоев, в том числе путем сохранения состояния для последующего анализа и восстановления. Сброс процессора обеспечивает: • прекращение выполнения текущей команды или других действий, например прерываний; • сброс всех условий прерываний, кроме внешних плавающих прерываний; • все предварительно выбранные команды и операнды, а также подготовленные для записи в память результаты сбрасываются; • очищаются строки буферов ALB, TLB; • если сброс вызван переключателем "загрузка - нормальная" любого из процессоров конфигурации, устанавливается режим архитектуры ESA/390, текущее PSW трансформируется в формат ESA/390, сохраняется для последующего восстановления режима z/Architecture по команде SIGNAL PROCESSOR. Начальный сброс процессора Начальный сброс процессора включает операции сброса процессора с последующими дополнительными операциями очистки и инициализации: • если сброс вызван переключателем "загрузка нормальная", в данном процессоре и во всех процессорах конфигурации устанавливается режим архитектуры ESA/390; • содержимое текущего PSW, старого PSW, регистров префикса, таймера CP, компаратора времени, программируемого регистра TOD и регистра управления операциями с ПТ устанавливается в 0; • в управляющих регистрах устанавливаются начальные состояния, соответствующие режиму z/Architecture. Сброс подсистемы Сброс подсистемы предназначен для тех элементов конфигурации, которые не являются процессорами, путем выполнения следующих действий: • в канальной подсистеме выполняется сброс системы ввода-вывода, включая сброс прерываний ввода-вывода и передачу системного сброса в устройства ввода-вывода; • сбрасываются плавающие прерывания в конфигурации. Сброс с очисткой Сброс с очисткой объединяет операции начального сброса процессора со следующими операциями инициализации: • во всех процессорах конфигурации устанавливается режим архитектуры ESA/390; • регистры общего назначения, регистры с плавающей точкой, регистры доступа устанавливаются в 0; • содержимое основной памяти в конфигурации и соответствующие ключи памяти обнуляются; • блокировки, применяемые в любом процессоре конфигурации при исполнении команды PERFORM LOCKED OPERATION, отменяются; • выполняется сброс подсистемы. Сброс по питанию Сброс по питанию выполняется при включении питания. Сброс CP включает сброс регистров GR, FPR, AR в нулевое состояние и установку режима ESA/390 в случае сброса для конфигурирования или режима, в котором находятся другие процессоры. Сброс CP может сопровождаться сбросом TOD часов, основной и расширенной памяти и канальной подсистемы 2.11. Средства временной синхронизации (Timing) Цель - отсчет времени и взаимная синхронизация процессоров: • часы для отсчета реального времени и ведения даты и времени суток TOD сlock; • компаратор времени, предназначенный для выработки прерывания, когда показания часов TOD превышают установленное программой значение; • процессорный таймер (CPU Timer), обеспечивающий измерение прошедшего времени и выработку прерывания в случае истечения заданного интервала времени. Часы TOD • Часы TOD представляют собой 104разрядный двоичный счетчик, который инкрементируется в типовом варианте каждую микросекунду добавлением +1 в разряд 51 Формат счетчика часов TOD 0 51 1 микросекунда 103 Состояния часов TOD: Часы могут находиться в одном из следующих состояний: • Выставлены (CR0, бит TOD-clocksync-control), • Не выставлены, • Остановлены (команда SET CLOCK), • Неисправны или • Отключены. Установка показаний часов TOD: В многопроцессорных конфигурациях одновременное выполнение команд SET CLOCK в разных процессорах блокируется. Каждый процессор системы содержит 32-разрядный программируемый регистр TOD, младшие 16 бит которого содержат поле Programmable Field, загружаемое в память вместе с показаниями часов командой STORE CLOCK EXTENDED. Это позволяет идентифицировать показания часов для разных конфигураций. Компаратор времени • Компаратор времени предназначен для сравнения показаний часов TOD с загруженной в компаратор уставкой. В типовом варианте сравниваются 48 старших разрядов счетчика часов и уставка такой же разрядности. В некоторых моделях с целью повышения разрешающей способности компаратора сравниваются более 48 бит. Компаратор вырабатывает прерывание в следующих случаях: • часы идут и уставка в компараторе меньше показаний часов в сравниваемых разрядах; • часы в неисправном или отключенном состоянии. Процессорный таймер Процессорный таймер - двоичный счетчик в формате, соответствующем старшим 64-м разрядам счетчика часов, исключая старший бит 0, рассматриваемый как знаковый. • Таймер декрементируется вычитанием 1 из разряда 51 каждую микросекунду. • Прерывание от таймера вырабатывается при достижении отрицательного значения, то есть, при установке 1 в разряде 0. • Загрузка в таймер выполняется командой SET CPU TIMER, а чтение - командой STORE CPU TIMER. 2.12. Мультипроцессирование Цель - распараллеливание вычислительных процессов с разделением данных и ресурсов и обеспечение высокой готовности системы. Мультипроцессирование – это взаимодействие процессоров через общую память и средства межпроцессорных обменов. Основу мультипроцессирования составляют: • общая разделяемая память; • межпроцессорное взаимодействие; • синхронизация часов. Дополнительные средства мультипроцессирования Дополнительными средствами являются внешние прерывания. Канальная подсистема, включая все подканалы, в мультипроцессорной конфигурации может быть доступна всем процессорам. Прерывания по вводу-выводу являются плавающими, то есть могут быть обработаны любым процессором. Реализация мультипроцессирования • Разделяемая память - обращение нескольких процессоров в одни и те же ячейки, определяемые одним и тем же абсолютным адресом. • Адрес процессора в системе, присваиваемый каждому процессору при инсталляции системы и не изменяемый при ее реконфигурациях. • Команда Signal Processor - основное средство взаимодействия процессоров путем сигнализации и получения ответа. • В каждом процессоре предусмотрены средства для передачи, получения и выполнения приказов, а также формирования ответа для процессора, исполняющего команду Signal Processor. • Адресуемый процессор формирует для процессора, исполняющего команду Signal Processor, код состояния. 2.13. Прерывания • Прерывания процессора позволяют обеспечить быструю реакцию процессора при возникновении особых условий в самом процессоре, в подсистеме ввода-вывода, в других процессорах и вне системы. • Прерывания допускаются только в режиме РАБОТА, за исключением прерывания для рестарта, которое может быть выполнено в режимах РАБОТА или СТОП. • Инициируются прерывания запросами от устройств, в которых возникают условия прерываний. Классы прерываний Все прерывания разбиты на шесть классов: 1. 2. 3. 4. 5. 6. Прерывание по вызову супервизора Программные прерывания Прерывания от схем контроля Внешние прерывания Прерывания ввода-вывода Прерывание рестарта Код прерываний Причина прерывания внутри класса уточняется кодом прерывания этого класса, который в процессе прерывания заносится в отдельную область памяти, закрепленную за данным классом. В зависимости от класса длина кода прерывания может быть 16, 32 или 64 бита. Код прерывания используется прерывающей программой для определения процедуры, выполнение которой необходимо для обработки прерывания. Класс прерываний = область памяти Каждому классу прерываний выделены две фиксированные области памяти: • Для текущего (старого) PSW прерываемой программы, • • • Старое PSW обычно содержит адрес команды, которая выполнялась бы следующей, если бы прерывания не произошло. Для нового PSW прерывающей программы Каждый процессор имеет свои области за счет механизма префиксации. Адреса размещения PSW, кодов и масок прерываний Классы Прерыван ий Адреса памяти для размещения PSW Адреса памяти для кода прерыван ия Маска прерываний Стар Новое о е в PSW в управляющих регистрах Внешние 304 432 7 CR0[48-50, 52-54, 57, 59] 134-135 Вводавывод а 368 496 6 CR6[32-39] 184-191 От схем Контроля 352 480 13 CR14[35-39] 232-239 Програм мные 336 464 1 20-23 CR0[33], CR1[57], CR8[32-47], CR9[32-36], FPC? 142-143 Рестарта 288 416 - - - Процесс прерывания Процесс прерывания включает следующие действия: • распознавание класса и причины прерывания; • сохранение текущего PSW как старого PSW распознанного класса; • сохранение информации, идентифицирующей прерывание; • выборка и размещение в процессоре нового PSW распознанного класса; • запуск прерывающей программы в соответствии с новым PSW. Возврат к прерванной программе выполняется путем восстановления в процессоре старого PSW. Плавающие (floating interruption) прерывания Прерывания, которые могут быть обработаны любым из процессоров конфигурации, называются плавающими прерываниями (floating interruption). Запрос на такое прерывание подается в первый из процессоров, в котором это прерывание не замаскировано, после чего сбрасывается для исключения повторных прерываний в других процессорах. К плавающим прерываниям относятся прерывания ввода-вывода, некоторые из внешних прерываний и от схем контроля. Маскирование • Разрешение и запрет прерываний в процессоре реализуются с использованием маскирования. • Маски прерываний размещаются в зависимости от класса в текущем PSW, управляющих регистрах, регистре управления операциями с плавающей точкой FPC. • Каждый разряд маски разрешает или запрещает соответствующее прерывание. Неразрешенные прерывания либо полностью игнорируются, либо остаются в состоянии ожидания. • Маской могут быть запрещены как все прерывания данного класса, так и отдельные типы прерываний. • Маскирование реализует механизм приоритетов прерывающих программ, когда каждая программа устанавливает разрешение или запрет ее прерывания другими программами. Механизм приоритетов запросов Прерывания обрабатываются в следующем порядке: • прерывание по вызову супервизора; • программные прерывания; • прерывания от схем контроля, допускающие отложенную обработку; • внешние прерывания; • прерывания ввода-вывода; • прерывание рестарта. PWS Обработка одновременно поступивших запросов осуществляется путем последовательной записи старых PSW и выборки новых PSW без исполнения команд прерывающих программ до тех пор, пока не будут обработаны все имеющиеся запросы. Далее в обратном порядке в соответствии с сохраненными старыми PSW выполняются прерывающие программы.