Разработка метода контроля быстродействия

реклама

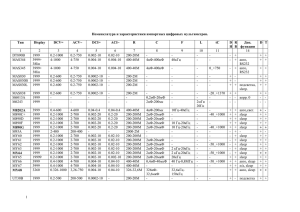

Федеральное государственное бюджетное учреждение науки Институт проблем проектирования в микроэлектронике Российской академии наук Метод снижения статической мощности КМОП-схем на основе отключающих транзисторов с контролем быстродействия Волобуев Павел Сергеевич Гаврилов Сергей Витальевич Рыжова Дарья Игоревна ИППМ РАН Содержание • Актуальность • Источники энергопотребления СБИС • Анализ реализаций метода отключения питания • Обзор существующих проблем • Разработка метода контроля быстродействия в схемах с отключением питания • Выводы и результаты ИППМ РАН 2 Актуальность Рост потребляемой мощности и уменьшение технологических норм [ S. Hanson. B. Zhai. K. Bernstein. D. Blaauw. A. Bryant. L. Chang. K. K. Das. W. Haensch. E. J. Nowak. D. M. Sylvester. Ultralow-voltage, minimum-energy CMOS. IBM Journal of Research and Development, 50:469-490, 2006. ] Необходимость оценки максимального тока потребления схемы ИППМ РАН 3 Источники энергопотребления Компоненты мощности Статическая Динамическая Iперезарядки Iкз Cнагрузки 2 Pдин fCнVDD Iутечки Токи через p-n переход Туннельные токи Ip-n W I стат COX T2 e L ИППМ РАН Подпороговые токи утечки VGS VTH nT Iт (1 e VDS T ) Iп 4 Анализ методов снижения мощности на основе отключающих транзисторов 1. Без сохранения сигнала на выходе схемы • Sleep метод • Sleep+stack метод • Zig-zag метод 2. С сохранением сигнала на выходе схемы • • • • Stack метод Sleepy stack метод Sleepy keeper метод Dual sleep метод Степень пространственного разбиения ИППМ РАН 5 Анализ методов снижения мощности на основе отключающих транзисторов Sleep Sleep+stack Sleepy keeper Dual sleep Zig-zag n-МОП ключ Stack p-МОП ключ ИППМ РАН 6 Обзор существующих проблем • Выбор схемотехнического варианта реализации метода отключения напряжения питания • Размещение и задание размеров отключающих транзисторов • Проведение корректного статического временного анализа • Автоматическое создание и распределение сигнала отключения питания • Создание корректного расписания активации/деактивации сигнала отключения питания с целью уменьшения влияния всплесков напряжения на виртуальных шинах • Минимизация энергии переключения • Проблемы при восстановлении уровня сигнала ИППМ РАН 7 Результаты моделирования тестовой схемы 4-битного сумматора Stack Sleep Sleep (multi-Vth) Sleepy Stack Статическая мощность 196X 199X 4044X 139X Динамическая мощность 0,8X 1X 1X 0,9X Sleepy Stack (multi-Vth) 199X 1X 2.4X Sleepy Keeper 40X 1,1X 1.2X Sleepy Keeper (multi-Vth) 41X 1,1X 1.2X 45 нм Статическая мощность Динамическая мощность Задержка Площадь Stack Sleep Sleep (multi-Vth) Sleepy Stack 440X 6793X 121369X 430X 0,9X 1X 1,2X 1,2X 2,8X 1,3X 1,8X 2,3X 1.62X 1.24X 1.24X 2.48X Sleepy Stack (multi-Vth) 439X 1X 2,5X 2.48X Sleepy Keeper 280X 1,2X 1,3X 1.49X Sleepy Keeper (multi-Vth) 315X 1,2X 1,3X 1.49X 90 нм Задержка Площадь 2.8X 1.2X 1.3X 2.4X 1.62X 1.24X 1.24X 2.48X 2.48X 1.49X 1.49X ИППМ РАН 8 Комплексная энергетическая метрика (PDP) ИППМ РАН 9 Разработка метода контроля быстродействия в схемах с отключением питания (1) Методы учета деградации задержки: на основе оценки пикового тока на основе оценки среднего тока Максимальное значение огибающей тока Время A1 A3 A2 t t t t t t t t A1 A3 A2 ИППМ РАН Входной вектор iA1 + iA2 + iA3 = ioverall 10 Разработка метода контроля быстродействия в схемах с отключением питания (2) td C LVdd (Vdd VtL ) td deg td t d I sleep sleep Vsleep (Vdd VtL ) CLVdd td sleep td sleep (1 )td td Rsleep I sleep Vdd VtL ((Vdd Vsleep ) VtL ) Vsleep td td ((Vdd Vsleep ) VtL ) td 2 Vsleep nCox (W L) sleep (Vdd VtL )Vsleep 2 (W L) sleep I sleep (1 deg) n Cox (Vdd VtL )(Vdd VtH ) I sleep max |gates| max I switch i 1 Интервальный подход: I j sleep max p i I ijp ИППМ РАН i 1 11 Оценка ширины отключающего транзистора от коэффициента деградации задержки Ряд 1 – все ячейки переключаются одновременно Ряд 2 – интервальный подход ИППМ РАН 12 Разработка метода контроля быстродействия в схемах с отключением питания (3) Схема для характеризации максимального пропускного тока отключающего транзистора График зависимости Imax и VVDD отключающего транзистора от параметра W ИППМ РАН 13 Разработка метода контроля быстродействия в схемах с отключением питания (4) Схема характеризации задержки прохождения сигнала для базовых элементов Падение напряжения на виртуальной шине VVDD, мВ ИППМ РАН 5 10 20 40 80 100 Процент деградации задержки, % NAND2X0 C17 C432 0,76 1,53 3,07 6,20 11,16 14,56 0,50 0,84 1,78 3,68 7,26 9,07 0,58 1,13 2,29 4,65 9,67 12,30 14 Зависимость значения пикового тока от падения напряжения на виртуальной шине питания VVDD Падение напряжения на виртуальной шине питания 40мВ Пиковый ток схемы равен 9мкА Процент деградации задержки С432 равен 4,65%. По данным характеризации выбирается p-МОП ключевой транзистор с шириной канала, равной 0,28 мкм. ИППМ РАН 15 Выводы и результаты • Проведен анализ схемотехнических подходов к уменьшению статической мощности на основе реализаций метода отключения питания • Разработан метод контроля быстродействия для схем с применением отключающих транзисторов • Применение интервального подхода к оценке пикового тока в активном режиме обеспечило точность в пределах 7% по сравнению со SPICE моделированием • Полученные значения деградации задержки могут быть использованы на этапе логического синтеза для снижения статического энергопотребления КМОП схем ИППМ РАН 16 Спасибо за внимание! ИППМ РАН 17