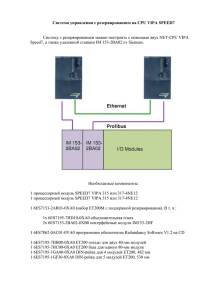

Дипломная работа

реклама

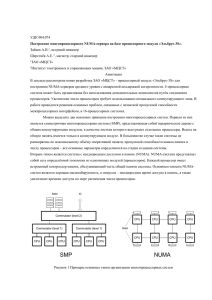

Дипломная работа Исследование и разработка системного коммутатора и оптимизирующего контроллера оперативной памяти для системы-накристалле «Эльбрус-3s» Научный руководитель: Чудаков М. Л. Шерстнёв Андрей, ФРТК Гр.112 Базовая конфигурация 4-х процессорной системы Контроллер ввода/вывода _l IO 1Gb/s in 4Gb/s k CPU #0 CPU #3 _l IO Контроллер ввода/вывода in k 2Gb/s CPU #1 CPU #2 Постановка задачи: 1. Разработка устройства для взаимосвязи процессорных модулей ВК «Эльбрус-3s» 2. Адаптация оптимизирующего контроллера памяти под разрабатываемую систему Требования: Доступ к полному объёму оперативной памяти с поддержкой когерентности для всех процессоров Построение 1-4 процессорных систем с поддержкой когерентности, с возможностью расширения до 8 процессоров Функционирование на частоте 500 МГц Поддержка различных соотношений частот процессора и памяти Внутреннее устройство процессорного модуля 17 ipcc #A 17 17 ipcc #B ipcc #C IO_link MC #0 MC #1 SC ? MAU CPU 8 CPU - процессор MC - контроллер памяти ipcc - контроллер канала межпроцессорного обмена IO_link - канал связи с «южным мостом» SC – системный коммутатор Проблемы 1. Обращение в «свою» / «чужую» память(приём и обработка запросов от 5 абонентов) 2. Невозможность одновременной проверки кэш-памяти всех процессоров 3. Обработка запроса занимает несколько тактов 4. Различная синхронизация интерфейса памяти и процессора Решения Выполнение чтения из оперативной памяти Memory Memory 3 CPU #A Memory Memory 1 CPU #B 1 CPU #A CPU #B 2 3 Memory 5 1 4 2 1 2 2 2 Memory 1 3 2 CPU #D CPU #C CPU #D Memory Memory Чтение из «чужой» памяти CPU #C Memory Чтение из «своей» памяти Запрос доступа в память Запрос проверки когерентности Когерентный ответ Данные из памяти Сообщение о завершении операции Упрощённая версия буфера запросов Процессор #1 Канал #A Канал #B #2 #3 Канал #C Контроллер ввода/вывода #4 Запрос в контроллер памяти #5 Коммутатор пакетов и буфер запросов Коммутатор пакетов Канал #A Канал #B Канал #C Процессор «Южный мост» Коммутатор Конфигурация распределения запросов и границ областей Область для запросчиков из канала #A Область для запросчиков из канала #B Область для запросчиков из канала #C Область для запросов от процессора Область для DMAзапросов Банк №1 Банк №2 В конвейер Приёмный буфер запросов Проблемы Решения 1. Обращение в «свою» / «чужую» память(приём и обработка запросов от 5 абонентов) Коммутатор пакетов + буфер запросов 2. Невозможность одновременной проверки кэш-памяти всех процессоров Буфер ожидания 3. Обработка запроса занимает несколько тактов Конвейеризация 4. Различная синхронизация интерфейса памяти и процессора Конвейер 3 2 1 Уровень 1 В буфер ожидания Уровень 2 Уровень 3 1. Повтор 2. Блокирование абонента 3. Сквозная передача Исполнение Блокировка Проблемы Решения 1. Обращение в «свою» / «чужую» память(приём и обработка запросов от 5 абонентов) Коммутатор пакетов + буфер запросов 2. Невозможность одновременной проверки кэш-памяти всех процессоров Буфер ожидания 3. Обработка запроса занимает несколько тактов Конвейеризация 4. Различная синхронизация интерфейса памяти и процессора Модуль интерфейса с контроллером памяти с оптимизацией для кратных частот Структура Системного коммутатора DMA-запрос из пространства ввода/вывода Коммутатор пакетов Запрос от процессора Входной буфер запросов Блокировка Запрос в пространство ввода/вывода Stage 0 Буфер ожидания Конвейер Буфер данных контроллеров памяти Модуль интерфейса с контроллерами памяти MC #1 DDR2 DDR2 MC #0 Сообщение от процессора «Запрос выполнен» Запрос проверки когерентности Блок пересинхронизации данных Считанные данные(250Мгц) req Stage 2 ann Сквозная передача Данные для записи в память Запросы от соседних процессоров Считанные данные(500Мгц) Подсистема памяти Максимальная загрузка канала Конвейеризация Минимальное время доступа в память(чтение) Режим параллельной работы Изменение порядка Организация памяти Адрес строки Адрес банка DDR Адрес столбца Декодер строки и логического банка Банк №3 Банк №2 Банк №1 Банк №0 Выдача данных в систему Запрос от системы Выходные драйверы Массив памяти 1 row = 1024 byte tRAS Декодер столбца Чтение/Запись IDLE Выходной буфер строки(страницы) Предзаряд Активация tCAS Active Состояния строки Изменение порядка следования запросов Время(такты) Т1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 Команды 1. 2. 3. 4. 5. 6. 7. (0,0,0) (0,1,0) (0,0,1) (0,1,3) (1,0,0) (1,1,1) (1,0,1) pre act rw pre 1 act rw pre 2 act rw pre 3 act rw pre 4 act rw 5 pre act rw 6 pre act rw 7 Банк Строка Столбец Т2 1. 2. 3. 4. 5. 6. 7. (0,0,0) (0,1,0) (0,0,1) (0,1,3) (1,0,0) (1,1,1) (1,0,1) pre act rw pre rw act pre rw act rw rw pre act rw pre act rw rw Предзаряд t=3 Активация t=2 Чтение / Запись t=1 Т1 / Т2 = 42/18 = 2,3 1 Функциональная схема оптимизирующего контроллера памяти Приём запросов от системы Тип операции Адрес (Данные) Возраст Состояние строки Блок переупорядочивания запросов Входной буфер запросов Фильтр зависимости по данным Фильтр переоткрытия строк Фильтр запросов чтения Фильтр протокольных блокировок Фильтр возраста Модуль физического интерфейса с чипами памяти Блок регенерации Режим работы контроллеров Запрос А Запрос В МС #0 МС #1 64 байта Кэш-блок А 64 байта Запрос А МС #0 32 байта МС #1 32 байта Кэш-блок А Кэш-блок В H «Честный» двухканальный режим Максимальное число открытых страниц(64). L Минимальное время чтения из памяти (сокращается на 8нс) Сравнение: freq. = 300MHz freq. = 2000MHz L2 = 256kb freq. = 500MHz L2 = 1Mb CPU #0 CPU #A 5.3Gb/s CPU #A 16Gb max. CPU #D AC 32Gb max. DC1 CPU #C CPU #D DDR2-400 HyperTransport 6.4Gb/s DDR2-500 AMD Opteron 846 Система CPU #B 8Gb/s DC0 DDR-333 CPU #1 CPU #B 6.4Gb/s L2 = 2Mb Эльбрус-3м 16Gb max. CPU #C 4Gb/s Эльбрус-3s Эльбрус-3м Эльбрус-3s Частота процессора 1.4 ~ 2.0 GHz 300 MHz 500 MHz Тип оперативной памяти DDR-333 DDR2-400 DDR2-500 Проп. спос. памяти, время доступа 5.3 Gb/s, 50 ns 6.4 Gb/s,180 ns 8 Gb/s,60 ns Проп. спос. линка, время доступа 6.4 Gb/s, 110 ns 4 Gb/s,110 ns Суммарная максимальная пропускная способность 3х6.4+5.3=24.5Gb/s 2x3.2=6.4 Gb/s 3x4+8=21 Gb/s AMD Opteron 84х Результаты: 1. Разработано Verilog-описание Системного коммутатора 2. Контроллер памяти адаптирован для системы «Эльбрус-3s» 3. Собран «стенд» для автономного тестирования 4. Произведён начальный синтез. Достигнут заданный уровень производительности при требуемой частоте: Частота функционирования - 500мгц Максимальная пропускная способность оперативной памяти – 8 GB/s Минимальное время обращения в память по считыванию – 60нс. Время чтения из памяти соседнего процессора – 110нс Интерфейс памяти DDR2-500 Поддержка различных соотношений частот процессора и памяти Возможность построения мультипроцессорной системы с общей памятью с числом процессоров до 8-ми Характеристики Общие временные характеристики: Входной буфер запросов: • Минимальное время передачи запроса от процессора в контроллер памяти: 0 тактов • Максимальный темп передачи запросов в контроллеры памяти: 4 запроса/такт • Темп приёма запросов: 2 запроса/такт • Общая ёмкость: 256 запросов • Возможность разбиения на области для 2 – 5 абонентов • Конфигурации размера области для каждого абонента • Сквозная передача(bypass) Буфер данных контроллеров памяти: Интерфейс с контроллерами памяти: • Ёмкость:1024 байт • Хранение блоков данных 32 и 64 • 100% использование ёмкости буфера независимо от соотношения блоков данных разного размера • 7 портов по записи • 2 порта по чтению • Поддержка двух контроллеров оперативной памяти Конвейер: • Число уровней: 3 • Выработка двух типов блокировок: «долговременная» и «быстрый перезапуск» • Сквозная передача запроса в контроллер памяти с первого уровня(bypass) • Два канала передачи запросов для каждого контроллера • Поддержка различных соотношений частот процессора и контроллера памяти • минимальная задержка для кратных частот Буфер ожидания: • Размер буфера: 32 ячейки • Максимальное количество ячеек, освобождаемых за 1 такт: 10. • Время определения коллизии запросов: 1 такт