Лабораторная работа N 7 - Тюменский государственный

реклама

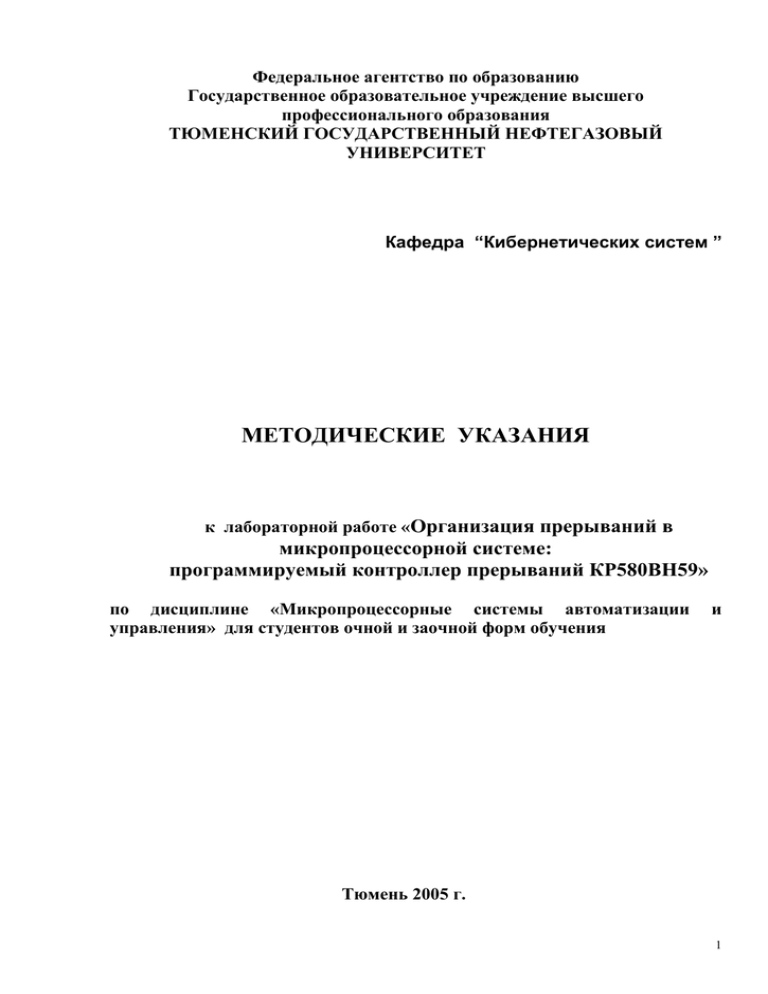

Федеральное агентство по образованию Государственное образовательное учреждение высшего профессионального образования ТЮМЕНСКИЙ ГОСУДАРСТВЕННЫЙ НЕФТЕГАЗОВЫЙ УНИВЕРСИТЕТ Кафедра “Кибернетических систем ” МЕТОДИЧЕСКИЕ УКАЗАНИЯ к лабораторной работе «Организация прерываний в микропроцессорной системе: программируемый контроллер прерываний КР580ВН59» по дисциплине «Микропроцессорные системы автоматизации управления» для студентов очной и заочной форм обучения и Тюмень 2005 г. 1 Цель работы: Изучение организации многоуровневой системы прерываний с применением программируемого контроллера КР580ВН59. Большая интегральная схема (БИС) программируемого контроллера прерываний КР580ВН59. Программируемый контроллер прерываний КР580ВН59 представляет собой законченное устройство, которое позволяет реализовывать 8-уровневую векторную систему прерываний с возможностью маскирования и динамического изменения дисциплины обслуживания. Для перехода к подпрограммам обслуживания прерываний контроллер формирует и подает на ШД процессора код команды CALL. Каскадированием БИС КР580ВН59 число обслуживаемых уровней прерывания может быть увеличено до 64. Контроллер может использоваться как для организации обмена информацией в режиме прерывания, так и для организации программноуправляемого обмена. В первом случае БИС КР580ВН59 на приоритетной основе формирует запрос на прерывание для МП и адрес подпрограммы обслуживания, во втором - процессор считыванием слова состояния контроллера определяет устройство с наивысшим приоритетом, готовое к обмену. Структура программируемого контроллера прерываний КР580ВН59 INT INTA IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7 Запросы на прерывание Регистр запросов Буфер Управления Регистр состояния GAS0 GAS1 GAS2 SP Блок управления обменом Регистр маски RD WR AO CS Блок приема запросов Внутренняя шина данных D0-D7 Буфер шины данных Рис.1 БИС КР580ВВ55 К микропроцессору 2 Микросхема КР580ВН59 размещена в пластиковом корпусе с 28 выводами, требует напряжение питания 5В и потребляет мощность 1Вт. Контроллер позволяет реализовывать приоритетный режим и режим циклического приоритета обслуживания прерываний. При реализации простого приоритетного режима всем восьми входам запросов на прерывание присваиваются фиксированные приоритеты, причем наивысший приоритет присваивается входу IR0, низший IR7. В режиме циклического после окончания обслуживания любого устройства приоритеты входов контроллера циклически изменяются таким образом, что устройству, обслуженному последним, присваивается низший приоритет. Кроме того, при работе в режиме циклического приоритета низший приоритет может быть присвоен программным способом любому входу запроса. Запросы на прерывания от внешних устройств подаются на входы IR0-IR7 контроллера и запоминаются в регистре запросов. Регистр состояния, каждый разряд которого соответствует одному из входов IR0IR7, содержит все запросы прерывания, обслуживаемые в текущий момент. Регистр маски содержит единицы в разрядах, соответствующих маскируемым в настоящий момент входам запросов. Запросы на прерывания по любому входу могут быть поданы в потенциальной или импульсной форме. Однако каждый последующий запрос на прерывание воспринимается контроллером только после выполнения подпрограммы обслуживания текущего запроса по данному входу и сброса соответствующего разряда регистра состояния, что осуществляется программным способом (специальной командой). Установка в единицу того или иного разряда регистра маски блокирует передачу запроса на прерывание. Однако, если через некоторое время после подачи запроса на прерывание маска будет снята программой, запрос будет обслужен. Программирование контроллера осуществляется двумя типами управляющих слов: управляющими словами инициализации (ICW) и операционными управляющими словами (OCW). Ввод команд в контроллер прерываний осуществляется микропроцессором командой OUT (вывод). Однако в системе может быть организовано обращение к контроллеру и как к ячейке памяти. Управляющие слова инициализации подаются перед началом работы контроллера. Они задают стартовые адреса подпрограмм обслуживания прерываний, расстояния между соседними стартовыми адресами и указывают, если необходимо, на наличие других контроллеров в системе. Операционные управляющие слова служат для оперативного изменения режимов обслуживания прерываний и могут подаваться в любое время в процессе работы контроллера. Процедура инициализации заключается в последовательном вводе в контроллер управляющих слов инициализации (ICW1 и ICW2). Если система содержит несколько контроллеров прерываний, для каждого из 3 них вслед за ICW1 и ICW2 вводится третье управляющее слово ICW3, которое определяет соподчиненность контроллеров. Перед проведением инициализации прием прерываний микропроцессором должен быть запрещен с помощью команды DI (запретить прерывание). Управление режимами работы контроллеров, изменение характера обслуживания, управление маскированием прерываний осуществляется операционными управляющими словами (OCW1, OCW2, OCW3). Таблица 1 Сигналы управления контроллера прерываний КР580ВН59 Обозначение Наименование Функциональное назначение и условия возникновения Сигналы управления записью / считыванием RD Запись (входной) Чтение (входной) WR CS Выбор микросхемы (входной) AO Адрес (входной) Запись в БИС управляющих слов Считывание из БИС содержимого внутренних регистров Формируется при определенной комбинации сигналов на ША (1-15). Осуществляет подключение ШД (0-7) БИС к шине данных системы. При отсутствии сигнала выводы ШД (0-7) БИС находятся в состоянии с высоким выходным сопротивлением Адресация регистров Сигналы управления прерыванием IR0-IR7 INT INTA Запросы на прерывание (входные) Запрос на прерывание (выходной) Разрешение прерывания Запросы на прерывание от внешних устройств Запрос на прерывание, контроллером на МП выдаваемый После поступления этого сигнала от МП контроллер осуществляет ввод в МП команды CALL Сигналы управления каскадированием SP Ведомый (входной) GAS0-GAS2 Каскадирование Высокий уровень, если контроллер является ведущим, низкий уровень – если ведомым Сигналы GAS0-GAS2 являются выходными, если контроллер является ведущим (SP=1), и входными, если – подчиненным (SP=0). Значения сигналов GAS0-GAS2ведущего контроллера, подаваемые на входы GAS0GAS2 подчиненных, указывают подчиненный контроллер, который формирует и выдает на МП адрес своей подпрограммы обслуживания 4 Управляющие слова инициализации КР580ВН59 ICW1 A0 D7 D6 D5 D4 D3 D2 0 А7 А6 А5 1 0 D1 D0 А2 А1 0 Число контроллеров в системе 1 – один 0 – более одного Разряды А7 – А5 младшего байта адреса подпрограмм обработки прерываний A0 1 D7 D6 D5 D4 Разность между стартовыми адресами 1 – 4 байта 0 – 8 байтов D3 ICW2 D2 D1 D0 А15 А14 А13 А12 А11 А10 А9 А8 0 – более одного Старший байт адреса подпрограмм обработки прерываний ICW3 (для ведущего) A0 1 D7 D6 D5 D4 D3 D2 D1 0 – более одного D0 INT7 INT6 INT5 INT4 INT3 INT2 INT1 INT0 Подключение к входу INT починенного контроллера 1 – подключен 0 – не подключен ICW3 (для ведомого) A0 D7 D6 D5 D4 D3 D2 D1 D0 1 X X X X X N2 N1 N0 Номер входа ведущего контроллера, к которому подключен данный подчиненный Не важно Рис.2 5 Операционные управляющие слова КР580ВН59 OCW1 A0 D7 D6 D5 D4 D3 D2 D1 D0 1 М7 М6 М5 М4 М3 М2 М1 М0 Маскирование входа 1 – маска установлена 0 – маска сброшена OCW2 A0 D7 D6 D5 D4 D3 D2 D1 D0 0 Ц К СВ 0 0 1 – разряды К0 используются 0 – не используются К2 К1 К0 Номер входа запроса, которому присваивается низший приоритет 1 – сброс разряда с высшим приоритетом 0 – не действует 1 – режим циклического приоритета 0 – простой приоритетный режим Рис.3а 6 OCW3 A0 D7 D6 D5 D4 D3 D2 D1 D0 0 X СМ1 СМ0 0 1 П Р1 Р0 Считывание регистров 0 1 0 1 0 0 1 1 не воздейрегистры ствует запр. сост. Безразлично Режим маскирования 0 1 0 1 0 0 1 1 Сброс Установка не воздействует режима режима 1 – разрешает в следующем цикле считать номер запроса с наивысшим приоритетом Рис. 3б Для задания простого приоритетного режима не требуется никаких дополнительных команд, кроме команд инициализации. После приема микропроцессором запроса на прерывание INT и выдачи сигнала разрешения прерываний INTA триггер разрешения прерываний микропроцессора сбрасывается, запрещая тем самым прием прерываний. Поэтому для организации многоуровневой системы прерываний необходимо выполнить программную установку этого триггера командой ЕI (разрешить прерывание) МП. Об окончании выполнения подпрограммы обслуживания каждого запроса на прерывание МП должен сообщать контроллеру с помощью OCW2. При этом осуществляется сброс либо указанного в команде разряда регистра состояния контроллера, либо разряда, соответствующего обслуженному прерыванию. Для реализации многоуровневой системы прерываний каждая из подпрограмм обслуживания должна иметь определенную структуру. Структура подпрограммы показана на рис.4. 7 Список литературы 1. Большие интегральные схемы запоминающих устройств: Справочник/ под ред. А.Ю.Гордонова и Ю.Н.Дьякова. - М.: Радио и связь, 1990. - 288 с. 2. Самофалов К.Г. и др. Микропроцессоры. – Киев: Техника, 1986. – 278 с., ил. – Библиогр.: с. 277. 3. Мячев А.А., Cтепанов В.Н. Персональные ЭВМ и микроЭВМ. Основы организации: Справочник/Под ред. А.А.Мячева. - М.: Радио и связь, 1991. 320 c. 4. Калабеков Б.А., Мамзелев И.А. Цифровые устройства и микропроцессорные системы: Учебник для техникумов связи. - М.: Радио и связь, 1987. - 400 с. 5. Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов: Учебное пособие для вузов. - М.: Радио и связь, 1988. - 368 с. 6. Коффрон Дж. Технические средства микропроцессорных систем: Практический курс. Пер. с англ. - М.: Мир, 1983. - 344 с. 7. Микропроцессоры: в 3-х кн. Кн.1 Архитектура и проектирование микроЭВМ. Организация вычислительных процессов: Учебн. для втузов/Под ред. Л.Н.Преснухина. - М.: Высш.шк., 1986. - 495 c. 8. Токхайм Р. Микропроцессоры: Курс и упражнения/Пер с англ., под ред. В.Н.Грасевича. - М.: Энергоатомиздат, 1987. - 336 c. 9. Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы. - М.: Радио и связь, 1989. 8