Документ 660097

реклама

ЮГО-ЗАПАДНЫЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

На правах рукописи

Борисенко Юлия Васильевна

Метод, алгоритмы и аппаратные средства

оперативного переразмещения программ в

отказоустойчивых мультикомпьютерных системах

Специальность 05.13.05 – Элементы и устройства вычислительной техники и

систем управления

Диссертация на соискание ученой степени

кандидата технических наук

Курск - 2014

2

СОДЕРЖАНИЕ

Введение ................................................................................................................... 4

1 Анализ методов и средств обеспечения отказоустойчивости

мультикомпьютерных систем ................................................................................ 9

1.1 Методы, модели и алгоритмы обеспечения отказоустойчивости в

мультикомпютерных системах ........................................................................................9

1.2

Модели отказоустойчивых мультикомпьютеров .........................................12

1.3

Методы и алгоритмы размещение задач в параллельных системах .....24

1.3.1 Постановка задачи размещения в мультипроцессорных системах

24

1.3.2 Методы и алгоритмы размещения подпрограмм в

мультипроцессорных системах ..................................................................... 28

1.4 Анализ путей аппаратной реализации размещения подпрограмм в

мультикомпьютерных системах....................................................................................35

1.5

Выводы ........................................................................................................................37

2 Метод оперативного переразмещения программ в отказоустойчивых

мультикомпьютерных системах .......................................................................... 39

2.1 Обобщенная постановка задачи переразмещения подпрограмм в

отказоустойчивых мультикомпьютерах.....................................................................39

2.2

Математическая постановка задачи переразмещения подпрограмм в

отказоустойчивых мультикомпьютерах.....................................................................41

2.3

Алгоритмы переразмещения подпрограмм с учётом отказов

процессоров и межпроцессорных связей...................................................................45

2.3.1 Алгоритм замены отказавшего процессора резервным ................. 45

2.3.2 Алгоритм переразмещения с учётом отказа процессора ............... 45

2.4 Выводы ........................................................................................................................49

3 Устройство оперативного переразмещения подпрограмм в

отказоустойчивых мультипроцессорных системах ........................................... 51

3.1 Принцип аппаратной реализации переразмещения подпрограмм в

отказоустойчивых мультикомпьютерах.....................................................................51

3.2

Структурная организация акселератора переразмещения ........................52

3.3

Алгоритмы функционирования акселератора...............................................54

3.4

Устройство замены отказавшего модуля резервным .................................57

3.5

Оценка производительности и быстродействия акселератора ...............63

3

3.6

Устройство поиска кратчайшего пути обхода межпроцессорной связи

67

3.7

Оценка аппаратной и временной сложности устройства поиска

кратчайшего пути обхода отказавшей межпроцессорной связи .......................73

3.8

Выводы ........................................................................................................................79

4 Моделирование алгоритмов оперативного переразмещения в

отказоустойчивых мультипроцессорных системах ........................................... 80

4.1 Программная модель процедур переразмещения с учётом отказа

процессора и/или отказа линка ......................................................................................80

4.2

Результаты исследования эффективности алгоритма планирования

размещения ...........................................................................................................................81

4.3

Результаты исследования эффективности алгоритма переразмещения

с учётом отказа процессора и/или отказа линка .....................................................87

4.4

Выводы ........................................................................................................................89

Заключение ............................................................................................................ 90

БИБЛИОГРАФИЧЕСКИЙ СПИСОК ................................................................. 92

Приложение 1 ...................................................................................................... 101

4

Введение

Актуальность темы. Отказоустойчивые мультикомпьютерные системы

(ОМС) – одно из перспективных направлений развития параллельной вычислительной техники. ОМС способны непрерывно функционировать в условиях отказа отдельных узлов и каналов связи без необходимости проведения

восстановительного ремонта за счет наличия в их архитектуре специальных

аппаратно-алгоритмических средств, позволяющих автоматически обнаруживать отказы, выполнять их изолирование (и замещение резервными ресурсами) и обеспечивать восстановление логической целостности коммуникационной среды. Благодаря этим свойствам ОМС могут успешно применяться в

качестве основы для создания критических важных объектов (критических

систем, а именно: бортовые системы управления, системы управления опасными производствами и технологическими процессами и т.п.).

Теория отказоустойчивой организации мультикомпьютерных систем достаточно хорошо разработана. Большой вклад в эту область внесли работы

отечественных ученых: С.И. Баранова, Вл.В. Воеводина, В.В. Воеводина,

Ю.Ю. Громова, А.В. Каляева, И.А. Каляева, И.И. Левина, В.Г. Хорошевского, И.В. Зотова, а также зарубежных ученых: М. Флинна, К. Ванга, Р. Лонгботтома, Д. Скилликорна и др. Однако вопросы, связанные с распределением

резервных ресурсов в структуре системы, локализации отказов модулей и

связей, а также перераспределения множества выполняемых подпрограмм в

поле работоспособных модулей в этих работах рассмотрены недостаточно.

Отказы процессорных модулей и связей ОМС приводят к появлению неоднородностей в ее физической структуре. В результате уменьшается количество возможных маршрутов передачи данных, при этом возрастает их

средняя длина, что усложняет маршрутизацию данных между работоспособными модулями после реконфигурации системы. Как следствие, увеличивается среднее время межпроцессорного обмена и снижается реальная производительность системы. Одним из путей преодоления указанных послед-

5

ствий отказов является переразмещение выполняемых системой программ на

множестве работоспособных модулей с минимизацией времени межпроцессорного обмена. Переразмещение должно осуществляться за минимально

возможное время с тем, чтобы сохранялась оперативность восстановления

системы после возникновения отказов.

Задача переразмещения имеет высокую вычислительную сложность изза ее комбинаторного характера, поэтому, учитывая жесткие временные

ограничения, целесообразно полностью перенести ее решение на аппаратный

уровень. Аппаратные решения аналогичных комбинаторных задач хорошо

известны, однако они не позволяют минимизировать время межпроцессорного обмена в условиях неоднородности и изменяемости физической структуры

ОМС под воздействием локальных отказов после выполнения реконфигурации с включением резервных модулей.

Таким образом, существует противоречие между объективной необходимостью повышения отказоустойчивости мультикомпьютерных систем и

недостаточными возможностями существующих средств по обеспечению

оперативной реакции на отказ с сохранением высокой реальной производительности системы.

В соответствии с вышеизложенным актуальной является научная задача разработки методов и аппаратных средств оперативного переразмещения

выполняемых системой программ на множестве работоспособных модулей (с

учетом резерва), обеспечивающих минимизацию времени межпроцессорного

обмена данными после ликвидации последствий отказа.

Цель диссертации: снижение времени восстановления структуры мультикомпьютерной системы после возникновения отказов путем разработки

метода и аппаратных средств оперативного переразмещения выполняемых

программ на основе целенаправленной пошаговой минимизации отклонения

времени межпроцессорного обмена данными от теоретической нижней оценки этого времени.

6

Объект исследования: отказоустойчивые мультикомпьютерные системы.

Предмет исследования: методы, алгоритмы и аппаратные средства размещения программ в отказоустойчивых мультикомпьютерных системах.

Работа выполнена по плану инициативных НИР 2009–2013 г.г. кафедры информационных систем и технологий Юго-Западного государственного

университета.

Задачи исследований:

1. Анализ методов и аппаратных средств обеспечения отказоустойчивости мультикомпьютерных систем, реконфигураций структуры ОМС при отказах, размещения программ на множестве процессорных модулей. Обоснование направления исследований.

2. Разработка метода оперативного переразмещения программ в мультикомпьютерных системах, обеспечивающего минимизацию времени межпроцессорного обмена данными с учетом текущего распределения отказовых

неоднородностей физической структуры системы.

3. Создание аппаратно-ориентированного алгоритма оперативного переразмещения программ в ОМП, реализующего разработанный метод, а также программной модели указанного алгоритма, позволяющей исследовать

его функционирование при различных комбинациях отказов.

4. Разработка структурно-функциональной организации специализированного устройства оперативного переразмещения программ после возникновения отказов в ОМС, оценка аппаратной сложности устройства, сравнительный анализ временных затрат на переразмещение программ в ОМС на

аппаратном и программном уровнях.

Результаты, выносимые на защиту, и их научная новизна:

1. Метод оперативного переразмещения программ в отказоустойчивых

мультикомпьютерных системах, основанный на диагональном распределении

множества резервных модулей (скользящего резерва) непосредственно в

7

матрице процессоров, новизна которого заключается в минимизации времени

межпроцессорного обмена данными путем целенаправленного пошагового

снижения отклонения указанного времени от нижней оценки наибольшей

частной коммуникационной задержки, вычисляемой по длине множества

статических маршрутов передачи данных с учетом текущей неоднородности

физической структуры системы.

2. Аппаратно-ориентированный алгоритм оперативного переразмещения программ в отказоустойчивых мультикомпьютерных системах, отличающийся реализацией поиска резервного модуля для замещения отказавшего

процессора на множестве ближайших к отказу резервных модулей.

3. Структурно-функциональная

организация

специализированного

устройства оперативного переразмещения программ в отказоустойчивых

мультикомпьютерных системах, отличающаяся наличием блоков переразмещения отказавших процессорных модулей и поиска кратчайшего маршрута

обхода, позволяющих осуществлять быстрый поиск резервного модуля для

замещения отказавшего процессора и корректировать маршруты обмена данными с учетом распределения отказовых неоднородностей в матрице ОМС.

Достоверность результатов диссертационной работы обеспечивается

корректным и обоснованным применением аппарата математической логики,

положений и методов теории множеств, графов, теории вероятностей и математической статистики, теории параллельных вычислительных систем,

теории надежности, а также подтверждается имитационным моделированием

с использованием зарегистрированных программных средств.

Практическая ценность результатов исследований:

1. Благодаря диагональному распределению множества резервных модулей непосредственно в матрице процессоров ОМС, созданный метод оперативного переразмещения программ позволяет значительно снизить время

замещения отказавших модулей резервными (время перестройки) по сравнению с методами, основанными

на введении

отдельных резервных

8

строк/столбцов (свободный захват, комбинированный захват, диагональный

захват и т.п.). При этом более высокая аппаратная избыточность системы и

несколько сниженный коэффициент использования резерва не являются критическими, поскольку последствия недостаточно оперативной реакции на отказ в системах рассматриваемого класса могут иметь катастрофический характер.

2. Разработанный аппаратно-ориентированный алгоритм оперативного

переразмещения программ в ОМС и устройство на его основе позволяют на

2-3 порядка снизить время поиска нового варианта размещения программ в

системе после возникновения отказа по сравнению с известными аналогами

(реализуемыми программно), что способствует повышению оперативности

реакции на отказ и, как следствие, увеличивает коэффициент готовности

ОМС. При этом созданный алгоритм и аппаратные средства учитывают не

только отказы процессорных модулей ОМС, но и отказы отдельных каналов

связи, что существенно расширяет область их применения.

3. Аппаратная сложность разработанного устройства для всех практически значимых случаев не превышает 106 эквивалентных вентилей (ЭВ), что

позволяет использовать его как в существующих, так и в перспективных

мультикомпьютерных системах, содержащих десятки-сотни тысяч процессорных модулей (Titan Cray XK7, IBM BlueGene/Q и т.п.).

9

1 Анализ методов и средств обеспечения отказоустойчивости

мультикомпьютерных систем

В главе рассмотрена классификация методов обеспечения отказоустойчивости мультикомпьютерных систем, структурные модели отказоустойчивых мультикомпьютеров, проведён анализ методов размещения задач в параллельных системах.

1.1 Методы, модели и алгоритмы обеспечения отказоустойчивости в

мультикомпютерных системах

Применение программируемых логических мультиконтроллеров в

устройствах группового управления критических важных объектов (критических систем), нарушение работоспособности которых в результате отказа вызывает большие материальные издержки, возможно только в том случае, если

будет обеспечиваться непрерывное управление, толерантное к отказам элемента устройства, то есть если устройства будут обладать свойством отказоустойчивости.

В рамках работы [1] под отказоустойчивостью понимается свойство

устройства выполнять возложенные на него функции при отказах его элементов.

Под d-отказоустойчивым устройством понимается устройство, которое

способно противостоять (парировать) отказам d элементов.

В работе [2] для обеспечения отказоустойчивости использовалась

структурная и информационная избыточность.

В результате развития теории надежности были сформулированы три

подхода к построению отказоустойчивых устройств, а именно: подход, основанный на использовании активной отказоустойчивости; подход, основанный

на пассивной отказоустойчивости; подход, учитывающий или сочетающий

активную и пассивную отказоустойчивость. Подход, основанный на активной отказоустойчивости, использует динамическое резервирование с контро-

10

лем функционирования работающих устройств. Пассивная отказоустойчивость обеспечивается пассивным резервированием устройства (например,

мажорированием).

Проведенные исследования, представленные в [3-6] показали эффективность скользящего резервирования со сдвигом для структурной самоорганизации матричных структур. В отличие от общего скользящего резервирования оно упрощает построение коммутаторов и сохраняет однородность

структуры и локальность связей элементов.

Статические методы обеспечения отказоустойчивости малоэффективны для применения в параллельных многопроцессорных архитектурах, поскольку они маскируют отказы и требуют значительной аппаратурной избыточности. Так, для трехканальной мажоритарной структуры требуются дополнительные аппаратурные затраты, превышающие более чем вдвое основное оборудование.

Динамические методы обеспечения отказоустойчивости эффективно

реализуются в однородных структурах при незначительных аппаратных затратах. Скользящее резервирование, являющееся лучшим инструментом повышения надежности устройств из однотипных элементов, дает наибольший

выигрыш в надежности. Введение резервной строки или столбца элементов

позволяет обеспечить более высокую надежность в сравнении с мажоритарными трёхканальными структурами. Исключение отказавших процессорных

элементов и подключение резервных осуществляется с помощью алгоритмов

реконфигурации. Под восстановлением исходной логической структуры связей распределенными средствами управления понимается структурная самоорганизация многопроцессорного устройства. При этом структурная самоорганизация достигается с помощью дополнительного встраиваемого в структуру мультипроцессора коммутатора, обеспечивающего коммутацию каналов

между исправными процессорными элементами логической структуры. При

разработке топологии мультипроцессорной системы этап структурной само-

11

организации сводится к выбору топологии отказоустойчивого устройства с

требуемой отказоустойчивостью, в которой возможно размещение исходной

логической структуры.

Согласно [45] организация хранения и доступ к распределенным программным модулям задач могут быть осуществлены несколькими способами:

хранением программных модулей в общей памяти для устройства и их перемещения в процессоры при смене режима; записью требуемых для выполнения процессором программных модулей задач в его постоянную память, с

последующим обращением к ней при смене режима; вводом буферной оперативной памяти для каждого из процессоров, в которую заранее переписываются программные модули, необходимые для выполнения следующего режима.

В работе [45] приведены основные особенности, на которых базируется

построение отказоустойчивых самоорганизующихся мультиконтроллеров,

которые включают:

1. использование структурной и алгоритмической самоорганизации

для построения отказоустойчивых мультиконтроллеров;

2. применение скользящего резервирования со сдвигом для выполнения структурной самоорганизации, что существенно снижает избыточность;

3. организацию перестройки топологии путём коммутации сообщений,

а не каналов без применения дополнительных встраиваемых коммутаторов,

что обеспечивает сохранение исходных физических связей между элементами;

4. применение распределённого управления для перестройки топологии мультиконтроллера при смене комбинации отказов процессоров и формирования виртуальных адресов с помощью аппаратных средств по состояниям только соседних элементов;

5. использование связности каждого элемента с каждым путем замены

отказавшего элемента соединительным для решетчатой топологии;

12

6. организацию управления средствами коммутации сообщений между

взаимодействующими процессорными элементами в многопроцессорном

устройстве с отказами без применения таблиц соответствия виртуальных и

физических адресов абонентов;

7. использование статического перераспределения задач при отказах в

перестроенном многопроцессорном устройстве для алгоритмической самоорганизации, обеспечивающего быстрый переход к новому плану функционирования;

8. организацию смены режима функционирования при отказах распределенным аппаратным способом, не требующим сложных управляющих таблиц и хранения в каждом из процессоров состояния всех элементов устройства;

9. хранение в каждом из процессорных элементов только ограниченного числа программных модулей, необходимых для выполнения планов реализации задач при допустимых отказовых ситуациях;

10.применение в каждом из процессоров мультиконтроллера многофункционального (многоалгоритмического) динамического автомата (микроконтроллера).

Из множества моделей реакции на отказ в случае использования критически важных объектов (критических систем), таких как системы слежения, наблюдений, контроля и т.д. необходимо выбрать такую, которая позволит оперативно реагировать на отказовую ситуацию и в минимальные временные сроки заменять отказавший (сбойный) модуль резервным и переназначать ранее назначенные задачи (подпрограммы) на новую систему.

С этой целью рассмотрим существующие модели отказоустойчивых

мультикомпьютерных систем.

1.2 Модели отказоустойчивых мультикомпьютеров

Объектом обеспечения отказоустойчивости является мультиконтроллер

(МК), представляющий собой композицию набора микроконтроллеров, реа-

13

лизующих общий логический алгоритм управления (дискретная микроконтроллерная сеть) и коммуникационной сети связи микроконтроллеров.

Задачей коммуникационной сети является организация обмена управляющими сообщениями между микроконтроллерами.

Применение мультиконтроллеров для управления наборами объектов

управления (ОУ), реализующих дискретные технологические и информационные процессы в реальном масштабе времени, допустимо, если отказавшие микроконтроллеры (МК) не приводят к нарушению функционирования

МК и его останову. Остановы при управлении в реальном времени вызывают

необратимые изменения в управляемом процессе и значительные материальные потери. Для обеспечения безостановочного (непрерывного) функционирования мультиконтроллера, он должен строиться как отказоустойчивый, то

есть нечувствительный к отказам отдельных его элементов.

В настоящее время сформулировано три подхода к построению отказоустойчивых устройств.

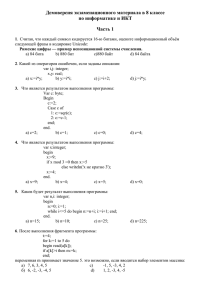

Представим структурную модель отказоустойчивого мультиконтроллера (рис. 1.1).

ССО

ИМК

Рис. 1.1. Структурная модель отказоустойчивого мультиконтроллера

Ядром отказоустойчивого мультиконтроллера является избыточный

МК (ИМК). Для реализации динамического, статического или комбинированного резервирования используется аппаратурная избыточность – избыточное число микроконтроллеров и модулей памяти МК. Условно будем счи-

14

тать, что в каждом модуле памяти содержится программный модуль (ПМ)

для реализации частного алгоритма управления. Восстановление правильного поведения мультиконтроллера после возникающих отказов обеспечивается самоорганизующей оболочкой (СОО) (рис. 1.1). Под самоорганизацией

будем понимать адаптацию, проводимую путем перестройки структуры и

функций. СОО реализует действия по коррекции отказов в соответствии с

примененным в избыточном мультиконтроллере методом резервирования.

Управляющие воздействия в зависимости от метода поступают с МК, либо из

самоорганизующего слоя.

Выбор метода резервирования зависит не только от предъявляемых

надежностных и временных требований, но и во многом определяется структурой неизбыточного устройства, Мультиконтроллер представляется решеткой микроконтроллеров (рис. 1.2).

11

12

…

1n

21

12

…

1n

…

…

…

…

m1

m2

…

mn

1

Рис. 1.2 Структура мультиконтроллера

Узлам решетки соответствуют микроконтроллеры, координаты, расположения которых соответствуют их физическим номерам. Номера выполняемых программных модулей в микроконтроллерах соответствуют их физическим номерам. Связи между микроконтроллерами соответствуют ребрам решетки.

Для регулярных структур указанные методы могут применяться на

уровне как каждого микроконтроллера (рис. 1.3а), так и всего мультиконтроллера в целом (рис. 1.3б).

15

При охвате каждого микроконтроллера самоорганизующий слой является распределенным и представляет набор мажоритарных органов (МО)

(рис.1.3а), служащий для восстановления результатов выполнения ПМ при

отказах отдельных элементов. При децентрализованном методе самоорганизации обеспечивается минимальное время самоорганизации мультиконтроллера, минимальная сложность самоорганизующий оболочки, простота связей

распределенных элементов самоорганизующего слоя (мажоритарных органов) с микроконтроллерами и высокая гибкость отказоустойчивого мультиконтроллера.

МК

МК

МК

МО

ОММК

ММК

а)

ММК

МО

ММК

ОММК

б)

Рис. 1.3 Уровни резервирования МК при статическом методе: а) для каждого

микроконтроллера; б) для всего микроконтроллера

Под гибкостью (масштабируемостью) мультиконтроллера будем понимать способность к перестройке при изменении размерности решетки МК и

усложнении общего алгоритма управления. В данном случае при наращивании, например, числа МК перестройка сводится к подключению дополнительных микроконтроллеров к соседним МК.

Однако высокие аппаратурные затраты на построение избыточного

МК, а так же отсутствие фиксации функционального отказа мультиконтроллера существенно снижают эффект от маскирования отказов микроконтроллеров.

Мажорирование на уровне мультиконтроллера в сравнении с пассивным резервированием на уровне МК практически не имеет никаких преиму-

16

ществ. Использование меньшего числа мажоритарных элементов при пассивном резервировании на уровне МК несущественно, так как аппаратурные

затраты на указанные элементы несоизмеримы с затратами на микроконтроллеры.

Таким образом, применение пассивной отказоустойчивости приводит к

высоким аппаратурным затратам, более чем вдвое превышающим неизбыточный вариант мультиконтроллера. Кроме того, в МК с пассивной отказоустойчивостью не контролируется наступление функционального отказа.

Под функциональным отказом будем понимать событие, заключающееся в

нарушении правильности функционирования мультиконтроллера.

Эффективным инструментом обеспечения активной отказоустойчивости является скользящее резервирование [45]. Скользящее резервирование

применяется для устройств, состоящих из однотипных элементов, и заключается в замене отказавшего элемента элементом из магазина резерва. В отличие от общего аппаратурного скользящего резервирования магазин резерва

для скользящего резервирования аппаратуры и программ включает магазин

элементов и программных модулей (рис. 1.4).

1

k

K

…

Магазин

элементов

…

1

1

p

k …

P

K…

Магазин программных модулей

Рис. 1.4. Модель общего скользящего аппаратного и программного резервирований

17

На рис. 1.4 кружками обозначены программные модули и прямоугольниками – элементы. Число аппаратурных элементов устройства может быть

произвольным, а число программных модулей должно быть равно числу элементов неизбыточного устройства. Реализация такой модели в устройстве

сопряжена со значительными аппаратурными и временными затратами.

Необходимы значительные средства на подключение каждого элемента резерва вместо каждого основного и на управление перекоммутацией. Кроме

того, необходимы значительные временные затраты на перезагрузку требуемого программного модуля из магазина резерва (памяти программных модулей) в заменяющий отказавший элемент аппаратурного резерва. В итоге отказоустойчивое устройство получается громоздким, с нерегулярной структурой, требующей значительного времени на самоорганизацию.

Снижения времени на самоорганизацию можно добиться, если включить все программные модули в каждый из резервных элементов. Однако негибкая структура отказоустойчивого устройства остается, и сохраняются

прежние недостатки предшествующей структуры. Кроме того, становятся

равнозначными основные элементы и резервные элементы структуры.

Равнозначность элементов сохраняется, если каждый из элементов может выполнять любой из программных модулей и заменять любой из элементов (рис. 1.5).

…

…

F

F

F

1

α

A

Рис. 1.5. Модель взаимного скользящего резервирования элементов и

программ

На рис. 1.5 стрелки F1, …, Fα, …, FA характеризуют настройку каждого

из элементов на соответствующую программу из множества {π1, ..., πk, …,

18

πК}. Представленная на рис. 1.5 модель позволяет эффективным образом

настраивать программные модули, для того чтобы характеристики образовавшейся структуры наименее отличались от исходных. Однако недостаток

применения такой структуры связан с существенными затратами на средства

коммутации, а также на построение самоорганизующий оболочки.

Исключить аппаратурные затраты на средства коммутации в устройствах со скользящим резервированием возможно, если восстанавливать не

физические связи между элементами после отказов, а логические (виртуальные) связи между элементами [45]. В этом случае каждый элемент после восстановления должен иметь данные о новом расположении программных модулей. Указанные данные позволяют передавать сообщение необходимому

программному модулю по физическому номеру элемента, в котором он находится. Для создания таких данных СОО передает сообщение, содержащее

номер элемента устройства и адрес нового исполняемого программного модуля. Время передачи указанных сообщений затягивает процесс самоорганизации, возрастающий с увеличением числа элементов устройства. Организация обхода отказавших элементов, формирование физического адреса сообщения по адресу программного модуля, обеспечение их хранения в элементе

приводит к модификации и существенному усложнению коммуникационного

блока каждого элемента устройства со скользящим резервированием. Выполнение эффективной настройки элементов приводит к сложной структуре

самоорганизующей оболочки устройства.

Отказоустойчивое устройство с взаимным скользящим резервированием элементов и программных модулей [45] можно представить следующей

обобщенной схемой (рис. 1.6).

На рисунке 1.6 блок ОЭ соответствует основным элементам устройства, блок ДЭ – дополнительным, ШН – шине настройки элементов и формирования памяти адресов элементов с соответствующими номерами про-

19

граммных модулей. В блок СОО поступают сигналы отказов основных и дополнительных элементов.

ОЭ

ДЭ

…

…

СОО

Рис. 1.6. Обобщённая схема устройства с взаимным скользящим резервированием элементов и программных модулей

В настоящее время предложен метод скользящего резервирования со

сдвигом, позволяющий с некоторой потерей эффективности при распределении программных модулей, но со значительным снижением аппаратурных

затрат на построение каждого элемента устройства и СОО реализовать отказоустойчивый МК. Структура избыточного МК для построения отказоустойчивого устройства указанным методом представляет исходную решетку элементов, дополненную столбцом и/или строкой дополнительных элементов.

Модель скользящего резервирования со сдвигом заключается в следующем.

Для каждого элемента устройства имеются элементы замены, являющегося

его соседями. Так, элементами замены для каждого основного элемента могут быть элементы, расположенные справа, вверху и по диагонали вправо

(рис. 1.7). Для каждого соседнего элемента аналогичное расположение элементов замены. Граничными элементами замены являются резервные.

При отказе каких-либо элементов устройства в соответствии с правилами самоорганизации [45] выполняется замена и восстановление структуры

(рис. 1.8).

20

Рис. 1.7. Модель скользящего резервирования со сдвигом

Рис. 1.8. Схема организации замены отказавших элементов при скользящем резервировании со сдвигом

На рис. 1.8 окружностями показаны программные модули, выполняемые элементами. Двойными прямоугольниками изображены резервные элементы. Процесс самоорганизации сводится к образованию путей замены от-

21

казавших элементов работоспособными, заканчивающихся в резервном элементе. Так, на рисунке элемент 3.1 заменяется элементом 2.2, 2.2 – 1.3, 1.3 –

1.4, 3.2 -2.3, 2.3 – 2.4, 4.1 – 4.2, 4.2 – 3.3, 3.3 – 3.4, 4.3 – 4.4. Заменившие элементы выполняют программные модули, ранее выполнявшиеся в этих позициях. В результате проводимых замен запас резерва исчерпывается. Для организации скользящего резервирования со сдвигом каждый элемент хранит

не все множество ПМ, а только соседних элементов. Самоорганизующая

оболочка реализует существенно более простой алгоритм, нежели в методе с

взаимным скользящим резервированием. Это объясняется тем, что для каждого заменяемого элемента анализируется возможность «захвата» элемента

для выполнения его ПМ только из множества соседних элементов, а не всех

элементов решетки.

Идентичность правил выбора «захватываемого» элемента для всех элементов устройства позволила построить самоорганизующую оболочку, представляющую распределенную сеть элементов самоорганизации. Указанное

обстоятельство обеспечило возможность существенно повысить гибкость отказоустойчивого устройства, реализующего метод скользящего резервирования со сдвигом.

Анализ известных алгоритмов самоорганизации элемента оболочки показал, что сигнал «захвата» зависит от состояний «работоспособность/отказ»

соседних элементов, а также состояния «захват резерва/отказ от захвата» при

сдвиге заменяемых элементов в горизонтальном направлении. Ситуация отказа от захвата характеризует событие захвата работоспособным элементом

отказавшего на пути замены (1.9).

Рис. 1.9 Схема возникновения отказа от захвата резервного элемента

22

Указанное событие фиксируется в случае появления пары расположенных друг над другом отказавших элементов или захваченного элемента и отказавшего. Сообщение об указанной ситуации передается всем элементам,

расположенным левее такой пары. Для обхода критичной пары отказавший

элемент, расположенный левее, захватывает элемент, находящийся сверху по

вертикали или диагонали в зависимости от состояния «работоспособен/отказ» и приоритетности направления замены.

Выбираемые направления замены обведены на рис. 1.10.

Рис. 1.10 Схема отказоустойчивого мультиконтроллера, реализующий скользящее резервирование со сдвигом

В результате в самоорганизующем слое (рис. 1.10) каждый его элемент

связан с соседним сигналами «захвата», «захвата резерва» (жирные линии).

Каждый элемент самоорганизации анализирует состояние «своего» и соседних микроконтроллеров и посылает сигнал настройки в «свой» МК.

На рисунке 1.10 элементы самоорганизации показаны кружками, микроконтроллеры – прямоугольниками. Массовые параллельные вычисления

настроек МК в сети элементов СОО позволяют минимизировать время самоорганизации.

Недостаток такой структуры – сложность и неоднородность связей самоорганизующий оболочки с микроконтроллерами и элементов самоорганизации между собой.

23

Структура отказоустойчивого мультиконтроллера с самоорганизующим слоем, реализующим эффективный алгоритм замены микроконтроллеров, приведена на рис. 1.11.

Рис. 1.11. Структура отказоустойчивого мультиконтроллера с

самоорганизующим слоем, реализующим эффективный алгоритм замены

микроконтроллеров

Особенностью рассматриваемого метода является его программонезависимостъ, являющаяся неотъемлемым свойством отказоустойчивых систем

с непрерывным функционированием, а значит невозможностью применения

в критических важных объектах (критических системах), где причина и тип

отказа непредсказуемы, а реакция на отказ во времени должна быть как можно меньше.

В случае возникновения сбойной ситуации в рассматриваемых системах необходима оперативная замена отказавшего модуля резервным в соответствии с выбранной отказоустойчивой организацией. Однако будет показано ниже, при возникновении сбоя изменяется топология системы, что неизбежно приведет к сбою ее работы. В этом случае необходимо оперативное

переразмещение ранее назначенных задач (программ, подпрограмм и т.д.) на

новую топологию многопроцессорной системы.

Поэтому на следующем этапе необходимо рассмотреть существующие

виды топологий многопроцессорных систем и существующий методы и ал-

24

горитмы размещения задач (программ, подпрограмм и т.д.) в многопроцессорных системах.

1.3 Методы и алгоритмы размещение задач в параллельных системах

1.3.1 Постановка задачи размещения в мультипроцессорных системах

Планирование оптимального размещения задач по множеству обрабатывающих процессоров – важный этап в процедурах подготовки комплекса

взаимодействующих программ к параллельной обработке в мультикомпьютерах и кластерных системах. Оно выполняется с целью минимизации величин коммуникационных задержек, обусловленных способом обмена данными

между задачами в ходе их обработки путем передачи сообщений между процессорами. Неудачное распределение задач между процессорами может привести к появлению длинных составных и перекрывающихся маршрутов транзитной передачи данных, возрастанию коммуникационных задержек и существенному снижению степени ускорения обработки, ожидаемой от распараллеливания.

Быстрое восстановление правильности функционирования системы путем реконфигурации ее структуры с отключением неисправного процессора

и заменой его резервным, расположенным обычно вне поля обрабатывающих

процессоров, приводит к существенному изменению конфигурации связей

между ними и образованию длинных и перекрывающихся маршрутов передачи данных. Они могут быть уменьшены и разнесены путем оперативного

переразмещения задач. В то же время процедуры планирования размещения

являются комбинаторными, имеют большую вычислительную сложность и

поэтому могут привести к существенному увеличению времени восстановления и снижению коэффициента готовности системы.

Построение параллельных систем (ПС) с распределенной памятью сталкивается с ограниченными возможностями коммуникационной сети в обеспечении быстрых передач данных [12]. Это, в свою очередь означает, что

25

стремление увеличения быстродействия за счёт использования в системах

большого числа процессоров может быть несовместимо в условиях применения конкретного набора задач с возможностями конкретной коммуникационной сети. Это также означает, что любая вычислительная система будет эффективной только на определённом классе алгоритмов и методов.

Стремление эффективно решать задачи в ПС должно сопровождаться

согласованием структуры задач и архитектуры (топологии) вычислительных

систем. В противном случае, необходимая эффективность может быть не достигнута из-за возрастания коммуникационных задержек переда данных. В то

же время, существует множество видов топологических организаций ПС и

методов размещения, дающих множество абсолютно неравнозначных способов решения, из которых необходимо выбрать подходящую с точки зрения

типа решаемых задач.

Поэтому первоначально рассмотрим топологический аспект задачи размещения.

Простейший вариант топологии – цепочечная организация (линейка)

[3,4]. Привлекательной данный вариант является с точки зрения простоты организации и как следствие малой сложности. Более того, цепочка легко расширяется с помощью добавления в нее любого количества процессорных модулей. С другой стороны, процессоров не может слишком много (не более

10-15) из-за присутствия одного канала связи и как следствие увеличения задержки при передаче сигнала через процессоры. Еще один недостаток заключается в присутствии всего одной линии связи и, следовательно, при выходе из строя любого процессорного модуля вся система выходит из строя.

Эти недостатки являются причиной того, что такие топологии практически

не используются. Тем не менее, цепочка важна, например, в матричных системах, так как любую строку или столбец можно рассматривать как линейку

(рис.1.12а-в).

26

Вариантом линейной организации является кольцо, в котором первый и

последний процессоры соединены [3,5-10]. Такой организации свойственны

теже достоинства и недостатки что и у цепочки, а именно: малая сложность,

легкость в наращивании, простота маршрутизации и т.п. Также как и линейку, кольцевую топологию можно рассматривать как часть матрицы. Тем не

менее, как и в линейке в таких системах не может более 10-20 процессорных

модулей, так как также как и в линейке, кольцо обладает низкой надежностью.

Альтернативой ПС с простой топологической организацией является

шинная архитектура. В таких системах единственный тракт передачи информации – единая магистраль, называемая шиной. Преимуществом таких топологий является независимость подключенных процессорных модулей и простота увеличения или уменьшения их количества. Это преимущество одновременно является основным недостатком такой организации, так производительность ограничена пропускной способностью шины как единственного

канала передачи информации. Поэтому такие топологии также как и линейку

и кольцо используется для относительно небольшого количества процессоров (10-20) [3, 11].

В случае использования большего количества процессоров (20-100)

применение топологий, описанных выше невозможно, и находят применение

топологии, представленные на рис. 1.2а-в. Как видно из рисунка маршрутов

передачи информации в таких системах гораздо больше, что позволяет строить более надежные системы, так как в случае отказа одного из процессоров

или межпроцессорной связи система остается работоспособной и сохраняет

возможность передачи информации в необходимый процессорный модуль

[4]. Кроме того, в таких системах возможно использование резервных процессорных модулей для общего повышения надежности.

27

а)

б)

в)

Рис. 1.12. Топологии параллельных матричных систем средних и больших

размеров

На рисунке 1.12а представлена система с матричной двунаправленной

организацией, а на рисунке 1.12б – с однонаправленной организацией. На

рис. 1.12в представлена матричная полносвязная система, в которой каждый

процессорный модуль соединен с каждым из восьми соседних процессоров.

В таких структурах каждому процессорному модулю соответствует номер

строки и столбца. В двунаправленных структурах передача информации

происходит в обоих направлениях (рис.1.12а), либо только в одном

(рис.1.12б). Как отмечалось выше, каждую строку или столбец можно

рассматривать

отдельно

как

кольцо

или

линейку.

Структуры,

представленные на рисунке 1.12в позволяют строить системы повышенной

отказоустойчивости за счет возможности передачи практически в любом

направлении и одновременно минимизировать общий трафик за счет выбор

оптимального маршрута передачи [17].

Базовые многопроцессорные блоки мультикомпютерных критических

систем как правило строятся по матричной топологии различных модификаций [45], так как они позволяют за сравнительно оптимальное время вычислять задачи, требующие минимальное время реакции вычислительной системы. Это в свою очередь позволяет реагировать на отказы и/или сбои межпро-

28

цессорных модулей за время, адекватное для оперативного решения выполняемой задачи.

1.3.2 Методы и алгоритмы размещения подпрограмм в

мультипроцессорных системах

На содержательном уровне задача размещения может быть представлена

как выбор такого варианта распределения задач между модулями ПС,

которому будет соответствовать минимальное время выполнения комплекса

взаимодействующих задач в целом [3, 5-8, 12-14,25,32-40].

При выполнении задачи размещения возникает ряд особенностей, которые необходимо учитывать при постановке задачи размещения. Они состоят

в следующем. Большое значение оказывает внутреннее взаимодействие подзадач (программ, подпрограмм, объема передаваемой информации и т.д.)

друг с другом, которое необходимо минимизировать. В этом случае, очевидно, желательно, чтобы подзадачи, которым свойственно наиболее интенсивное назначались на соседние процессорные модули. Это в свою очередь позволит сократить очереди, снизить время ожидания и в итоге позволит повысить скорость решения всей задачи в целом и повысить общую производительность системы.

С учетом выделенных факторов исходную задачу размещения можно

представить следующим образом. Найти такой способ распределения

подзадач между модулями ПС, который минимизирует [3]

интенсивности взаимодействия между смежными процессорными

модулями;

расстояния между подзадачами, которым свойственен наибольший

объем передаваемых данных.

Одним из ключевых вопросов, возникающих при решении задачи

размещения, является выбор адекватной модели представления размещаемой

задачи.

29

Исходную задачу принято представлять графом [5-7]. Традиционно

выделяют граф предшествования задач и граф взаимодействия задач. Граф

взаимодействия задач представляет собой множество вершин, соединенных

дугами. Вершины в данном случае могут означать участки исходной задачи

(программы, подпрограммы, файлы для передачи, объемов данных для передачи и т.п.), а дуги в этом случае показывают связь вершин и обычно означают передачу некоторой информации в зависимости от предназначения

вершины графа. Дуге графа, как правило, ставится в соответствие некоторое

число, которое может означать объем передаваемой информации, количество

бит и т.п. Граф предшествования задач показывает упорядоченность множестве участков.

Граф предшествования задач в отличие от графа взаимодействия задач

проявляется в динамике выполнения задачи и может использоваться, например, для построения расписания выполнения некоторых событий, где следующее событие может произойти только после завершения предыдущего.

Другим важным аспектом разработки субоптимального варианта размещения является выбор метода размещения, подходящего для решаемого

комплекса задач.

Принято различать подходы к размещению по следующим признакам

[7, 16, 17]: 1) по степени точности получаемого результата (методу решения

математических задач размещения); 2) по характеру процесса размещения

(способу формирования решений задач размещения); 3) по степени однородности ПС. Эта классификация представлена на рис. 1.17. В свою очередь

каждая категория подразделяется на отдельные подкатегории. Так, методы по

степени точности делятся на точные и приближенные. В свою очередь, точные методы подразделяются на графо-теоретические, математического программирования и ветвей и границ. Приближенные методы в зависимости от

способа формирования размещения включают: последовательные, параллельно-последовательные и итерационные методы.

30

Работа [18] посвящена «смежному размещению». Повышение пропускной способности системы предложено достичь выделением групп процессоров для заданного набора задач. При этом предложено ввести понятие

«внешней» и «внутренней» фрагментации. Считается что «внешняя» фрагментация присутствует, когда для решения требуется большое количество

процессоров, а «внутренняя» – когда некоторое количество процессоров свободно для решения некоторой задачи, но использование их невозможно. Для

устранения этого противоречия предложено использовать альтернативные

стратегии размещения: случайная, страничная, Multiply Buddy Strategy, методика скольжения структур и метод First fit и Best Fit.

Принято различать методы размещения по следующим признакам: 1)

по характеру процесса размещения 2) по степени однородности 3) по степени

точности.

По характеру процесса размещения подходы бывают динамические и

статические, по однородности – однородные и неоднородные подходы, а по

точности – точные и приближенные.

Например, к точным можно отнести работы, описанные [19-22]. Особенностью таких методов состоит в нахождении оптимальных решений за

счет значительной временной сложности. В связи с этим они применяются

лишь в случаях, когда размер многопроцессорной систем невелик (10-20

процессоров). Кроме того, в точных методах существует классификация методики поиска оптимальных решений: графо–теоретические [20-55]; математическое моделирование [19, 26] и ветвей и границ [23].

Как следует из названия, графо–теоретический метод для вычислений

использует граф и операции связанные с графом. Недостатком таких методов

является высокая сложность вычислений и как следствие длительное время

решения.

В работе [21] выполняется минимизация суммы вычислительных и коммуникационных затрат. При этом используется сетевой потоковый подход

31

Стоуна [24]. Основная идея предложенного подхода заключается в трансформации исходной задачи в двухтерминальную сетевую потоковую задачу,

после чего применяется алгоритм Голдберга-Тажана. Фактически предложенный подход учитывает только интенсивность взаимодействия без учета

длины связей и конкретной исходной топологии, чего нельзя допускать в

критических системах.

Представителем методов математического программирования является

работа [18]. Идея таких методов основана на полном переборе всех возможных вариантов размещения. Основным недостатком таких методов является

большие затраты на время поиска и емкость памяти, необходимой для хранения основных и промежуточных результатов вычислений. В работе [18] вычисления проводятся с учетом требований к емкости памяти и реальному режиму времени. В тоже время не учитываются такие особенности как формирование очередей, приоритеты и старшинство процессоров.

В [19] описана процедура размещения прикладных задач между

процессорами в распределенных компьютерных системах, основанная на

идеях метода ветвей и границ. Метод позволяет обеспечивать: 1) минимум

межпроцессорного взаимодействия, 2) сбалансированное использование

каждого процессора. Рассматривается процедура размещения, основанная на

технике бивалентного программирования и методе ветвей и границ. Для

заданной конфигурации системы ПС и набора ограничений находится

оптимальное решение для комплекса взаимодействующих задач средней

размерности. Для больших комплексов задач размещение выполняется

приближенно. Метод решения математических задач размещения для ПС состоит из следующих этапов: 1) оценка степени межпроцессорного

взаимодействия и затрат на обработку данных; 2) формулировка набора

ограничений,

встречающихся

в

различных

прикладных

задачах;

3)

реализация итерационного алгоритма для нахождения общего решения.

Функция оценки формулируется как сумма затрат на межпроцессорное

32

взаимодействие и вычислительные затраты. Технология метода ветвей и

границ представляет задачу размещения в виде поиска на дереве решений.

Целью приближенных методов [27-30] является поиск решений близких к оптимальному по какому-либо критерию и главное не требующих длительных временных затрат. Такие методы позволяет выполнять размещения

для задач с большим количеством процессорных модулей, но в тоже время

они не могут быть использованы для критических систем или систем реального времени, где решение должно быть как можно более точным и одновременно за как можно более короткое время.

Так же как и точные методы, приближенные подходы делятся на несколько подклассов [27-30], к которым можно отнести: последовательные [27], параллельно-последовательные и итерационные [28]. Коротко опишем каждый из

них.

В основе последовательных алгоритмов лежит пробный последовательный перебор и фиксация вершин и соответствующих им дуг модели. Результатом перебора является вершина для окончательной фиксации. На следующем этапе аналогично происходит пробная попытка фиксации следующей вершины и т.д. Недостатком таких алгоритмов являются решения невысокого качества и следовательно в критических системах они не могут быть

использованы.

Итерационные методы рассмотрены в [28]. В таких методах варианты

решения могут быть различны. Например, это могут быть парные перестановки и/или групповые перестановки. В итоге фиксация происходит на основе сравнения нового решения с ранее полученным и выбором лучшего из

них. По сравнению с последовательными методами итерационные дают более качественные решения, но за счет больших временных затрат.

В эвристическом алгоритме, рассмотренном в [28] для перестановок

используется матрица смежности графа, описывающая исходную задачу. В

результате выходным решением является тоже матрица смежности, соответ-

33

ствующая полученному варианту решения задачи. В матрице выполняются

вероятностные парные перестановки. Если вероятностный переход улучшает

решение, оно принимается и процесс повторяется заново. Недостатком такого подхода является возможность достижения ситуации «тупика», в случае

чего процесс поиска прекращается. Это является недостатком такого подхода.

Размещение для однородных структур рассмотрено в [23, 27, 28, 23], а

для неоднородных – в [21, 31-33].

В [23] предлагается сетевой алгоритм для матричных сетей.

Размещение в матричных сетях выполняется с использованием алгоритма Голдберг-Таржана для каждой задачи. Авторы обосновывают, что однородная сеть может быть представлена из нескольких процессоров с собственной памятью. Исходная задача задается графом взаимодействия, задающего матричную сеть. Далее из этой сеть формируется линейная матричная

сеть, после чего из нее образуется сетевой граф. Этот граф образуется за счет

добавления n вершин, причем каждая соответствует отдельному процессору.

В конечном итоге применяется сетевой алгоритм для каждого сетевого графа,

а множество (n-1) сечений весов определяют итоговый вариант размещения.

Размещение для неоднородных структур рассмотрено в [31]. При этом

для решения приняты ограничения:

– использования неоднородных процессоров;

– межпроцессорные связи в системе неоднородны;

– использование не полносвязной процессорной топологии;

– минимальные требования к синхронизации программ/подпрограмм.

Основная идея предложенного метода и алгоритма заключается в использовании критерия минимакса при размещении.

Анализ описанных методов размещения задач в параллельных системах

позволяет сделать вывод о том, что они приводят к достаточно большим временам поиска. Это препятствует быстрому динамическому переразмещению

34

задач в случае отказа какого-либо процессорного модуля. В связи с этим целесообразно перенести решение задачи размещения на аппаратный уровень и

разработать метод многократного снижения вычислительной сложности процедур планирования размещения задач по процессорам матричных базовых

блоков кластерных критических систем.

Это может быть достигнуто на основе итерационного метода субоптимального размещения [28] за счет допустимого увеличения снижения выигрыша в снижении коммуникационных задержек по сравнению с известными

методами точного оптимального размещения [19-22].

Планирование размещения предшествует маршрутизации сообщений и

должно создавать необходимые качественные предпосылки для прокладки в

топологии ПС наиболее коротких параллельных маршрутов без их перекрытия (наложения) в одном и том же канале связи между смежными процессорными модулями [3].

Из рассмотренных в п. 1.3 алгоритмов размещения можно сделать следующие выводы. Они имеют приемлемые результаты при их программной

реализации. В случае использования критических систем (системы наблюдения, слежения, контроля и т.д.) из-за выхода из строя (сбоя) одного из внутренних модулей, когда время реакции системы должно быть минимальным

применение программных способов замены отказавшего модуля резервным

либо переразмещение задач (программ, подпрограмм и т.д.) на новый вариант топологической организации неприменимо из-за длительного времени

решения. Кроме того, , количество внутренних модулей например в системах

бортовой авиации исчисляется несколькими сотнями. Решением может быть

применение соответствующих специализированных аппаратных средств резервирования и переразмещения. В связи с этим ниже рассмотрим существующие аппаратные средства.

35

1.4 Анализ путей аппаратной реализации размещения подпрограмм в

мультикомпьютерных системах

Как было показано выше, рассмотренные известные методы и алгоритмы требуют больших затрат времени на выполнение перебора значительного

числа вариантов размещения. В мультикомпьютерных критических системах

вариант размещения должен быть получен за минимальное время. В случае

отказа одного из процессоров системы и оперативной замене его резервным,

как было показано в п.п. 1.1.-1.3 изменяется топология, что приводит к необходимости оперативного переразмещения ранее назначенных подпрограмм.

Реализация этого вопроса программным способом приводит к высоким временным издержкам и вызывает необходимость привлечения аппаратных

средств. Рассмотрим варианты реализации этой задачи с помощью аппаратных средств.

В [41] предложено устройство поиска нижней оценки размещения в

матричных системах по критерию минимизации интенсивности взаимодействия процессов и данных.

Идея предложенного критерия заключается в следующем. Согласно теории метода ветвей и границ при поиске нижней оценке дуги исходного графа

задачи назначаются на процессорные модули так, что дуги с наибольшей интенсивностью (объемах информации, количества передаваемых данных и

т.д.) назначаются на соседние процессоры не обращая внимания при этом на

ограничения, которые накладывает исходных граф задачи.

Это предположение было решено использовать при проектировании

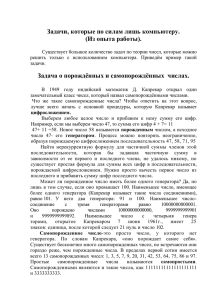

устройства, представленное на рисунке 1.13.

36

БО

1.1

&

1.2

&

&

&

1

&

+1

СЧ9.1.1

&

2.1

1.n

&

1

&

+1

…

СЧ9.1

.2

SM

2.n

2.2

ВУУ

…

Сч1

of

+1

DC

…

7

ОС

1.1

1.2

…

of

1 +1

Сч2

2.1

2.2

…

2.n

К1

m.1

m.2

…

Сч3

oe DC

+1 1 …

C

Сч4

+1of DC …

2

oe

1.n

1

ВУУ

… m.n

m.2

m.1

m.n

S

R

MX

1

1

S

R

…

…

1

S

R

of

+1

Сч5

DC …

3

Тр1

&

…

MX

2

Сч7

+1of DC

5 …

oe

G

S

R

&

of DC …

+1 4

Сч6

+1

oe DC

6 …

C

Сч8

Рис. 1.13. Устройство поиска нижней оценки размещения в параллельных системах

В устройстве на рисунке 1.13 исходный граф задачи предложено математически представлять матрицей смежности, которое в устройстве отображает блок ОС, состоящий из множества элементов 1.1,…, m.n, где m 1, n ,

n 1, n . Матрицу процессоров отображает множество блоков 1.1, 1.2,…, m.n,

где m 1, n , n 1, n . Так как исходный граф двунаправленный, то в за нижнюю

и верхнюю ее диагональ в устройстве отвечают два разных блока элементов.

За одну половину отвечают дешифраторы DC 1 и 2, счетчики Сч 3 и 4 мультиплексор MX 1. За вторую половину матрицы смежности отвечают дешифраторы DC 5 и 6, счетчики Сч 7 и 8 и мультиплексор МХ 2. Триггер ТР1 служит для переключения режимов работы устройства, к которым относится

опрос либо верхней либо нижней диоганали матрицы.

37

Работа устройства заключается в следующем. На каждом тактовом

импульсе блок ключей К1 последовательно выбирает очередную строку блока ОС, который через линейку элементов ИЛИ записывает значения строки

матрицы смежности в линейку RS-триггеров. После этого в зависимости от

состояния RS-триггера обрабатывается либо верхняя либо нижняя диагональ

матрицы смежности с помощью соответствующего блока элементов путем

последовательного перебора элементов линейки RS-триггеров, описанных

выше. В итоге обработанные значения обоих блоков устройства суммируется

в сумматоре SM и передаются для обработки во внешнее устройство ВУУ.

Недостатком рассмотренной аппаратной реализаций алгоритма размещения является ограниченные функциональные возможности, а также применительно к критическим системам, выбор критерия при поиске варианта

размещения, недостаточного для критических систем. Здесь размещение

проводилось на основе минимизации суммарной интенсивности взаимодействия между подпрограммами, что как показано в п. 1.4 является недостаточным для критических систем. Для критических систем более подходящим

критерием является минимизация задержек на всех маршрутах взаимодействия, что невозможно гарантировать при минимизации суммы интенсивностей. Недостатком является также сравнительно большое число элементарных вентилей в устройстве. В связи с этим разработка метода переразмещения подпрограмм в отказоустойчивых мультикомпьютерных системах является актуальной научной задачей, а ее важным практическим аспектом является разработка алгоритмов и структурно-функциональной организации соответствующего устройства, позволяющего ускорить составление плана размещения.

1.5 Выводы

1. Важнейшим требованием к мультипроцессорным системам является

обеспечение высокой величины коэффициента готовности, приближающейся

к единице. Однако в случае использования отказоустойчивых систем при

38

возникновении функционального отказа необходимо оперативная реакция

системы на отказ. При этом изменяется топология системы, возрастает коммуникационная задержка и требуется перестройка ее внутренней организации. Это обусловливает необходимость оперативного переразмещения ранее

назначенных подпрограмм.

2. Существующие методы планирования размещения подпрограмм обладают большим временем поиска обусловленного большим числом вариантов перебора и решаются в основном программно, что для мультикомпьютерных критических важных объектов является неприемлемым, а это определяет необходимость разработки метода и средств обеспечивающих многократное ускорение составления плана размещения.

3. Известные аппаратные средства имеют специализированную организацию, ограниченные функциональные возможности и требуют для своей

реализации большое число элементарных вентилей. В связи с этим, целесообразно разработать структурно-функциональную организацию акселератора, которая основана на типовых БИС микропроцессорных систем и в которой увеличение размера топологии системы приводит лишь к увеличению

требуемой емкости модулей оперативной памяти.

4. Высокое быстродействие, достигаемое в известных разработках путем специализации устройств, является необходимым для контроля качества

получаемого варианта размещения, которые могут быть построены на основе

подхода, используемого при разработке известных устройств размещения,

рассмотренных в данном разделе.

39

Метод оперативного переразмещения программ в отказоустойчивых

2

мультикомпьютерных системах

2.1 Обобщенная постановка задачи переразмещения подпрограмм в

отказоустойчивых мультикомпьютерах

Отказоустойчивые логические мультиконтроллеры (ОЛМК) – одно из

перспективных направлений развития многопроцессорных управляющих

систем [48-50]. В случае отказа одного из процессорных модулей ОЛМК

осуществляется

быстрое

восстановление

правильности

его

функционирования путем реконфигурации структуры с отключением

неисправного процессора и заменой его резервным, расположенным обычно

вне

поля

обрабатывающих

процессоров.

Однако

это

приводит

к

существенному изменению конфигурации связей между процессорами и

образованию длинных маршрутов передачи данных. Такие маршруты могут

быть сокращены путем оперативного переразмещения задач [2, 3]. Оценка

времени процедуры размещения являются комбинаторной задачей, имеют

большую вычислительную сложность и могут привести к существенному

увеличению времени восстановления и снижению коэффициента готовности

системы [3,4]. Поэтому необходим поиск путей уменьшения вычислительной

сложности процедур размещения задач в ОЛМК.

Преимущества использования отказоустойчивых вычислительных

систем вытекают из необходимости продолжительной работы системы в

условиях, когда техническое обслуживание (ремонт, замена и т.д.)

невозможны,

труднореализуемы

или

сопряжены

с

большими

экономическими затратами. Поэтому ВС разрабатываются таким образом,

чтобы у системы была устойчивая обратная связь к возникающим отказам в

любых условиях функционирования.

40

При отказе процессорных модулей многопроцессорной системы

можно выделить два основных типа отказов, влияющих на выполнение

назначенной задачи:

- отказ процессора;

- отказ линка - связи между процессорами;

Идентификация отказа какого-либо процессора многопроцессорной

системы классифицируется, как отказ одного из её узлов: он изолируется на

логическом

уровне

и,

при

наличии

соответствующей

поддержки,

отключается.

Идентификация отказа линка (связи) приводит к уменьшению степени

связности узлов сети. Отказавшая связь изолируется на логическом уровне

путем изменения маршрутов передачи сообщений между узлами сети.

Предполагается, что отказы элементов обнаруживаются после их возникновения, и переключение на резерв осуществляется без прерывания работы системы. При переходе на резервный процессор акселератор, разработанный в данной работе, осущесствляет логическую функцию переназначения.

В [49] авторы считают, что при исходной интенсивности отказов

η = 0,00005 1/ч (наработка на отказ составляет 20 000 ч) и интенсивности

восстановления η = 0,25 1/ч (4 ч восстановления) значение Кг = 0,99999992,

где Кг – это коэффициент готовности. Взятая наработка 20 000 ч является

нижней планкой MTBF (MeanTime Before Failure, средняя наработка на отказ) серверных платформ. Обычно для серверов приводятся значения 50–100

тыс. часов и, следовательно, получаются чрезмерно "хорошие" результаты.

В [50] авторы считают, что кластер должен обеспечить надёжность с

99,9999% обслуживаемых запросов. Т.е. сбои составляют на 0,0001% из них.

Авторы в [50] рассмотрели кластер, состоящий из 8 узлов, обслуживающий

33,8×104 запросов в течение 10 минут. Если это экстраполировать на 24-х узловой кластер серверов приложений, то получается из 53,3×10 9 запросов обслуженных за год сбои составляют не более чем 53,3×103. Если использовать

41

перезагрузку JVM это число позволяет получить 23 сбоя на один узел в течение всего года. Если использовать микроперезагрузку – 329 допустимых

сбоя.

Таким образом, из приведенного анализа следует, что для критических

важных объектов решение проблем задачи минимизации отказов является

актуальной и в случае сбоя необходима оперативная реакция со стороны системы. Из анализа, приведенного в первой главе и п. 2.1 данной работы можно сделать вывод, что в случае отказов процессорных модулей и/или процессорных связей в критических важных объектах необходимо применение специализированных аппаратно-ориентированных подходов, так как существующие, как правило, программные подходы, неприемлемы из-за длительного

времени решения. Один из путей решения этой задачи рассмотрим ниже.

2.2 Математическая постановка задачи переразмещения подпрограмм

в отказоустойчивых мультикомпьютерах

В основе созданного метода и алгоритма переразмещения программ [5155] лежат следующие понятия и теоретические построения.

Каждая из реализуемых системой программ представляется множеством

взаимосвязанных подпрограмм. Множество подпрограмм каждой программы

описывается графом взаимодействия задач:

X,E ,

(2.1)

где X xi – множество вершин, которые соответствуют отдельным подпрограммам, E eij – множество дуг, отражающих связи между подпрограммами.

AM mij

Граф

N N

представляется

матрицей

смежности

вершин:

, где N X . Значение элемента mij определяется числом со-

общений (объемом данных), передаваемых между подпрограммами xi и x j .

Топология мультикомпьютера задается графом H P1 ,V , где множество

вершин P1 соответствует процессорным модулям, а множество дуг V – меж-

42

модульным связям. Множество P1 разбивается на два непересекающихся

подмножества P1 P L , где P pij – множество основных процессоров,

L lij

–

множество

P L n 2 , n 2,3,4,

матриц pij

nn

и lij

nn

резервных

процессоров,

причем

фиксируется

. Упорядочим множества процессоров P и L в виде

соответственно. Множество P1 представим объедине-

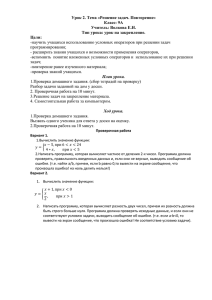

нием указанных матриц «через столбец» следующим образом (рис. 2.1):

p1.1 l1.1 p1.2 l1.2

p2.1 l2.1 p2.2 l2.2

p l p l

q.1 q.1 q.2 q.2

pn.1 ln.1 pn.2 ln.2

p1. l1.

p2. l2.

pq. lq.

pn . l n .

p1.n l1.n

p2.n l2.n

pq.n lq.n

pn .n ln .n

P1.1

(2.2)

l1.1

l1.2

P1.2

l2.1

P2.2

l2.2

Рис. 2.1. Матричная организация мультикомпьютера с резервными модулями

P2.1

Размещение множества взаимосвязанных подпрограмм, описываемого

графом , в мультикомпьютере задается отображением

: X P1 ,

(2.3)

которое ставит в соответствие каждой подпрограмме один из процессоров

(основной либо резервный).

Между каждой парой процессоров матрицы (2.2) в общем случае существует множество маршрутов передачи сообщений, которые обеспечивают

разное время доставки данных между соответствующими подпрограммами. В

рамках решаемой задачи интерес представляют кратчайшие маршруты, гарантирующие минимум указанного времени. Для описания множества таких

маршрутов вводится матрица длин LM dij

N N

, элемент dij которой чис-

43

ленно равен длине кратчайшего маршрута между процессорами, в которых

размещены подпрограммы xi и x j .

Пусть – множество всевозможных отображений вида (2.3). Тогда задача размещения программ в мультикомпьютере будет заключаться в выборе

такого отображения s , которое соответствует следующему критерию:

s min

max

i 1, N , j 1, N

d

ij

mij ,

(2.4)

где максимум в фигурных скобках представляет собой наибольшую частную

коммуникационную задержку для заданного отображения β.

Сущность созданного метода заключается в двухэтапном решении задачи переразмещения. На первом этапе вычисляется теоретически минимальная наибольшая частная коммуникационная задержка min из предположения, что граф Ф размещается в мультикомпьютере без учета ограничений

связности подпрограмм (дуги графа Ф «укладываются» наилучшим образом,

т.е. так, что более высоким значениям mij соответствуют меньшие длины

маршрутов dij ). На втором этапе отыскивается вариант размещения s , который минимизирует отклонение s min и, таким образом, дает локальный

минимум наибольшей коммуникационной задержки.

В случае наличия в мультикомпьютере отказавших процессоров [59-65]

размещение вычисления по формуле (2.4) для различных отображений вида

(2.3) проводятся с учетом неоднородности топологической структуры.

Например, при отказе процессора p1.2 выполняется перебор отображений вида (рис. 2.2):

xs xs ... xs ... xs

p l

l

x 1.1 x 1.2 ... x 1. ... x 1.n

p1.1 l1.1 p l1.2

s2.1 s2.2

s2.

s2.n

2.1 2.1 2.2 2.2

...

x x ... x ... x

sq.

sq.n

sq.1 sq.1

pq.1 lq.1 pq.2 lq.2

...

pn.1 ln.1 pn.2 ln.2

xsn.1 xsn.2 ... xsn. ... xsn.n

p1. l1.

p2. l2.

pq. lq.

pn . l n .

p1.n l1.n

p2.n l2.n

pq . n l q . n

pn .n ln .n

(2.5)

44

В этом случае учитывается, что отказавший процессор замещается резервным, например, процессором l1,2 и изменяется множество допустимых

маршрутов передачи данных.

P1.1

l1.1

P2.1

l2.1

P1.2

P2.2

l2.2

Рис. 2.2. Матричная организация мультикомпьютера с отказавшим модулем Р1,2

Процедура замещения отказавшего процессорного модуля резервным

формализуется следующим образом.

Состояние основных процессоров

Z zij

nn

Состояние резервных

ij

nn

описывается матрицей

:

zij

pij P

1, если pij неисправен;

0, если pij исправен.

процессоров

lij L

описывается

матрицей

:

ij

Матрица K kij

nn

1, если lij неисправен;

0, если lij исправен.

содержит признаки доступности ближайшего ре-

зервного модуля к процессору pij P для замены:

kij

1, если lij недоступен;

0, если lij доступен.

45

2.3 Алгоритмы переразмещения подпрограмм с учётом отказов процессоров и межпроцессорных связей

2.3.1 Алгоритм замены отказавшего процессора резервным

С учетом введенных в п. 2.2 обозначений алгоритм замещения отказавшего процессорного модуля резервным будет состоять из следующих шагов:

ЗАГРУЗИТЬ матрицы AM и LM;

УСТАНОВИТЬ zij ij kij 0, i 1, n, j 1, n ;

ЦИКЛ по всем процессорам pij P

ЕСЛИ pij P : zij 1 , то найти в матрице элемент st 0 такой,

что i s 1 j t 1 ;

ЕСЛИ такой st найден, то принять st 1 , lst pij (замещение

успешно), иначе необходим останов системы;

КОНЕЦ ЦИКЛА

Особенностью этого алгоритма является то, что поиск резервного модуля для замещения отказа ограничивается ближайшими соседями (порядок их

перебора не является существенным).

2.3.2 Алгоритм переразмещения с учётом отказа процессора

Важным этапом созданного метода переразмещения является определение теоретической нижней оценки наибольшей частной коммуникационной

задержки min max , относительно которой осуществляется минимизация времени межпроцессорного обмена при выборе варианта размещения программ

согласно постановке задачи (4). Для вычисления указанной оценки разработан следующий алгоритм.

1. Переписать все значения d kl 0 из матрицы LM в вектор LM ' в порядке невозрастания, т.е. соблюдая условие: z1 z2 : d kz1'l ' d kz''2l '' z1 z2 ,

где z1 , z2 – порядковые номера значений d k l , d k l в векторе LM ' .

46

2. Переписать все значения mij 0 из матрицы AM в вектор AM ' в

порядке неубывания, т.е. соблюдая условие: z1 z2 : miz'1j ' miz''2j '' z1 z2 ,

где z1 , z2 – порядковые номера значений mi' j' , mi'' j'' в векторе AM ' .

3. По векторам LM ' и AM ' вычислить оценку min max , используя формулу:

min max max mijz d klz ,

(2.6)

z

где mijz , dklz – элементы векторов AM ' и LM ' , расположенные в одинаковых

позициях.

В

дальнейшем

переразмещение

сводится

к

выполнению

серии

перестановок столбцов и строк матрицы AM с тем, чтобы достичь

наибольшего приближения к оценке min max . После каждой перестановки

вычисляется значение max mij d ij . Если найденное значение больше

предыдущего, то перестановки продолжаются от предыдущего варианта,

иначе далее рассматривается текущий вариант.

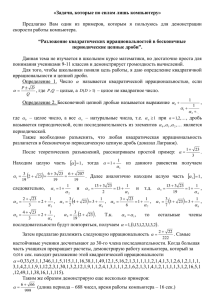

В качестве примера работы разработанных алгоритмов, рассмотрим

мультипроцессорную систему 2 2 с отказавшим модулем 2 (рис. 2.3) и соответствующую ей ММР (рис. 2.4).

1

1’

2

2’

3’

4

4’

Рис. 2.3. Матричная организация мультикомпьютера с отказавшим модулем 2

3

47

1234

10312

22021

31202

42120

Рис. 2.4. Матрица АМ для мультипроцессорной системы на рис. 2.4

Проводим поиск нижней оценки, просуммировав произведения элементов матрицы смежности и матрицы расстояния:

3 * 6 + 1 * 10 + 2 * 20 + 2 * 8 + 1 * 15 + 2 * 30 = 159.

Сравним полученные результаты, находим максимум в матрице расстояний и минимум в матрице смежности и меняем строки и столбцы местами.

Получим:

Пример матрицы смежности ЛМ

1234

10312

22021

31202

42120

Пример матрицы расстояния МА

1 2 3

1 0 10 6

2 10 0 8

3 6 8 0

4 20 30 15

С учетом вышеизложенного алгоритм

4

20

30

15

0

отказоустойчивого переразмеще-

ния программ в мультикомпьютерных системах будет состоять из следующих шагов:

1. Загрузить матрицы AM и LM;

2. Создать дополнительные матрицы M 1 , M 2 , M 3 размера N N для

хранения новых вариантов размещения после перестановок строк и столбцов

матрицы AM: M 1 – матрица, где фиксируются проверенные элементы матрицы M 2 , а M 3 – это промежуточные матрицы.

48

3. Сформировать векторы AM ' и LM ' по матрицам AM и LM соответственно.

4. Найти оценку min max по формуле (6).

5. Вычислить коммуникационную задержку 0 max

i 1, N , j 1, N

d

ij

mij для

первоначального варианта размещения 0 , определяемого матрицами AM и

LM.

6. Рассчитать отношение 0

0

min max

, если 0 (где 1 – пороговое

значение, определяющее точность решения задачи), то останов.

7. Принять 0 и M 2 AM .

8. Начать просмотр элементов вектора AM ' , начиная с элемента k 1 .

9. Пусть k-м элементом вектора AM ' является m . Найти элемент m

в матрице M 2 , определяя его положение по индексам , .

10. Найти соответствующую элементу m длину маршрута d в матрице LM.

11. Если d 1 , то (так как улучшить размещение нельзя) зафиксировать текущий элемент в M 2 как просмотренный, приняв M 2 1 . Принять

k k 1 и если вектор AM ' не просмотрен до конца, вернуться к п.9, иначе

перейти к п.12.

12. Начать просмотр строки d матрицы LM, с элемента j 1.

13. Если j N , строка просмотрена, перейти к п.24.

14. Если d j d d j 0 , то перейти к п.15, иначе принять j j 1

и вернуться к п.13.

15. Выполнить парную перестановку столбцов/строк i в матрице

AM и сформировать новую матрицу M 1 .