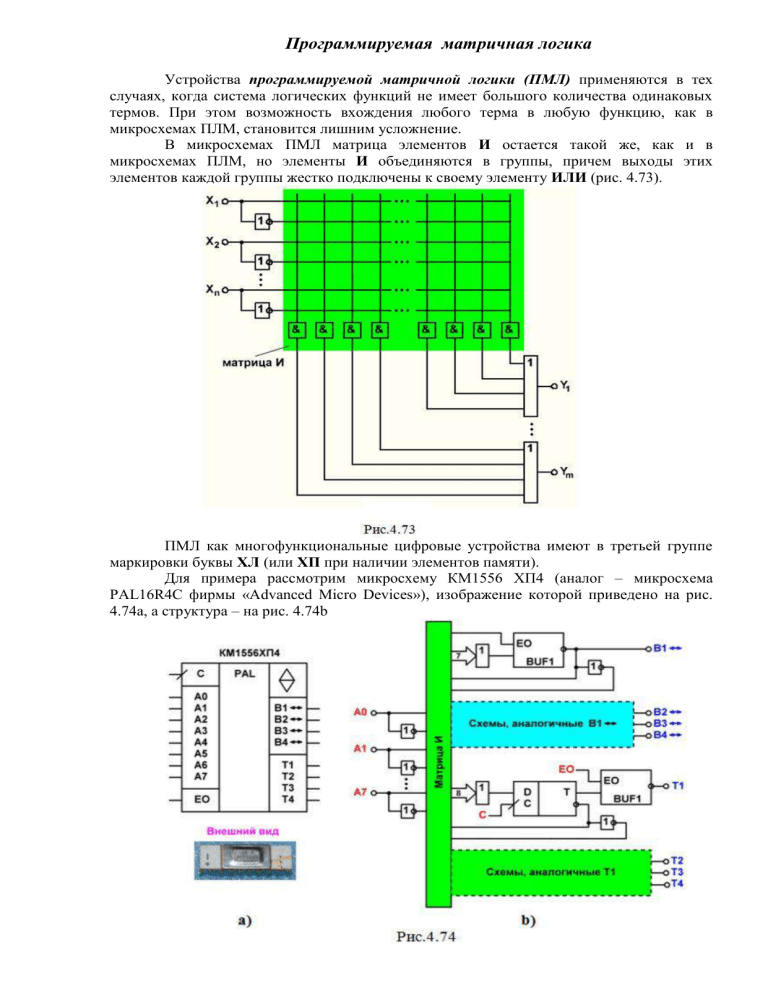

Программируемая матричная логика Устройства программируемой матричной логики (ПМЛ) применяются в тех случаях, когда система логических функций не имеет большого количества одинаковых термов. При этом возможность вхождения любого терма в любую функцию, как в микросхемах ПЛМ, становится лишним усложнение. В микросхемах ПМЛ матрица элементов И остается такой же, как и в микросхемах ПЛМ, но элементы И объединяются в группы, причем выходы этих элементов каждой группы жестко подключены к своему элементу ИЛИ (рис. 4.73). ПМЛ как многофункциональные цифровые устройства имеют в третьей группе маркировки буквы ХЛ (или ХП при наличии элементов памяти). Для примера рассмотрим микросхему КМ1556 ХП4 (аналог – микросхема PAL16R4C фирмы «Advanced Micro Devices»), изображение которой приведено на рис. 4.74a, а структура – на рис. 4.74b Матрица И, формирующая термы, имеет 8 входов А0…А7 для переменных Х. Матрица ИЛИсодержит 8 элементов ИЛИ, из них -четыре 7-входовых и -четыре 8-входовых. Выводы В1…В4 выполнены двунаправленными путем применения здесь буферных элементов BUF1с тремя состояниями. В зависимости от программирования перемычек в цепях ЕО, идущих от матрицы И, любой буфер может работать следующим образом: – в обычном режиме при формировании в цепи ЕО активного сигнала 1; тогда соответствующий вывод B используется в качестве выхода, где формируется соответствующая функция Y; – переключается в Z-состояние при формировании в цепи ЕО пассивного уровня логического 0; в этом случае соответствующий элемент ИЛИ отключается от своего вывода B, который при этом может использоваться как дополнительный вход еще для одной переменной X. На выходах T ставятся интегральные триггеры с синхронизацией по положительному перепаду импульса на входе C, способные запоминать результаты выполненных функций Y. К инверсным выходам триггеров подключены цепи обратной связи, что позволяет получать на выходах T результаты операций всех последующих тактов в зависимости от результатов операций предыдущих тактов. Кроме этого, выходы T могут одновременно переходить в Z-состояние, отключаясь по пассивному уровню сигнала на входе ЕО буферов BUF2.