пакет - MES conference

реклама

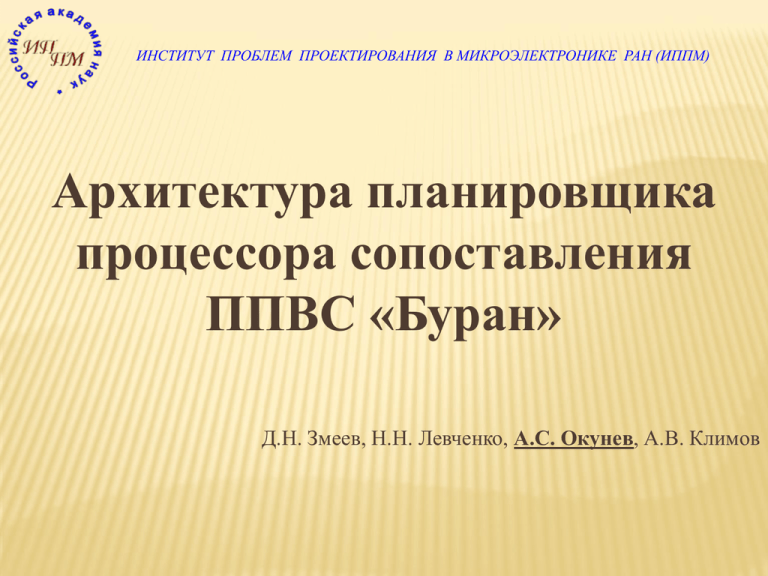

ИНСТИТУТ ПРОБЛЕМ ПРОЕКТИРОВАНИЯ В МИКРОЭЛЕКТРОНИКЕ РАН (ИППМ)

Архитектура планировщика

процессора сопоставления

ППВС «Буран»

Д.Н. Змеев, Н.Н. Левченко, А.С. Окунев, А.В. Климов

МОДЕЛЬ ВЫЧИСЛЕНИЙ ППВС «БУРАН»

С УПРАВЛЕНИЕМ ПОТОКОМ ДАННЫХ С ДИНАМИЧЕСКИ

ФОРМИРУЕМЫМ КОНТЕКСТОМ

Программа на DFL = набор узлов

M1(x1,x2){7,6} пакет

…

node M1(a,b) {i,j}

begin

…

a*b –> M2.c{i+1,j};

…

end

…

программа узла

Ассоциативная память

заголовок

узла

x4–> M1.b{9,4}

ожидание

«парного»

токена

токены

x3–>M2.c{8,6}

x2–> M1.b{7,6}

Сопоставление

токенов (при

одинаковом

контексте)

x1–>M1.a{7,6}

i

node M1(a,b){i,j}

имя

узла

входы

узла

контекст

узла

формирование и

посылка

токена

j

формирование

пакета

пакет M1(x1,x2){7,6}

поступает на

вход узла

2

БАЗОВАЯ АРХИТЕКТУРА ПАРАЛЛЕЛЬНОЙ ПОТОКОВОЙ

ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ «БУРАН»

ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ

токен

ИУ 0

ВЫЧИСЛИТЕЛЬНЫЙ МОДУЛЬ

токен

токен

...

пакет

ИУ m-r

ИУ r-1

токен

пакет

...

ИУ m-1

пакет

внутренний коммутатор пакетов

внутренний коммутатор пакетов

ПС 0

...

пакет

пакет

пакет

токен

...

ПС k-1

пакет

ПС n-k

токен

внутренний коммутатор токенов

токен

пакет

...

ПС n-1

токен

внутренний коммутатор токенов

ЯДРО

ЯДРО

коммутатор токенов

3

АРХИТЕКТУРА ПЛАНИРОВЩИКА

ПРОЦЕССОРА СОПОСТАВЛЕНИЯ

Таблица

ПМ (ВЭ)

Устройство управления

планировщиком процессора

сопоставления

Блок сбора

статистики

память сопоставления

токены

из КМТ

Входной

буфер

токенов

Блок

хэшфункции

ПМ (ВЭ)

Узел

анализа и

установки

статуса

токена

Память отложенных

токенов

Память

ключей

Память

токенов

Формирователь

пакетов

пакеты

в ИУ

Многоуровневая внешняя память токенов

4

ОСНОВНЫЕ ФУНКЦИИ ПЛАНИРОВЩИКА

ПРОЦЕССОРА СОПОСТАВЛЕНИЯ

установка начальных физических адресов областей откачиваемых и остановленных токенов в многоуровневой внешней

памяти токенов (ВПТ), причем для каждого временного этапа (подмножества) откачиваемых и останавливаемых токенов

имеется своя область ячеек в ВПТ;

распределение свободных страниц ВПТ;

поддержка операционной системы с точки зрения распределение ресурсов ВПТ и связи ВПТ с дисковой памятью;

сбор статистики по выполняемым задачам:

анализ и фиксация количества свободных ячеек в АПК;

мониторинг интенсивности формирования пакетов по каждому этапу;

мониторинг интенсивности прихода токенов на вход АПК по каждому этапу;

анализ загрузки буфера готовых пакетов по каждому этапу;

выполнение ротации задач и подзадач;

проверка активности задач, реализация функции останова задач.

5

ОБЩИЙ АЛГОРИТМ РАБОТЫ ПЛАНИРОВЩИКА

ПРОЦЕССОРА СОПОСТАВЛЕНИЯ

6

ИНСТИТУТ ПРОБЛЕМ ПРОЕКТИРОВАНИЯ В МИКРОЭЛЕКТРОНИКЕ РАН (ИППМ)

Спасибо за внимание!