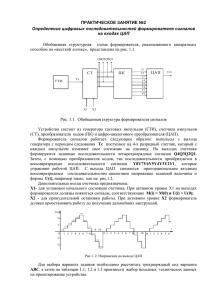

Восьмиразрядный сегментный цифро-аналоговый преобразователь с повышенной скоростью преобразования

реклама

Восьмиразрядный сегментный цифро-аналоговый преобразователь с повышенной скоростью преобразования М.С. Енученко, Д.В. Морозов, М.М. Пилипко Варианты построения ЦАП Унарная архитектура Бинарная архитектура 2 Цель и задачи Цель: разработка восьмиразрядного параллельного цифроаналогового преобразователя с повышенной скоростью преобразования. Задачи: • Разработка и моделирование ЦАП; • Разработка кристалла микросхемы ЦАП; • Экспериментальное исследование образцов микросхемы. 3 Структура сегментного восьмиразрядного ЦАП Бинарный сегмент D0 D1 D2 D3 I0 2I0 4I0 8I0 Iвых D4 D5 D6 D7 Термометрический дешифратор Унарный сегмент 15 x 16I0 4 Коммутируемый источник тока 𝑈𝐶И1 𝐼1 = 2𝑘1 · 𝑈ЗИ1 − 𝑈0 − 𝑈𝐶И1 2 I0 𝐼2 = 2𝑘2 · 𝑈ЗИ2 − 𝑈0 UD 1 𝑊𝑖 𝑘𝑖 = μ𝐶0 2 𝐿𝑖 2 М2 𝑈ЗИ1 = 𝑈СМ Uсм 𝑈ЗИ2 = 𝑈𝐷 − 𝑈𝐶И1 M1 𝐼1 = 𝐼2 = 𝐼0 𝐼0 = + 2 𝑈СМ − 𝑈0 2 𝑘2 𝑘 1+ 2 𝑘1 2 · 𝑘2 1− 𝑘1 + 2 𝑈𝐷 − 𝑈СМ 𝑈𝐷 − 𝑈0 𝑈СМ − 𝑈0 2 − 2 𝑘2 𝑘1 − 2 𝑈𝐷 − 𝑈0 · 𝑈СМ − 𝑈0 𝑈𝐷 − 𝑈0 2 + − 2 𝑈𝐷 − 𝑈0 𝑈СМ − 𝑈0 5 4-х разрядный термометрический дешифратор с параллельным формированием выходных функций 𝑌1 = 𝑋4 + 𝑋3 ∙ 𝑋2 + 𝑋1 𝑌2 = 𝑋2 + 𝑋3 + 𝑋4 𝑌3 = 𝑋1 ∙ 𝑋2 ∙ 𝑋3 + 𝑋4 𝑌4 = 𝑋3 + 𝑋4 𝑌5 = 𝑋1 ∙ 𝑋3 ∙ 𝑋4 + 𝑋3 ∙ 𝑋4 + 𝑋2 𝑌6 = 𝑋4 + 𝑋3 ∙ 𝑋4 + 𝑋2 𝑌7 = 𝑋1 + 𝑋4 + 𝑋4 + 𝑋3 ∙ 𝑋4 + 𝑋2 𝑌9 = 𝑋1 ∙ 𝑋4 ∙ 𝑋4 ∙ 𝑋2 + 𝑋3 𝑌10 = 𝑋4 ∙ 𝑋2 + 𝑋3 𝑌11 = 𝑋1 + 𝑋3 + 𝑋4 ∙ 𝑋2 + 𝑋3 𝑌12 = 𝑋3 ∙ 𝑋4 𝑌13 = 𝑋1 + 𝑋2 + 𝑋3 ∙ 𝑋4 𝑌14 = 𝑋2 ∙ 𝑋3 ∙ 𝑋4 𝑌15 = 𝑋4 ∙ 𝑋3 + 𝑋2 ∙ 𝑋1 𝑌8 = 𝑋4 6 Блоки термометрического дешифратора Блок А 𝑌1 = 𝑋4 + 𝑋3 ∙ 𝑋2 + 𝑋1 𝑌2 = 𝑋4 + 𝑋3 + 𝑋2 𝑌3 = 𝑋2 ∙ 𝑋1 ∙ 𝑋4 + 𝑋3 𝑌4 = 𝑋4 + 𝑋3 𝑌15 = 𝑋4 ∙ 𝑋3 + 𝑋2 ∙ 𝑋1 𝑌14 = 𝑋4 ∙ 𝑋3 ∙ 𝑋2 𝑌13 = 𝑋2 + 𝑋1 + 𝑋4 ∙ 𝑋3 𝑌12 = 𝑋4 ∙ 𝑋3 𝑌5 = 𝑋1 ∙ 𝑋3 ∙ 𝑋4 + 𝑋3 ∙ 𝑋4 + 𝑋2 𝑌6 = 𝑋4 + 𝑋3 ∙ 𝑋4 + 𝑋2 𝑌7 = 𝑋1 + 𝑋4 + 𝑋4 + 𝑋3 ∙ 𝑋4 + 𝑋2 𝑌11 = 𝑋1 + 𝑋3 + 𝑋4 ∙ 𝑋2 + 𝑋3 𝑌10 = 𝑋4 ∙ 𝑋2 + 𝑋3 𝑌9 = 𝑋1 ∙ 𝑋4 ∙ 𝑋4 ∙ 𝑋2 + 𝑋3 𝑌8 = 𝑋4 Блок Б 7 Топология 4-х разрядного термометрического дешифратора Блок А Блок Б 8 Размещение блоков дешифратора 9 Структура топологии ЦАП 10 Топология ЦАП 11 Топология ЦАП с кольцом защиты 12 Моделирование характеристик 13 Моделирование характеристик 14 Основные характеристики Характеристика Моделирование Топология с кольцом электростатической Топология защиты Шаг преобразования, мВ 1,27 1,26 DNL, МЗР 0,13 0,13 INL, МЗР 0,85 1,05 Ширина диапазона выходных напряжений, мВ 323 321 5,7 5,6 1000 50 Средняя потребляемая мощность, мВт Скорость преобразования, Мвыборок/с 15 Микрофотография кристалла микросхемы 16 Характеристика преобразования 17 График дифференциальной нелинейности 18 График интегральной нелинейности 19 Отклик выходного сигнала 20 Спектр гармонического сигнала 21 Результаты измерений Характеристика Измерения Шаг преобразования, мВ 1,21 DNL, МЗР 0,47 INL, МЗР 1,09 Ширина диапазона выходных напряжений, мВ 307 Средняя потребляемая мощность, мВт 6,3 Скорость преобразования, Мвыборок/с 20 22 Сравнение с другими работами Работа Год Разрядность Сегменты Скорость преобразования, Мвыборок/с INL, МЗР DNL, МЗР Напряжение питания, В Процесс, нм Потребляемая мощность, мВт [8] [9] 2011 8 6 ун. + 2 бин. 2008 8 5 ун. + 3 бин. Данная работа 2013 8 4 ун. + 4 бин. 200 500 1000 0,27 0,08 5,0 500 117 0,33 0,14 1,8 180 ‒ 1 0,47 1,8 180 6,2 23 Сравнение с другими работами Характеристика Год Технология Пересчитанная активная площадь, мкм2 [19] [21] [22] 2009 2009 2004 0,18 0,25 Предложенное решение 2013 0,35 0,18 4400 9000 8000 1764 24 Заключение При разработке параллельных ЦАП использование сегментной архитектуры. целесообразно В качестве примера разработан параллельный 8-ми разрядный сегментный ЦАП на источниках тока: 4 старших разряда унарный сегмент, 4 младших – бинарный. Изготовлены тестовые кристаллы микросхемы. Проведены измерения разработанного ЦАП. Получены следующие характеристики: DNL – 0,47 МЗР; INL – 1 МЗР; скорость преобразования 1000 Мотсчётов/с. По сравнению с известными реализациями достигнуто увеличение быстродействия в 2 раза и уменьшение площади в 2,5 раза. 25