Физическая реализация элементов памяти

реклама

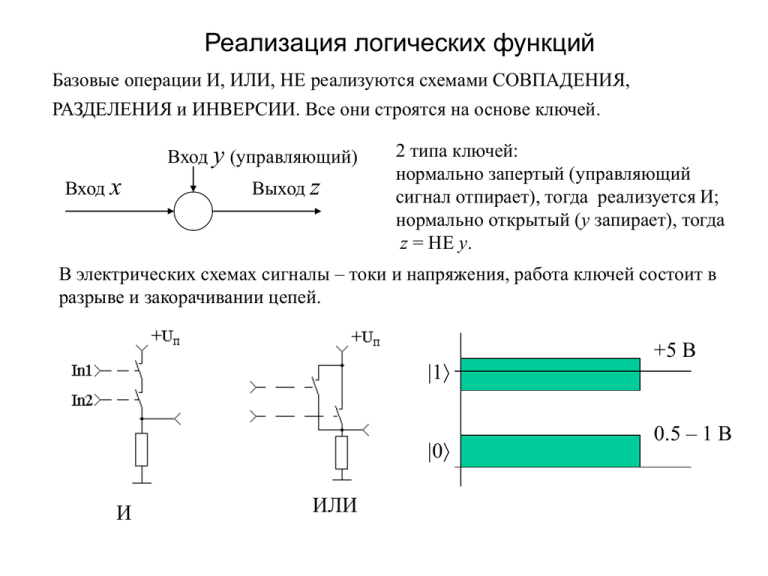

Реализация логических функций Базовые операции И, ИЛИ, НЕ реализуются схемами СОВПАДЕНИЯ, РАЗДЕЛЕНИЯ и ИНВЕРСИИ. Все они строятся на основе ключей. Вход у (управляющий) Вход х Выход z 2 типа ключей: нормально запертый (управляющий сигнал отпирает), тогда реализуется И; нормально открытый (у запирает), тогда z = НЕ у. В электрических схемах сигналы – токи и напряжения, работа ключей состоит в разрыве и закорачивании цепей. +5 В |1 |0 И ИЛИ 0.5 – 1 В Диодно-транзисторная логика (ДТЛ) Простейший путь реализации логических элементов в электронике – на диодах («незавершенный» ключ). |1 х1 х2 Для реализации инвертора у нужен активный элемент у (транзистор). В данном случае он работает как управляемое |0 х2 х1 сопротивление эмиттеру не |0, если один из коллектор. у = |1 только если оба диодов открыт (х = |1); диода заперты (х = |1); ИЛИ И |1 у х |0 НЕ Транзисторно-транзисторная логика (ТТЛ) Транзисторная реализация логики на ключах R2 = 0: |1 R1 у1 х1 х2 у2 R2 у1 = |0, если хотя бы один из ключей открыт у1 = |1, если оба закрыты R1 = 0: у2 = |1, если хотя бы один из ключей открыт у2 = |0, если оба закрыты Реализуется функция ИЛИ либо ИЛИ-НЕ |0 R2 = 0: |1 R1 у1 х1 у1 = |1, если хотя бы один из ключей закрыт у1 = |0, если оба открыты R1 = 0: у2 = |0, если хотя бы один из ключей закрыт у2 = |1, если оба открыты х2 у2 R2 |0 Реализуется функция И либо И-НЕ Выходы у1 и у2 взаимно инверсны Комплементарные МОП (КМОП) транзисторы р-канальный n-канальный (запирается высоким VG) (запирается низким VG) Логика на КМОП транзисторах Активная нагрузка |1 R1 х1 у у х1 х2 х2 |1 Активная нагрузка R1 х1 х2 Вместо нагрузочного резистора – комбинация ПТ. Когда на входе х1 или х2 высокий потенциал, R1 = . Даже при замыкании ключей в выходной цепи ток не течет. у х1 у ИЛИ-НЕ х2 И-НЕ |0 Физическая реализация элементов памяти Элементы памяти - это те же логические элементы, которые вдобавок обладают состоянием (т.е. на выходе изначально присутствует сигнал, соответствующий некоторому логическому состоянию). a t f a t t , x t Состояние элемента памяти упр. Триггер на двух инверторах: 2 устойчивых состояния. Бистабильность Память может быть построена на тех же элементах, что и логика Разные требования к разным типам памяти (оперативная, регистровая, кэш-память, внешняя) разные физические принципы. История: память на ферритовых сердечниках. Окислы железа с прямоугольной петлей гистерезиса I1 H1, B1 H2, B2 I2 Управление, запись, считывание размер 0.1 мм; Матричная организация памяти: Коммутация N2 ячеек требует 2N проводов. Разрушающее считывание. Время цикла около 1 мкс; число колечек в одной матрице до нескольких десятков тысяч. плотность записи - десятки бит/мм2 Полупроводниковые ЗУ Логика на управляемых ключах: состояние ключа влияет на выполняемую функцию. Любой логический элемент с управляемым состоянием = элемент памяти (ЭП). Но когда устройство работает как ЭП, к нему предъявляются другие требования: удобство обращения, записи и считывания, эффективный доступ и надежное хранение. Отсюда - конструктивные отличия. Виды памяти: С точки зрения адресная (с произвольным доступом) - RAM; доступа и с последовательным доступом; организации стековая, буферная; оперативная, т.е. всегда готовая к использоС точки зрения ванию, непосредственно связанная с функциональной процессором и работающая в его темпе; гибкости постоянная (содержимое не меняется или меняется редко и в особых условиях) - ROM Оперативная статическая С точки зрения память динамическая длительности хранения Матричная организация постоянной памяти (ROM). Ячейки в узлах координатной сетки, вертикальные (ВЛ) и горизонтальные (ГЛ) линии не соединяются. Потенциал ВЛ близок к |0; если же ВЛ и ГЛ соединены через диод, то при подаче высокого напряжения на ГЛ через резистор потечет ток, а потенциал ВЛ станет |1. |1 |0 |1 |0 |0 |0 |1 |0 Вместо диодов может быть матрица |1 транзисторов. Высокий потенциал ГЛ открывает транзисторы, и |1 поступает на ВЛ. Где транзистор отсутствует, там |0. ... Технологически удобно ставить транзисторы везде. Там, где |0, утолщенный слой диэлектрика. Для хранения стандартной широко |1 используемой информации Более совершенный вариант: программируемая постоянная память (PROM) Устранение или создание специальных перемычек: Пробой одного из диодов; Плавкие перемычки; УФ облучение. Многократное программирование: МНОП и плавающий затвор (5 нм) На границе нитрида и окисла Дополнительный электрод ловушки внутри слоя окисла Накопленный заряд экранирует затвор и изменяет напряжение переключения или Ме а) напряжение на затворе равно нулю, ловушки не заполнены; б) запись информационного заряда (напряжение 20 В); в) стирание информационного заряда 1 — Исходная ВАХ,VT = 0,6 В. Заряд в диэлектрике отсутствует; 2 — Состояние «закрыто»,VT = 2,6 В. В диэлектрик записан отрицательный заряд; 3 — Состояние «открыто», V T = –3,2 В. В диэлектрик записан положительный заряд 104 - 106 перезаписей а) напряжение на затворе VGS равно нулю, плавающий затвор не заряжен; б) процесс записи информационного заряда импульсом напряжения +VGS: лавинная инжекция электронов из стоковой области канала МДП транзистора. в) МОП ПТ при нулевом напряжении на затворе в режиме хранения информационного заряда. Если заряд ПЗ < 5000 е, это |1, если > 30000, это |0. Ячейки с |0 имеют порог переключения 5 В, ячейки с |1: 3,1 В. Стирание: 0 на затвор, высокое напряжение на сток. Необходимо строго контролировать инжекцию, подводить напряжение на определенное время. Сохранность: утечка заряда < 1 е в день. StrataFlash (1997): 2 бита в одной ячейке. 4 стандартных заряда, соответствующих |00, |01, |10, |11; 4 пороговых напряжения Невысокое быстродействие. Используются для внешней памяти (флэш-карты). Быстродействующая оперативная память работает в непосредственном контакте с процессором. Энергозависима (данные хранятся только при включенном питании) Статическая память - на триггерах, которые строятся на КМОП транзисторах линия выборки |1 Dj Dj При высоком потенциале линии выборки ключи открываются. Столбцовые шины подсоединяются к прямому и инверсному входам триггера (считывание). Запись: «навязывание» сигнала столбцов при открытых ключах. «Искусственная» энергонезависимость: резервный источник питания ЗУ Динамические ЗУ: данные хранятся в виде зарядов емкостей МОП структур Самые простые, дешевые, миниатюрные (у статических 6 транзисторов, у динамических 1); плотность записи на порядок выше, чем у статических. ЛЗС ЛЗС Сз SiO2 n+ ЛВ1 ЗЭ ЛВ2 U U1 Сз Cз Cл n+ Cз Сл Сл Поликремний ЛВ Сток никуда не подключен и образует обкладку; другая обкладка - подложка. При записи и считывании транзистор отпирается сигналом ЛВ и либо потенциал ЛЗС передается на Сз, либо наоборот. ЛЗС предварительно подзаряжается до потенциала U1. После замыкания ключа U1 U1 U Сз << Сл Считывание разрушающее; Время хранения: мс Перcпективы: TiO2 (в 20 раз больше ) Быстродействие оперативной памяти DRAM всегда значительно медленнее процессора В 90-е годы - время доступа 60 нс, которое равнозначно тактовой частоте 16,7 МГц В 2002 году появилась память DDR с частотой 333 МГц, которая была увеличена в 2003 году до 400 МГц. В 2004 году была представлена память DDR2 с рабочей частотой 400 и 533 МГц. Static RAM обычно интегрируется в состав процессора и работает в качестве кэш-памяти. Быстродействие такое же, как и у транзисторов процессора: при 3.4 ГГц - 0.29 нс 1 МБ оперативной памяти > 8 млн. транзисторов; 1 МБ кэш-памяти > 48 млн. транзисторов.