90531_ctsu_sui_5

реклама

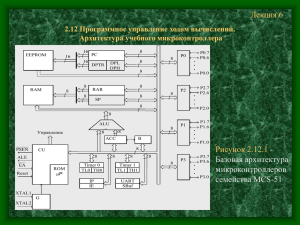

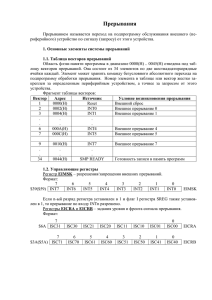

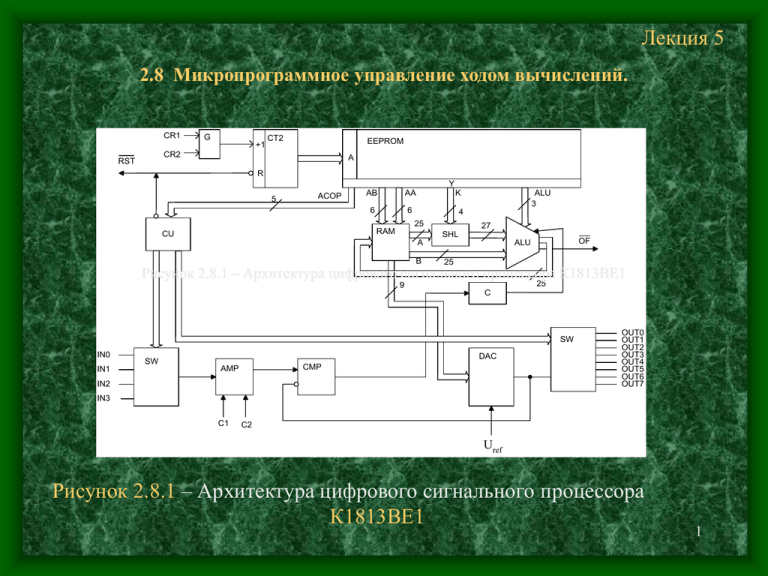

Лекция 5 2.8 Микропрограммное управление ходом вычислений. CR1 G +1 CT2 EEPROM CR2 RST A R Y 5 ACOP AB AA 6 6 K 4 25 RAM CU ALU 3 27 SHL A B OF ALU 25 Рисунок 2.8.1 – Архитектура цифрового сигнального процессора К1813ВЕ1 25 9 C SW IN0 IN1 SW DAC CMP AMP IN2 OUT0 OUT1 OUT2 OUT3 OUT4 OUT5 OUT6 OUT7 IN3 C1 C2 Uref Рисунок 2.8.1 – Архитектура цифрового сигнального процессора К1813ВЕ1 1 Лекция 5 Архитектура цифрового сигнального процессора Выбор канала и запоминание Uвх Шаг 1 Аналоговоцифровое преобразование Uвх=>DAR Шаг 2 9 Цифровая обработка сигнала Шаг 3 25 Вывод кода в ЦАП (DAC) ЦАП Шаг 4 Вывод в заданный канал Шаг 5 Рисунок 2.8.3 - Типовая последовательность шагов алгоритма цифровой обработки сигнала Общая характеристика процессора. КМ1813ВЕ1-однокристальная ЭВМ с встроенным перепрограммируемым ПЗУ программы с УФ стиранием и аналоговым устройством ввода-вывода. Кристалл выполнен по n-МОП технологии и помещен в металлокерамический, 28-выводный корпус (2121.28-6). 2 Лекция 5 2.9 Управление цифровой частью процессора. Реализация операции умножения на постоянный коэффициент Таблица 2.9.1 Коды операций, выполняемых сдвигателем Цифровая часть сигнального процессора К1813ВЕ1 состоит из трех управляемых блоков: двухпортового ОЗУ, аппаратного сдвигателя SHL и арифметико-логического устройства ALU Обозначе ние операции L02 Код операци и 1101 Сдвиг числа L01 1110 21 R00 1111 20 R01 0000 2-1 R02 0001 2-2 … … … R09 1000 2-9 R10 1001 2-10 R11 1010 2-11 R12 1011 2-12 R13 1100 2-13 22 3 Лекция 5 2.10 Управления аналоговой частью процессора. Реализация аналогоцифрового преобразования Управление аналоговой частью выполняется заданием кода операции в поле ACOP микрокоманды. Пятиразрядное поле ACOP позволяет задать 32 различные команды. Команды OUT(P), Р = 0 … 7 управляют выходным аналоговым переключателем и позволяют вывести выходное напряжение DAC на выход с требуемым номером Р. Команды CND(N), N = 0 … 8 , задают выполнение условной команды в цифровой части по биту N цифро-аналогового преобразователя. Команда NOP задает пропуск выполнения команды в аналоговой части. Команда END задает конец программы. 4 Лекция 5 2.11. Микропрограммная реализация регистрового способа вычислений. Распараллеливание вычислений X X1 RG :6 D Q C X2 RG D X3 RG D Q C C X4 RG D Q Q C X5 RG D X6 RG D Q SM Q C C T SM SM SM SM Y Рисунок 2.11.1 Схема вычисления сглаженного значения сигнала Для сглаживания сигнала выполняется усреднение: у(m) = (x1(m)+x2(m)+x3(m)+x4(m)+x5(m)+x6(m))/ 6 , где: х1(m), …, x6(m) – шесть последовательных отсчетов входного сигнала. Ниже приведена часть текста программы работы цифрового сигнального процессора : № ячейки ACOP 0 IN(1) 0 0 R00 LDA 1 IN(1) 0 0 R00 LDA AB AA K ALF Комментарий Ввод аналогового сигнала 5 Лекция 6 2.12 Программное управление ходом вычислений. Архитектура учебного микроконтроллера 16 EEPROM 16 16 8 RAM 8 8 PC 8 DPL DPH DPTR P0 . . . 8 8 8 SP P0.7 P0.6 P0.0 8 RAR 8 8 P2 . . . 8 P2.7 P2.6 P2.0 8 ALU Управление 8 8 8 8 8 ALE ROM Р Reset P1.7 P1.6 P1.0 CU EA . . . B ACC PSEN P1 8 8 Timer 0 TL0 TH0 Timer 1 TL1 TH1 IP IE UART SBuf 8 8 P3 . . . P3.7 P3.6 P3.0 Рисунок 2.12.1 Базовая архитектура микроконтроллеров семейства MCS-51 XTAL1 G XTAL2 6 2.13. Программная реализация табличного способа вычисления Вычисления значения нелинейной функции выполняется с помощью 5 команд и требует 12 мкс времени при реализации программы на типовом контроллере MCS-51 с частотой кварцевого резонатора 12 МГц. ROM1 X 12 8 7 11 A 4 Ki 4 SUM Q x 8 Y ROM2 A Q 7 Рисунок 2.13.1 - Схема аппаратной реализации табличного вычислителя в рассматриваемой схеме реализованы вычисления по следующим уравнениям: X = Xi + ∆х, Y = f( Xi ) + Ki * ∆х , где: f( . ) - заданная нелинейная функция. 7 2.13.2. Реализация генератора функции времени Для примера: необходим генератор задающего воздействия y = sin ( w*t) , частота воздействия 10 Гц, т.е. w = 62,8 1/с. G fк +1 CT2 A Q R ROM 7 N 10 Q Y Рисунок 2.13.2 - Генератор функции времени для задания периода квантования сигналов используется механизм обработки прерываний таймеров, а программа генерации значений функции пишется, как программа обработки прерывания одного из таймеров. 8 Реализация генератора функции времени Начало Инициализация Требование прерывания ТС0 Запрет прерываний Установка режима таймера 0 Запрет прерываний Обработка прерывания Чтение Y=f(x) из буфера Вывод Y Запись периода прерывания TС0 N 100 N=0 N=N+1 N=0 Разрешение прерываний Разрешение прерываний RTI Различные сервисные программы Основная задача Рисунок 2.13.3 - Структура программы генератора функции времени 9 2.14 Программная реализация регистрового способа вычисления Пусть необходимо реализовать устройство, вычисляющее среднее значение по четырем последовательно измеряемым значениям входной переменной х(n): y(nТ) = [x(nТ-T) + x(nТ-2Т) + x(nТ-3Т) + x(nТ-4Т)]/ 4, где: n - дискретное время, Т - заданный период квантования сигнала во времени. 8 X(nT) X1(nT) RG 8 D 8 Q SM X2(nT) Q 8 RG 8 RG D D RG D Q X3(nT) C C C 8 Q X4(nT) 9 SM Y(nT) 8 10 :4 C T SM 9 Рисунок 2.14.1 - Схема устройства, аппаратно реализующего регистровый способ вычислений 10 Программная реализация регистрового способа вычисления Начало Инициализация Запрет прерываний Кофигурирование линии P3.2 на ввод сигнала Int0 Запись вектора прерывания Int0 Разрешение прерываний Int0 Разрешение прерываний Требование прерывания Int0 Запрет прерываний Чтение x(nT) через порт Р1 Синхронный ввод и обработка информации Вывод Y(nT) через порт Р2 Обновление информации в регистрах Вычисление нового значения Y Разрешение прерываний Различные сервисные программы RTI Асинхронный процесс Рисунок 2.14.2 - Блок-схема программы, реализующей регистровый способ вычислений.11 Цифровая техника систем управления В.И. Бойков, С.В. Быстров, В.В. Григорьев Учебное пособие 12