ST(0)

реклама

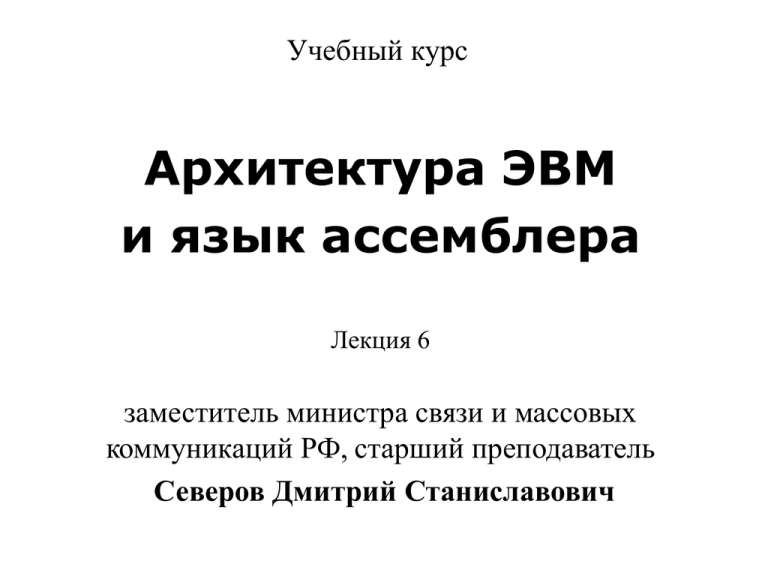

Учебный курс Архитектура ЭВМ и язык ассемблера Лекция 6 заместитель министра связи и массовых коммуникаций РФ, старший преподаватель Северов Дмитрий Станиславович Модель «сопроцессора» FPU Операция 9 0 Управление Состояние Теги стека 15 0 Указатель команды Указатель данных 47 0 R7 R6 R5 R4 R3 R2 R1 R0 Стек Данных 79 • • • • Обмен c CPU через память Команду выбирает CPU Данные выбирает CPU CPU ждёт FPU – FWAIT/WAIT ST(4) ST(3) ST(2) ST(1) ◄ST(0) ST(7) ST(6) ST(5) 0 79 1.0 2.0 3.0 ST(1) ◄ST(0) ST(7) 0 2 Команды FPU • Мнемоники – Первая – F – Вторая – тип операнда в памяти • i - целое двоичное • b - целое десятичное • пусто – вещественное – Последние p – выталкивание результата – (Пред)последняя r – реверс операндов • Форматы – Стековый – Регистровый – С памятью FADD FADD ST(1),ST FADD mem64real 3 Пример работы с FPU TITLE FPU Expression Evaluation (Expr.asm) ;(6.0*2.0)+(4.5*3.2) или 6.0 2.0 * 4.5 3.2 * + INCLUDE Irvine32.inc .data array REAL4 6.0, 2.0, 4.5, 3.2 dotProduct REAL4 ? .code main PROC finit ; инициализировать FPU fld array ; втолкнуть 6.0 в стек fmul array+4 ; ST(0) = 6.0 * 2.0 fld array+8 ; втолкнуть 4.5 в стек fmul array+12 ; ST(0) = 4.5 * 3.2 fadd ; ST(0) = ST(0) + ST(1) fstp dotProduct ; вытолкнуть результат exit main ENDP END main 4 Сводка назначений команд FPU • • • • • • • • • • • • Загрузка, Выгрузка Абсолютная величина Округление Выделение мантиссы/порядка Сравнение Сложение, Вычитание Умножение, Масштабирование Частное, остаток от деления Косинус, синус Тангенс, арктангенс Потенциирование Логарифмирование • • • • • • • • • Инициализация Сброс флагов Перемотка стека Освобождение регистра Обмен регистров стека Пустое Ожидание Сохранение Восстановление 5 Архитектура ЭВМ: Литература • Литература – Жмакин А.П. Архитектура ЭВМ. • ISBN 5-94157-719-2 – Королёв Л.Н. Архитектура ЭВМ. • ISBN 5-89176-274-9 – Таненбаум Э. Архитектура компьютера 4-е изд. • ISBN 5-318-00298-6 6 Иерархия языков и акторов • • • • • • • • • • Общечеловеческие • Профессиональные • • Спецификаций • Программирования • Системных вызовов • Машинного кода • Микрокоманд • Цифровых сигналов • Аналоговых сигналов Изменений в материалах • Субъекты рынка Решатели задач Исполнители алгоритмов Виртуальные машины Операционная система Система команд Микроархитектура Цифровые схемы Аналоговые схемы Фрагменты материалов 7 Иерархия языков и акторов • • • • • • • • • • Общечеловеческие • Субъекты рынка Профессиональные •Транслируются Решатели задач • Исполнители алгоритмов Спецификаций • Виртуальные машины Программирования • Операционная система Системных вызовов • Система команд Машинного кода Интерпретируются • Микрокоманд Микроархитектура • Цифровые схемы Цифровых сигналов • Аналоговые схемы Аналоговых сигналов Изменений в материалах • Фрагменты материалов 8 Иерархия событий в ЭВМ • • • • • • • • • Взаимодействие ВМ (в ВС) Взаимодействие процессов (в ОС ВМ) Взаимодействие потоков команд в процессе Выполнение потока команд Выполнение операции системы команд Выполнение микрооперации Срабатывание цифровых элементов Переключение аналоговых элементов Изменение в материалах 9 Роль архитектуры системы команд • Алгоритм Программы • Прикладная программа • Транслятор, ассемблер, ОС Ключевое соглашение • Архитектура системы команд • Сложные блоки: АЛУ, УУ, память, УВВ Аппаратура • Типовые цифровые блоки: Логические схемы. • Структурная основа: цифровые элементы • Физ. основа: (полу)проводники, изоляторы 10 Структурная основа: Логические схемы • Ячейки хранения. Регистры. Память. – Статические, Динамические – Неадресуемые, Прямоадресуемые, Контекстноадресуемые • Логические ячейки. Комбинационные схемы – Элементарные: И, ИЛИ, НЕ; И-НЕ; ИЛИ-НЕ; ??? – Составные: полусумматор, сумматор, мультиплексор, дешифратор, сдвигатель, умножитель … • Соединения. Шины. – – – – Последовательные, Параллельные Двустабильные, Трехстабильные, Многостабильные Синхронные, Асинхронные Проводные, Беспроводные • Разрядность 4,8,16(20,24),32,(48),64,(128) 11 Иерархия данных и операций Макро вход/ввод макрооперация макро выход/вывод Вход/ввод Данные Операции Операция Результаты Выход/вывод 12 Некоторые модели вычислений Однопотоковая фон Неймана потоковая (синхронная) управляемая потоком данных многопотоковая 13 Машина с хранимой в памяти программой. • Адресность – Информация вычислительного процесса сохраняется в одном или нескольких пронумерованных массивах ячеек – В любой момент доступна любая ячейка • Программное управление – Алгоритм вычислений представлен в виде программы -упорядоченной последовательности команд, подлежащих обработке • Двоичное кодирование – Вся информация кодируется элементами с двумя состояниями – Каждый тип информации кодируется последовательностью определённого формата • Однородность памяти – Команды и данные хранятся в общей памяти и неразличимы по способу хранения – Команды и данные различаются способом использования – Команды модифицируются, и являются результатом трансляции 14 Близкие архитектуры Принстонская Основная память ЦП ЦП АЛУ Гарвардская Память Память данных команд УУ Порты ввода/вывода АЛУ УУ Порты ввода/вывода 15 О структуре и классификации АЛУ УУ Регистры Память УBB УBB УBB Среда взаимодействия АЛУ АЛУ АЛУ УУ Регистры Память УBB УBB УBB Среда взаимодействия УУ АЛУ УУ Регистры Регистры Память УBB УBB УBB Среда взаимодействия память – Один поток команд – Один поток данных • SIMD – Один поток команд – Много (потоков) данных • MISD – Много потоков команд – Один поток данных • MIMD память АЛУ УУ АЛУ УУ Регистры Регистры • SISD Память Среда взаимодействия УBB УBB УBB – Много потоков команд – Много потоков данных 16 Пример: Аккумуляторная ВМ Селектор операции 1-й операнд Аккумулятор 2-й операнд Блок обработки данных результат Дешифратор операции Селекторы источника и назначения Код операции Регистр команды Основная память 17 Аккумуляторная ВМ. Детали. Устройство управления Устройство обработки данных Сигналы управления ⋅⋅⋅ Микропрограммный автомат Счётчик команд Указатель стека Регистр 2-го операнда Операционный блок Дешифратор кода команд Регистр команды Операц. Адресная. часть часть Регистр Признаков Аккумулятор Порт ввода Дешифратор В/В Регистр адреса Регистр 1-го операнда Порт вывода Регистр данных Модуль ввода вывода Адрес Данные Оперативная память Периферийное устройство 18