описание системы команд микропроцессора кр580

реклама

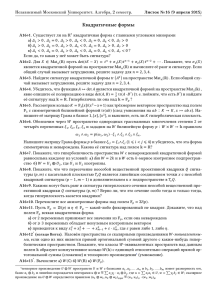

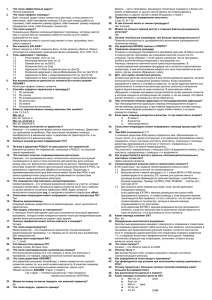

ОПИСАНИЕ СИСТЕМЫ КОМАНД МИКРОПРОЦЕССОРА КР580 При описании системы команд используются следующие сокращения: o () – означают содержимое регистра или ячейки памяти; o [] – содержимое регистровой пары или двух смежных ячеек памяти, используемых для указания адреса размещения операнда; o R, RI – регистры A, B, C, D, E, H, L, M (виртуальный регистр); o YZ – регистровые пары BC, DE, HL или указатель стека SP; o YZ* – регистровые пары BC, DE, HL; o M – ячейка памяти, адрес которой хранится в регистровой паре HL; o F (Flags register) – регистр флагов; o PC (program counter) – регистр счетчика команд; o SP (stack pointer) – регистр указателя стека; o PSW (program state word) – слово состояния программы (содержимое регистров A и F). o N – номер порта ввода-вывода; o D16 – двухбайтовый операнд данных; o D8 – однобайтовый операнд данных; o A16 – двухбайтовый операнд адреса. Для фиксирования определенных ситуаций, возникающих в процессе выполнения машинных команд, применяется содержимое регистра флагов F. Формат регистра флагов для процессора КР580ВМ80А приведен в таблице П1. Таблица П1 Номер бита Обозначение 7 Формат регистра флагов F 6 5 4 3 2 1 0 S Z P 1 C 0 AC 0 S (Sign) – признак знака, устанавливается в 1, если результат выполнения команды отрицателен. Единица в старшем разряде соответствует отрицательному числу в дополнительном коде. Z (Zero) – признак нуля, устанавливается в 1, если результат выполнения операции нулевой. AC (Auxiliary Carry) – признак вспомогательного переноса, устанавливается в 1, если происходит перенос из младшей тетрады в старшую. P (Parity) – признак четности, устанавливается в 1, если число единиц в двоичном коде четное. C (Carry) – признак переноса, устанавливается в 1, если в результате выполнения операции с двумя 8-разрядными двоичными числами результат не помещается в разрядной сетке. Влияние выполнения машинных команд на состояние регистра флагов отображено в таблице П2. Таблица П2 Влияние выполнения машинных команд на состояние регистра флагов КР580 Команда Регистр флагов Команда Регистр флагов S Z AC P C S Z AC P C ACI D8 ADC D8 ADD R ADI R ANA R + + + + + + + + + + + + + + U + + + + + + + + + + MVI R, D8 NOP ORA R ORI D8 OUT N + + - + + - 0 0 - + + - 0 0 - ANI D8 + * C_CON A16 - + - U - + + - - PCHL POP PSW + + + + + CALL A16 CMA - - - - - PUSH PSW PUSH YZ* - - - - - CMC CMP R CPI D8 DAA DAD YZ DCR R DCX YZ DI EI HLT IN N INR R INX YZ J_CON A16 JMP A16 LDA A16 LDAX R LHLD A16 LXI YZ, D16 MOV R, RI + + + + + - + + + + + - + + + + + - + + + + + - + + + + + + - R_CON RAL RAR RET RLC RRC RST NUM SBB R SBI D8 SHLD A16 SPHL STA A16 STAX R STC SUB R SUI D8 XCHG XRA R XRI D8 XTHL + + + + + + + - + + + + + + + - + + + + + 0 0 - + + + + + + + - + + + + + + + 1 + + 0 0 - В таблице П2 знак «+» означает, что выполнение данной команды оказывает влияние на состояние соответствующего флага, знак «-» – состояние флага остается неизменным, «1» – данный флаг устанавливается в единицу, «0» – данный флаг сбрасывается в «0», «U» – состояние данного флага не определено. Мнемоники машинных команд (их условное обозначение) и описание выполняемых ими действий приведены в таблице П3. Таблица П3 Функциональное описание системы команд микропроцессора № группы Назначение Мнемоника Описание команд 1 Команды MOV RI, R (RI)(R) однобайтовых MVI R, D8 (R)D8 пересылок (A)[YZ] LDAX YZ [YZ](A) STAX YZ A16(A) STA A16 (A)A16 LDA A16 2 Команды ввода-вывода IN N (A)(N) OUT N (N)(A) 3 Команды CMC C+ арифметических и STC C1 логических операций с CMA (A)(A) одним операндом DAA десятичная коррекция INR R (R)(R)+1 DCR R (R)(R)-1 INX YZ (YZ)(YZ)+1 DCX YZ (YZ)(YZ)-1 (HL)(DE) 4 Команды обмена XCHG (H)[SP+1] байтами XTHL (L)[SP] Циклический сдвиг 5 Команды сдвига RLC влево содержимого аккумулятора RAL Циклический сдвиг влево через флаг C RRC RAR Циклический сдвиг вправо Циклический сдвиг вправо через флаг C № группы команд 6 Назначение Команды двухбайтовых пересылок данных Продолжение табл. П3 Мнемоника Описание LXI YZ, D16 SHLD A16 (YZ)D16 A16+1(L) A16(H) LHLD A16 (L)A16+1 (H)A16 PUSH YZ POP YZ PUSH PSW 7 Команды арифметических и логических операций с двумя операндами [SP-1](Y) [SP-2](Z) (SP)(SP)-2 (Y)[SP] (Z)[SP+1] (SP)(SP+2) [SP-1](A) [SP-2](F) (SP)(SP)-2 POP PSW (F)[SP] (A)[SP+1] (SP)(SP)-2 SPHL (SP)(HL) ADD R ADC R SUB R SBB R ANA R ORA R XRA R ADI D8 ACI D8 SUI D8 SBI D8 ANI D8 XRI D8 ORI D8 CPI D8 CMP R (A)(A)+(R) (A)(A)+(R)+C (A)(A)-(R) (A)(A)-(R)-C (A)(A)(R) (A)(A)(R) (A)(A)(R) (A)(A)+D8 (A)(A)+D8+C (A)(A)-D8 (A)(A)-D8-C (A)(A)D8 (A)(A)D8 (A)(A)D8 Установка флагов в F по результатам сравнения (A) с D8 или (R) (HL)(HL)+(YZ) DAD YZ № группы команд 8 9 Назначение Специальные команды Команды вызова и возврата из подпрограмм и прерываний Продолжение табл. П3 Мнемоника Описание EI Разрешение прерываний DI Запрет прерываний HLT NOP CALL A16 RET Останов Холостая операция [SP-1][SP-2](PC) (SP)(SP)-2 (PC)A16 (PC)[SP][SP+1] (SP)(SP+2) C_CON A16 При CON=1 [SP-1][SP-2](PC) (SP)(SP)-2 (PC)A16, иначе (PC)(PC)+3 R_CON При CON=1 (PC)[SP][SP+1] (SP)(SP)+2, иначе (PC)(PC)+3 [SP-1][SP-2](PC) (SP)(SP)-2 (PC)A16, где А16=0h,8h,10h,18h, 20h,28h,30h, 38h RST Продолжение табл. П3 № группы команд 10 Назначение Команды передачи управления Мнемоника PCHL JMP A16 J_CON A16 Описание (PC)(HL) (PC)A16 при CON=1 (PC)A16, иначе (PC)(PC)+1(2)(3), в зависимости от длины машинной команды В таблице П1.3 _CON означает часть мнемоники команды, определяющая условие передачи управления вызова и возврата из подпрограммы. _CON в мнемониках команд заменяется на: o nz – если условный переход, вызов или возврат из подпрограммы осуществляется при z=0; o z – если условный переход, вызов или возврат из подпрограммы осуществляется при z=1; o nc – если условный переход, вызов или возврат из подпрограммы осуществляется при c=0; o c – если условный переход, вызов или возврат из подпрограммы осуществляется при c=1; o po – если условный переход, вызов или возврат из подпрограммы осуществляется при p=1; o pe – если условный переход, вызов или возврат из подпрограммы осуществляется при p=0; o p – если условный переход, вызов или возврат из подпрограммы осуществляется при s=0; o m – если условный переход, вызов или возврат из подпрограммы осуществляется при s=1. Далее приводится пример программы, демонстрирующей использование наиболее часто встречающихся команд. При составлении собственных программ рекомендуется придерживаться такой же формы записи. Адрес Мнемоника 8000 MVI A, 1A 8001 8002 8003 8004 8005 Код Комментарий 3E (A)1A; 3E – код команды MVI A, D8 1A 1A – конкретный операнд, подставляемый вместо D8 MOV C, A 4F (C)(A); 4F – код команды MOV C,A, операндов у ней нет, поэтому занимает 1 байт. Сейчас (A)=1A и (С)=1A LXI D, 8200 11 (DE)8200;11 – код команды LXI D, D16 00 8200 – конкретный операнд, 82 подставляемый вместо D16, т.к. младший байт расположен по младшему адресу, 8006 8007 8008 STA 8201 8009 MVI A, C1 800A 800B LDA 8201 800C 800D 800E MVI A, 90 800F 8010 STAX D 8011 LXI D, 8201 8012 8013 8014 LDAX D 8015 INR C 8016 DCR A 8017 INX D 8018 8019 801A 801B 801С 801D 801E 801F 8020 INX D DCX D STAX D LXI H, 0100 XCHG DCX H SPHL 8021 XTHL 32 01 82 3E C1 3A 01 82 3E 90 12 то порядок следования в программе 00 82 (8201)(A); 32 – код команды STA A16 8201 – конкретный операнд, подставляемый вместо А16. По этой команде в ячейку памяти с адресом 8201 записалось содержимое аккумулятора, т.е. (8201)=1А (A)C1 (A)(8201); 3A – код команды LDA A16 8201 – конкретный операнд, подставляемый вместо A16, (A)=1A (A)90 [DE](A); в ячейку памяти с адресом, хранящимся в регистровой паре DE, записывается содержимое аккумулятора, т.е. (8200)=90 11 (DE)8201 01 82 1A (A)[DE]; в аккумулятор из ячейки памяти, адрес которой хранится в регистровой паре, записывается содержимое, т.е. (A)=1A 0C (C)(C)+1, увеличение содержимого регистра С на единицу, т.е. (С)=1B 3D (A)(A)-1, уменьшение содержимого регистра A на единицу, т.е. (A)=19 13 (DE)(DE)+1, увеличение содержимого регистровой пары (DE) на единицу, т.е. (DE)=8202 13 (DE)(DE)+1, (DE)=8203 1B (DE)(DE)-1, (DE)=8202 12 [DE](A), (8202)=19 21 (HL)0100 00 01 EB (DE)(HL), (DE)=0100, (HL)=8202 2B (HL)=8201 F9 (SP)(HL), пересылка содержимого регистровой пары HL в регистр указателя стека (SP)=8201 E3 (H)[SP+1], (L)[SP], обмен информацией между вершиной стека и регистровой парой (HL), т. е. (H)=19, (L)=1A, (8202)=82, (8201)=01 (A)(A)+(H), (A)=32 команда сравнения содержимого аккумулятора со вторым байтом, т.е. (A) сравнивается с 32; сравнение производится посредством вычитания, но результат в А не помещается эта команда условного перехода передала бы управление на адрес 8000, если бы флаг Z=0, т.к. предыдущая команда установила Z=1, то будет выполнена следующая за ней команда с адресом 8028 (A)(A)-32; (A)=0, флаг Z в регистре флагов установился в 1 передаст управление на команду с адресом 8028, если Z=1 8022 ADD H 8023 CPI 32 8024 84 FE 32 8025 JNZ 8000 8026 8027 C2 00 80 8028 8029 802A 802B 802C 802D 802E 802F D6 32 CA 28 80 3C (A)(A)+1; (A)=1 87 (A)(A)+(A);(A)=2 B9 сравнение содержимого аккумулятора с содержимым регистра С; сравнение производится посредством вычитания, результат в аккумулятор не записывается F2 передала бы управление по адресу 8010, если 10 флаг S=0; т.к. (A)=2 и (С)=1B, то (А)-(С)=Е7, 80 т.е. флаг S=1 C3 безусловная передача управления на 00 команду с адресом 8300 83 SUI 32 JZ 8028 INR A ADD A CMP C 8030 JP 8010 8031 8032 8033 jmp 8300 8034 8035 В приведенной программе все числа записаны в шестнадцатеричной системе счисления. Мнемоники команд микропроцессора КР580ВМ80А и соответствующие им коды приведены в таблице П4. В крайних столбцах этой таблицы приведены значения старших 4 бит байта (старшей тетрады), в верхней и нижней строке значения младших четырех бит байта (младшей тетрады). MOV M, C 7 MOV M, B 1 MOV H, C 6 MOV H, B 0 MOV D, C - 3 LXI H, D16 5 MOV D, B - 2 LXI D,D16 4 MOV B, B - 1 LXI B,D16 1 LXI SP, D16 MOV B, C NOP 0 0 2 MOV M, D MOV H, D MOV D, D MOV B, D STA A16 SHLD A16 STAX D STAX B 2 3 MOV M, E MOV H, E MOV D, E MOV B, E INX SP INX H INX D INX B 3 4 MOV M, H MOV H, H MOV D, H MOV B, H INR M INR H INR D INR B 4 5 MOV M, L MOV H, L MOV D, L MOV B, L DCR M DCR H DCR D DCR B 5 6 HLT MOV H, M MOV D, M 7 MOV M, A MOV H, A MOV D, A MOV B, A STC MVI M, D8 MOV B, M DAA RAL RLC 7 MVI H, D8 MVI D, D8 MVI B, D8 6 8 MOV A, B MOV L, B MOV E, B MOV C, B - - - - 8 9 MOV A, C MOV L, C MOV E, C MOV C, C DAD SP DAD H DAD D DAD B 9 A MOV A, D MOV L, D MOV E, D MOV C, D LDA A16 LHLD A16 LDAX D LDAX B A Система команд микропроцессора КР580 B MOV A, E MOV L, E MOV E, E MOV C, E DCX SP DCX H DCX D DCX B B C MOV A, H MOV L, H MOV E, H MOV C, H INR A INR L INR E INR C C D MOV A, L MOV L, L MOV E, L MOV C, L DCR A DCR L DCR E DCR C D E MOV A, M MOV L, M MOV E, M MOV C, M MVI A, D8 MVI L, D8 MVI E, D8 MVI C, D8 E F MOV A, A MOV L, A MOV E, A MOV C, A CMC CMA RAR RRC F Таблица П4 7 6 5 4 3 2 1 0 ANA C ORA C POP B POP D POP H POP PSW 1 A ANA B ORA C RNZ D RNC E RPO RP 0 F SUB C 9 SUB B B B B ADD C 1 8 ADD 0 2 JP A16 JPO A16 JNC A16 JNZ A16 ORA D ANA D SUB D ADD D 2 3 DI XTH L OUT N JMP A16 ORA E ANA E SUB E ADD E 3 4 CP A16 CPO A16 CNC A16 CNZ A16 ORA H ANA H SUB H ADD H 4 5 PUSH PSW PUSH H PUSH D PUSH B ORA L ANA L SUB L ADD L 5 6 ORI D8 ANI D8 SUI D8 ADI D8 ORA M ANA M SUB M ADD M 6 7 RST6 RST4 RST2 RST0 ORA A ANA A SUB A ADD A 7 8 RM RPE RC RZ CMP B XRA B SBB B ADC B 8 9 SPHL PCHL - RET CMP C XRA C SBB C ADC C 9 A JM A16 JPE A16 JC A16 JZ A16 CMP D XRA D SBB D ADC D A B EI XCH G IN N - CMP E XRA E SBB E ADC E B C CM A16 CPE A16 CC A16 CZ A16 CMP H XRA H SBB H ADC H C D - - - CAL L A16 CMP L XRA L SBB L ADC L D E CPI D8 XRI D8 SBI D8 ACI D8 CMP M XRA M SBB M ADC M E F RST7 RST5 RST3 RST1 CMP A XRA A SBB A ADC A F F E D C B A 9 8 Продолжение табл. П4