Уточнение спецификаций архитектуры СБИС

реклама

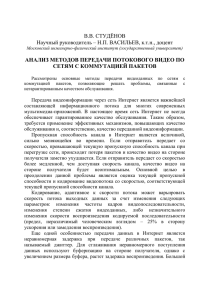

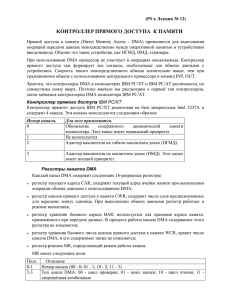

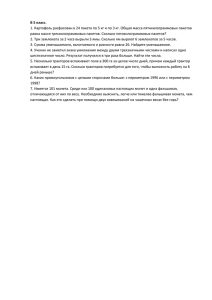

АНАЛОГО-ЦИФРОВАЯ «СИСТЕМА НА КРИСТАЛЛЕ» ПЕРИФЕРИЙНОГО КОНТРОЛЛЕРА МСТ-01 НА БАЗЕ IP-БИБЛИОТЕК ПЛАТФОРМЫ «МУЛЬТИКОР» А.В. Глушков1, Ю.И. Грибов1, В.А. Силин1, Т.В. Солохина1, Ю.М. Герасимов2, В.А. Нефедов3, Ю.Е. Шейнин4 ГУП НПЦ «ЭЛВИС», г. Москва, sectetary@elvees.com 2 ЗАО ЦП «Ангстрем-СБИС», г. Москва 3 ОАО МНИИ «АГАТ», г. Жуковский 4 С.-Петербургский государственный университет аэрокосмического приборостроения, г. Санкт-Петербург 1 1. Введение. Современные тенденции в разработке микропроцессоров связаны с переходом к размещению на одном кристалле не только процессорных ядер, но и аналоговых блоков. Еще одной тенденцией является широкое внедрение последовательных высокоскоростных интерфейсов (Rapid IO, HyperTransport, PCI Express, GigaEthernet, Infiniband и др.), вытесняющих традиционные шинные многоразрядные интерфейсы. Аналого-цифровая «система на кристалле» периферийного контроллера МСТ-01 разработана в ГУП НПЦ «ЭЛВИС» на базе платформы «МУЛЬТИКОР» [1-6] при участии специалистов предприятия ОАО МНИИ «АГАТ», входящего в концерн ОАО «Концерн ПВО «Алмаз-Антей» и ЗАО ЦП «Ангстрем-СБИС». Микросхема МСТ-01 – это одна из первых микросхем аналого-цифровой серии «Мультимикст». Контроллер МСТ-01 позволяет реализовывать конкурентоспособные вычислительные средства систем специального назначения, используемых в России и поставляемых на экспорт. Контроллер МСТ-01 предназначен для использования в многоканальных системах ввода, вывода и обработки сигналов. Он обеспечивает: ввод (дискретизацию и квантование) аналогового сигнала на частоте до 1 МГц по 4 каналам; цифровую обработку входного сигнала; вывод аналогового сигнала на частоте до 1 МГц по 4 каналам; скоростную передачу (до 200 Мбит/сек) обработанного сигнала; формирование сигналов управления. Контроллер спроектирован по технологии КМОП с проектными нормами 0,25 мкм и 5 уровнями металлизации, размещается в корпусе BGA-292 и, как ожидается, будет работать на тактовой частоте 120 МГц. При проектировании контроллера были решены следующие задачи: обеспечение высокой производительности для целочисленных данных и для данных с плавающей точкой в соответствии со стандартом ANSI/IEEE Standard 754-1985, «IEEE Standard for Binary Floating-Point Arithmetic»; создание высокоэффективной многоканальной системы аналогового ввода-вывода; внедрение скоростных последовательных каналов передачи данных. 2. Архитектура «системы – на – кристалле» МСТ-01. В состав периферийного контроллера МСТ-01 входят следующие основные узлы: CPU - центральный процессор; ICP целочисленный процессор; CP0 - системный сопроцессор; FPU - сопроцессор плавающей арифметики; DPRAM - двухпортовая оперативная память; MPORT - порт внешней памяти; DMA контроллер прямого доступа в память; OnCD - встроенные средства отладки программ; UART последовательный асинхронный порт; SWIC - контроллер канала Space Wire; TIMERS - таймеры; ICTR - контроллер прерываний; Switch - коммутатор; 4 channel ADC - 4-х канальный АЦП; 4 channel DAC - 4-х канальный ЦАП; LPORT - линковый порт или порт ввода вывода общего назначения; умножитель частоты на основе PLL; JTAG - отладочный порт. CPU представляет собой 32-разрядный процессор с архитектурой и системой команд MIPS32. Основные характеристики CPU: 32-х битные шины передачи адреса и данных; кэш команд объемом 16 Кбайт; кэш данных объемом 4 Кбайт; архитектура привилегированных ресурсов в стиле ядра R4000 (регистры Count/Compare для прерываний реального времени; отдельный вектор обработки исключений по прерываниям); программируемое устройство управления памятью. Оно имеет два режима работы - c TLB (Translation Look aside Buffer) и FM (Fixed Mapped). TLB имеет 16 строк; устройство умножения и деления; 461 поддержка отладки по JTAG-порту. Блок-схема CPU приведена на рис. 1. Он содержит следующие узлы: устройство исполнения (Execution Core), сопроцессор плавающей арифметики (FPU), системный управляющий сопроцессор (CP0), устройство управления памятью (MMU - Memory Management Unit), контроллер кэш (Cache Controller), устройство шинного интерфейса (BIU), кэш команд (Instruction Cache), кэш данных (Data Cache), средства отладки программ (OnCD - On Chip Debugger) с JTAG-портом. CPU содержит сопроцессор плавающей арифметики (FPU), который обеспечивает выполнение арифметических операций над операндами в формате с плавающей точкой. FPU полностью соответствует требованиям стандарта ANSI/IEEE Standard 754-1985. FPU поддерживает полностью 64-разрядные операции. Он содержит шестнадцать 64-разрядных регистров, каждый из которых может быть использован для хранения величин с одинарной или двойной точностью. FPU также содержит 32-разрядный регистр управления и состояния, который обеспечивает доступ ко всей информации по исключениям. Аналогично с целочисленным процессором в FPU используются одноцикловые команды загрузки и выгрузки. JTAG Instruction Cache OnCD MMU Cache Controller BIU TLB/FM Data Cache FPU Execution Core (RF/ALU/Shift) System Coprocessor Рис. 1. Блок схема CPU Внутренняя память контроллера объемом 128 Кбайт позволяет ей принимать и сохранять аналоговые сигналы. Большое количество программируемых счетчиков и развитая система внутренних и внешних прерываний обеспечивают выдачу на аналоговые выходы однократных и периодических аналоговых сигналов, хранящихся во внутренней памяти контроллера, в реальном масштабе времени с требуемыми задержками и длительностями. Порт внешней памяти обеспечивает подключение без дополнительной логики статической оперативной памяти типа SRAM, динамической памяти типа SDRAM или Flash. Конфигурационные регистры порта внешней памяти позволяют гибко настраивать такие параметры, как число тактов ожидания, размер банка памяти и его базовый адрес, тип памяти, размер страницы SDRAM и так далее. Это позволяет проектировать компактные встроенные устройства. Особое место при проектировании контроллера заняло выбор коммуникационной системы. В настоящее время происходит переход от традиционной шинной архитектуры к системам, реализованным на основе коммутатора. Ключевым элементом контроллера является коммутатор. Он выполнен в соответствии со спецификацией AMBA AXI Protocol (AXI - Advanced eXtensible Interface) [7]. Он имеет 7 портов задатчиков (CPU, каналы прямого доступа в память, контроллеры SWIC) и 2 порта исполнителей (внутренняя и внешняя память). В контроллере МСТ-01 имеются следующие режимы энергосбережения: программное изменение величины тактовой частоты; программное отключение тактовой частоты. Включение тактовой частоты осуществляется по внешним прерываниям. 3. Архитектура систем аналогового ввода и вывода. Контроллер содержит многоканальные системы ввода и вывода аналоговых сигналов. Основные особенности аналогового ввода: 4 независимых канала АЦП; реализовано на переключаемых конденсаторах последовательного приближения; разрядность 14 бит; частота дискретизации: не менее 1 МГц; дифференциальный вход 1...2 В: полоса входного сигнала не хуже 0...10 МГц; 462 напряжение питания аналоговое: 3.3 В; напряжение питания цифровое: 2.5В; встроенный или внешний источник опорного напряжения; режим пониженного потребления. Процесс конверсии в АЦП может запускаться от различных источников. Условия запуска следующие: возрастающий фронт сигнала на внешнем контакте контроллера START_EXT; сигнал, формируемый внутренним 16-разрядным делителем; запись «1» в разряд регистра управления и состояния АЦП (CSR_ADC). Основные особенности аналогового вывода: 4 независимых канала ЦАП; реализовано на токовых ключах; разрядность 14 бит; частота дискретизации: не менее 1 МГц; дифференциальный токовый выход; ток нагрузки - 4.095 мА; напряжение питания аналоговое: 3.3В; напряжение питания цифровое: 2.5В. Процесс конверсии в ЦАП может запускаться от различных источников. Условия запуска следующие: возрастающий фронт сигнала на внешнем контакте контроллера CLK_EXT; сигнал, формируемый внутренним 16-разрядным делителем. Каждый из АЦП и ЦАП имеет свой канал прямого доступа в память (DMA). Для управления работой каждого канала DMA имеются следующие регистры: регистр управления и состояния (CSR); набор регистров индекса (адрес памяти) и смещения (IOR, IR, OR); регистр начального адреса блока параметров DMA передачи (CP). Все каналы DMA могут выполнять процедуру самоинициализации (выполнение цепочки передач DMA). Для выполнения самоинициализации в каналах имеется 16-разрядный регистр CP, в котором хранится начальный адрес блока параметров очередного DMA обмена. Эти параметры при самоинициализации аппаратно загружаются в соответствующие регистры канала DMA. Процедура этой загрузки ничем не отличается от обычного DMA обмена. Блоки параметров, размещаемых в памяти, имеют следующую структуру (в порядке возрастания адресов): IR, OR, CP, CSR. При необходимости каналы DMA могут инициализироваться программно. Для этого CPU должен загрузить все необходимые регистры индекса и смещения, а затем регистр CSR. Основные параметры АЦП и ЦАП: динамический диапазон паразитных спектральных компонентов (SFDR) - 75 дБ; эффективная разрядность преобразователя (ENOB) - 13 бит; интегральная нелинейность (INL) – не более ±1 МЗР (младший значащий разряд); дифференциальная нелинейность (DNL) – не более ±1 МЗР; входной сигнал АЦП - от +0,4 до +2,0; выходной сигнал ЦАП - от +0,4 до +2,0. 4. Контроллеры каналов SpaceWire. В предлагаемую «систему на кристалле» встроены два контроллера каналов SpaceWire (SWIC - Space Wire Interface Controller), реализованные в соответствии с международным стандартом ECSS-E-50-12 [8-10]. Этот стандарт определяет физические интерфейсы (соединители и кабели, электрические характеристики) и полный стек сетевых протоколов: физический уровень, сигнальный уровень, канальный уровень, уровень передачи пакетов, сетевой уровень. Архитектура и протоколы SpaceWire ориентированны на требования аэрокосмических применений, характеризуются повышенной устойчивостью средств комплексирования SpaceWire к сбоям и нештатным ситуациям, а также пониженным энергопотреблением. Высокоскоростные последовательные каналы-линки SpaceWire со встроенным стеком базовых протоколов являются дуплексными каналами типа «точка-точка». Предусмотрена автоматическая адаптация скоростей передачи (от 2 до 400 Мбит/с) между двумя связанным им узлами по каналу-линку, автоматические процедуры разрыва и восстановления соединений, как после сбоев, так и при временном отключении/включении оборудования. LVDS-сигналы обеспечивают надежное функционирование высокоскоростных каналов при низком энергопотреблении. Контролеры SWIC имеют следующие особенности: реализация контроллера охватывает уровни стека протоколов SpaceWire, от сигнального до сетевого (частично) уровня; аппаратное детектирование ошибок связи: рассоединение, ошибки четности; встроенные LVDS приемопередатчики в соответствии со стандартом стандарта ANSI/TIA/EIA-644 (LVDS); встроенные в приемник LVDS резисторы-терминаторы; четыре канала DMA (два канала данных и два канала дескрипторов пакетов); встроенный буфер передаваемых данных на шестнадцать 32-х разрядных слов; 463 встроенный буфер принимаемых данных на четыре 32-х разрядных слова. Основой контроллера является DS-макроячейка (DS - data/strob), реализующая функции кодера/декодера. Кодер/декодер через драйверы LVDS подключен к физическим линиям связи. Контроллер SWIC взаимодействует с центральным процессором и системной оперативной памятью через интерфейсы ведущего и ведомого устройства. Через интерфейс ведомого устройства CPU может осуществлять чтение и запись регистров контроллера для определения его состояния и настройки параметров работы. Через интерфейс ведущего устройства контроллер выполняет запись данных в оперативную память, полученных из канала SpaceWire и чтение из системной памяти данных, которые необходимо передать в канал. Блок управления по командам CPU задает режимы работы приемо-передатчика канала SpaceWire. В этом блоке содержатся программно управляемый регистр, содержащий коэффициент скорости передачи данных, и доступный программному обеспечению на чтение регистр, в который записывается коэффициент скорости приема данных. В стандарте SpaceWire поддерживается передача маркеров системного времени; состояние последнего полученного извне маркера хранится в соответствующем регистре блока управления и может быть считано CPU. В контроллере обеспечивается промежуточное запоминание в коммуникационной буферной памяти принимаемых и передаваемых данных через DS-макроячейку, что позволяет согласовать скорость приема-передачи данных в канале с пропускной способностью коммутатора AXI. Блок буферной памяти реализуется на основе двухпортового ОЗУ. Управление приемом данных в буфер из DSмакроячейки и передачей данных из буфера в DS-макроячейку осуществляют соответственно блоки приема и передачи, которые взаимодействуют с блоками двухпортового ОЗУ. Буфер приема имеет конвейерную организацию и состоит из двух ступеней. Сначала буферизируются восьмиразрядные данные, принимаемые от DS-макроячейки (один разряд служебный). Затем для более эффективного использования пропускной способности коммутатора AXI в буфере формируются 32-разряные слова данных (и дополнительно четыре служебных бита). В буфер передачи с помощью канала передаваемых данных DMA из коммутатора AXI записываются 32-разряные слова данных (четыре разряда также используются для хранения формируемых блоком передачи служебных битов). Данные из буфера передачи в DS-макроячейку выдаются побайтно. Каналы DMA через интерфейс ведущего устройства реализуют обмен данными между оперативной памятью и буферной памятью контроллера. Используются четыре канала DMA: канал дескрипторов передаваемых пакетов, канал данных передаваемых пакетов, канал дескрипторов принимаемых пакетов и канал данных принимаемых пакетов. Для эффективной поддержки механизмов, обеспечивающих управление процессов обмена данными в соответствии со стандартом, заложенным в архитектуре виртуального интерфейса (VIA - Virtual Interface Architecture), в контроллере содержится четыре канала DMA - по два в каждом направлении (два канала на чтение из памяти и два канала на запись). Передача данных из канала SpaceWire в системную память. Маршрут принимаемых данных и схема их обработки приведены на рис. 2. 464 Маркер времени DS-макроячейка 7 6 5 4 3 2 1 0 8 Символы данных и концов пакетов 7..0 Буфер приема 3 2 23..16 15..8 4 31..24 Блок ведомого устройства Пр о цессо р 1 Дескриптор 7..0 DMA Канал записи дескриптора в память Данные Адрес Канал записи данных в память Системная память Рис. 2. Передача данных из линков SpaceWire в системную память Из канала в DS-макроячейку символы (байты) данных поступают последовательно (побитно). DS-макроячейка выделяет из последовательности приходящих символов символы данных и символы концов пакетов и передает их в буфер приема. По каналу байты данных передаются младшими разрядами вперед. Передача всех разрядов символа от DS-макроячейки в буфер приема осуществляется в параллельном коде. Символ содержит 9 разрядов, из них 8 используется для представления собственно байта данных, девятый бит является дополнительным и указывает, является ли этот байт символом данных или символом конца пакета. В буфере приема из байтов данных формируются слова разрядности 32. При формировании слов первый поступивший байт размещается в разрядах 7:0, второй - в разрядах 15:8, третий - в разрядах 23:16 и четвертый - в разрядах 31:24. Для того чтобы сократить загрузку процессора в ходе последующей обработки пакетов данных, в этом блоке выполняется выравнивание границ пакетов по границам слов и формирование дескрипторов пакетов, позволяющих процессору распознать границы отдельных пакетов. Собственно пакеты данных и дескрипторы пакетов могут храниться в различных областях памяти. Местоположение этих областей в памяти определяется процессором при настройке каналов DMA. Дескрипторы пакетов записываются в память друг за другом и логически организованы в очередь. Формат дескриптора пакета. Дескриптор пакета имеет следующую структуру: 31 - признак заполнения дескриптора действительными данными. Бит учитывается только при приёме пакетов (позволяет процессору идентифицировать конец очереди дескрипторов в памяти). При передаче пакетов этот бит не учитывается (DMA вычитывает всю область дескрипторов, заданную процессором). До запуска приёма, все 31-е биты дескрипторов области приёма должны быть обнулены программно; DMA не обнуляет 31-е биты не принятых дескрипторов, DMA только записывает ‘1’ в 31-е биты принятых дескрипторов. 30:29 - тип конца пакета: 01 - EOP, 10 - EEP; 28:25 - зарезервировано («0000») 24:0 - размер пакета в байтах. Слова данных из буфера приема передаются в канал DMA записи данных в память. Дескрипторы из блока приема передаются в канал записи дескриптора в память DMA. Блок DMA записывает данные и дескрипторы в системную память в соответствии с настройками, выполненными процессором. Процессор для канала записи дескрипторов в память определяет начальный адрес блока памяти и размер блока памяти. Для записи собственно пакетов данных в память может быть задан один блок памяти (так же, как и для канала записи дескриптора в память) или последовательность 465 блоков памяти, физически расположенных в разных местах памяти. При передаче данных в канал SpaceWire передается число дескрипторов (и пакетов), указанное в регистре размера блока дескрипторов на передачу. Передача данных из системной памяти в канал SpaceWire. Процесс передачи пакетов данных из системной памяти в канал через контроллер, а также преобразование форматов данных показаны на рис. 3. 0 1 2 3 4 5 6 Маркер времени DS-макроячейка 7 8 Симв олы данных и концо в пакетов 7..0 Буфер передачи 4 31..24 2 3 23..16 15..8 Блок ведомого устройства Процессор 1 Дескриптор 7..0 DMA Каналчтения дескриптора из памяти Данные Адрес Каналчтения данных из памяти Системная память Рис. 3. Передача данных из системной памяти в канал SpaceWire Пакеты данных загружаются из системной памяти в буфер передачи через каналы DMA чтения данных из памяти и чтения дескриптора из памяти. Чтение выполняется 32-х разрядными словами. Буфер передачи разбивает слова на отдельные байты. При этом из последовательности байтов в соответствии с информацией, содержащейся в дескрипторе, удаляются «лишние» байты байты, добавленные для выравнивания пакетов по границам слов, и вставляются символы концов пакетов EOP или EEP. Если в линк SpaceWire передаются пакеты, сгенерированные в данном узле, то предполагается, что они всегда должны заканчиваться символом EOP. Однако пакеты могут проходить через данный процессорный модуль транзитом. В этом случае они могут заканчиваться символом EEP. Коды маркеров EOP или EEP формируются контроллером аппаратно, на основании кодов дескриптора пакета на передачу (разряды 29-30 дескриптора пакета). Сами дескрипторы пакетов на передачу в сеть из основной памяти формируются программно. Распаковка 32-разрядного слова в последовательность из 4 байт при передаче из контроллера выполняется по правилу, согласованному с правилом упаковки байтов при приеме данных из канала в контроллер. Буфер передачи вначале передает в DS-макроячейку байт данных, находящийся в разрядах 7:0 слова, затем байт, находящийся в разрядах 15:8, затем байт, находящийся в разрядах 23:15, затем байт из разрядов 31:24 тридцатидвухразрядного слова. Символы данных и концов пакетов передаются блоком передачи в блок DS-макроячейки. DSмакроячейка преобразует полученные символы, в соответствии с алгоритмом DS кодирования, и передает их в канал. Символы передаются младшими разрядами вперед. Представление данных в памяти. Рассмотрим пример представления данных в системной памяти, если для данных выделен один сегмент памяти (рис. 4). 466 Системная память Начальный адрес Сегмент, выделенный процессором для записи данных Пакет 1 Пакет 2 Пакет 3 Начальный адрес Сегмент, выделенный процессором дл я записи дескрипторов 1 01 0A 1 10 08 1 01 0B 0 00 00 0 00 00 Байты,добавленные для выравнивания па кетов по границам слов Дескрипторпакета1 Дескрипторпакета2 Дескрипторпакета3 Рис. 4. Расположение принятых данных Пусть в системную память из канала SpaceWire было записано 3 пакета. Первый пакет имеет размер 10 байт и заканчивается символом EOP. Второй пакет имеет размер 8 байт и заканчивается символом EEP. Третий пакет имеет размер 11 байт и заканчивается символом EOP. Собственно пакеты хранятся в сегменте памяти, выделенном процессором для записи данных. Первый и третий пакет дополнены двумя и одним байтом соответственно с целью выравнивания по границам 32-х разрядных слов. Дескрипторы хранятся в сегменте памяти, выделенном процессором для записи дескрипторов. В дескрипторе указаны размеры пакетов в байтах - 0Ah, 08h и 0Bh соответственно. В дескрипторах хранится так же информация о типе конца пакета. В разряд 31 дескриптора записывается 1, что указывает процессору на то, что дескриптор заполнен действительными данными. Пакеты данных могут быть обработаны CPU в соответствии со следующей схемой. Процессор прочитывает первое слово из блока, выделенного для дескрипторов - первый дескриптор. По дескриптору он определяет тип конца пакета, в соответствии с этим решает, как его обрабатывать. По дескриптору он определяет действительный размер пакета и извлекает данные, относящиеся к пакету 1. Для того чтобы вычислить начальный адрес второго пакета, к начальному адресу блока данных добавляется размер первого пакета, и выполняется округление до границы ближайшего слова. После того, как первый пакет полностью обработан, процессор прочитывает дескриптор второго пакета. Обработка остальных пакетов выполняется аналогично. Процесс обработки очереди пакетов заканчивается, когда 31 разряд очередного дескриптора равен 0. Организация цепочек. Рассмотрим, как организуется цепочка сегментов памяти для хранения данных (рис. 5). 467 Системная память Сегмент 1 Начальный адрес 1-го сегмента Сегмент 2 Начальный адрес 2-го сегмента Сегмент 3 Начальный адрес 3-го сегмента Цепочка Начальный адрес цепочки Признак конца цепочки 1-й элемент цепочки Начальный адрес 1 сегмента 0 Размер 1 сегмента Начальный адрес 2 0 Размер 2-го Начальный адрес 3 1 Размер 3-го сегмента сегмента сегмента сегмента 2-й элемент цепочки 3-й элемент цепочки Рис. 5. Пример цепочки блоков памяти Пусть цепочка включает в себя три блока. В соответствии с начальным адресом цепочки прочитывается первый элемент цепочки, в котором определяется начальный адрес и размер первого блока. После того, как первый блок обработан, выполняется чтение второго элемента цепочки и так далее, до конца цепочки. Конец цепочки определяется следующим образом: если в 31 бите второго элемента конца цепочки 1, то это рассматривается как признак конца цепочки (последний элемент в цепочке). 5. Средства отладки программного обеспечения. Для отладки микросхемы МСТ-01 используется специальная реализация программного продукта MCStudio™ [11], который представляет собой интегрированную среду (IDE) разработки и отладки программного обеспечения для изделий, построенных на базе микросхем серий «Мультикор». MCStudio™ функционирует на инструментальном компьютере типа IBM-PC под операционной системой Windows 98/XP. Концепция интегрированной среды и инструментального программного обеспечения для микросхем серии «Мультикор» представлена на сайте фирмы [1], а среда MCStudio™ вместе с документацией на микросхему поставляется компанией «ЭЛВИС». Контроллер МСТ-01 имеет встроенные аппаратные средства отладки OnCD (On Chip Debugger), доступ к которым производится через JTAG- порт, реализованный по стандарту IEEE Standard Test Access Port and Boundary-Scan Architecture IEEE Std 1149.1-2001. OnCD предоставляет возможность пользователю по заданным через JTAG-порт условиям остановить CPU. При этом по завершении выполнения текущей команды останавливаются все активные компоненты такие, как DMA. В качестве условий останова CPU могут быть: обращение к памяти по записи или по чтению информации в заданном диапазоне адресов, либо при совпадении с заданными двумя адресами; выполнение команд с адресами в заданном диапазоне, либо при совпадении с заданными двумя адресами; выполнение команды с заданным адресом, либо обращение к памяти при записи или при чтении информации по заданному адресу; при вызове исполняемой программой любого из заданных векторов исключений (прерываний) или их совокупности; выполнение специальной команды перехода в отладочный режим; при выполнении заданного числа команд; требование перехода в отладочный режим со стороны JTAG-порта. После останова CPU имеется возможность с помощью OnCD визуализировать (или изменить) состояние всех архитектурных элементов MCТ-01, которые проецируются во всём адресном пространстве памяти системы, и продолжить выполнение программы. Перечисленные условия останова CPU, возможность в режиме отладки выполнения команды CPU по одному такту продвижения команды в конвейере, а также доступность всего адресного пространства в состоянии останова, даёт возможность использовать OnCD и JTAG-порт для построения эффективных отладчиков программ и систем. OnCD имеет программный интерфейс (JTAG-отладчик) с интегрированной средой разработки и отладки программ. Это позволяет проводить разработку программного обеспечения в реальном масштабе времени. 6. Заключение. Данная аналого-цифровая «система на кристалле» интегрирует высокопроизводительное вычислительное ядро с большим числом периферийных устройств. Реализация данного контроллера позволит обеспечить элементной базой отечественную радиоэлектронную аппаратуру для микроминиатюрных и дешевых систем многоцелевого назначения 468 ввода и обработки сигналов. Благодаря наличию высокоскоростных каналов SpaceWire данный контроллер позволяет реализовывать распределенные системы сбора и обработки данных. ЛИТЕРАТУРА 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. http://www.elvees.ru. Александров Ю.Н., Беляев А.А., Глушков А.В., Грибов Ю.Н., Никольский А.В., Петричкович Я.Я., Солохина Т.В. Новая отечественная платформа СБИС «МУЛЬТИКОР» для высокоточной скоростной обработки информации и управления объектами. // Цифровая обработка сигналов. 2001. - № 3. - С. 15-19. Петричкович Я.Я., Солохина Т.В. Цифровые сигнальные контроллеры «МУЛЬТИКОР» - новые отечественные серии систем на кристалле // Доклады 6-й Международной конференции «Цифровая обработка сигналов и ее применения (DSPA-2004)» . - Москва. - 31 марта - 2 апреля 2004. – Т. 1. - С. 8-15. Солохина Т.В., Петричкович Я.Я., Глушков А.В., Беляев А.А., Грибов Ю.И., Никольский В.Ф., Силин В.А., Алексеев М.Н., Александров Ю.Н. Время кентавров: Микросхемы серии Мультикор11хх (МС-11хх) для встраиваемых и мобильных применений // Chip News. - 2002. - № 8(71). С. 10-17. Солохина Т.В., Петричкович Я.Я., Глушков А.В., Александров Ю.Н., Глушков В.Д., Семенович А.М., Беляев А.А., Грибов Ю.И., Никольский В.Ф., Силин В.А., Алексеев М.Н., Бабичевский С.А., Федин В.А. Мультикор-12S - сигнальный контроллер с плавающей точкой для высокоточных встраиваемых применений // Chip News. - 2003. - № 8(81). - С. 4-15. Солохина Т.В., Петричкович Я.Я., Александров Ю.Н., Герасимов Ю.М., Заболотнов И.В., Алексеев М.Н., Беляев А.А., Грибов Ю.И., Глушков В.Д., Никольский В.Ф., Силин В.А., Крымов А.А., Тимофеев О.А., Миронова Ю.В., Перекин Р.Н., Кучинский А.В., Чупринов А.А., Грачев Р.А. Микросхемы базовых серий «МУЛЬТИКОР». Сигнальный микроконтроллер 1892ВМ2Т (МС-24). // Chip News. - 2005. - № 2(95). - С. 20-31. AMBA Specification (Rev 2.0) // http://www.arm.com. Solokhina T., Petrichkovich J., Glushkov A., Alexandrov Y., Goussev V., Sheynin Y., Gorbachev S., Suvorova E.. MCFlight™ - SOC-based chipset with SpaceWire links for Aerospace Applications.// International SpaceWire Seminar (ISWS 2003). - ESTEC Noordwijk, The Netherlands. - November 4–5, 2003. - P.28 -31. Space engineering. SpaceWire – Links, nodes, routers and networks. ECSS-E-50-12A, 24 January 2003 // ECSS Secretariat. - ESA-ESTEC Requirements & Standards Division. - Noordwijk, The Netherlands. Solokhina T., Petrichkovich Ja., Glushkov A., Alexandrov Y., Goussev V., Sheynin Y., Gorbachev S., Suvorova E. MCFLIGHT™ – SYSTEMS -ОN-CHIP FOR AEROSPACE APPLICATIONS.//16th IFAC SYMPOSIUM ON AUTOMATIC CONTROL IN AEROSPACE (ACA’ 2004).- S. Petersburg, Russia. June 14-18, 2004. - V. 2. - P. 271-276. Солохина Т.В., Петричкович Я.Я., Глушков А.В., Крымов А.А., Никольский В.Ф., Александров Ю.Н. и др. Интегральная среда разработки и отладки программ для модулей сигнальных контроллеров на базе ИМС платформы МУЛЬТИКОР» // Chip News. – 2002. - № 9(72). - С. 46-55. 469