Разработка архитектуры контроллера периферии

реклама

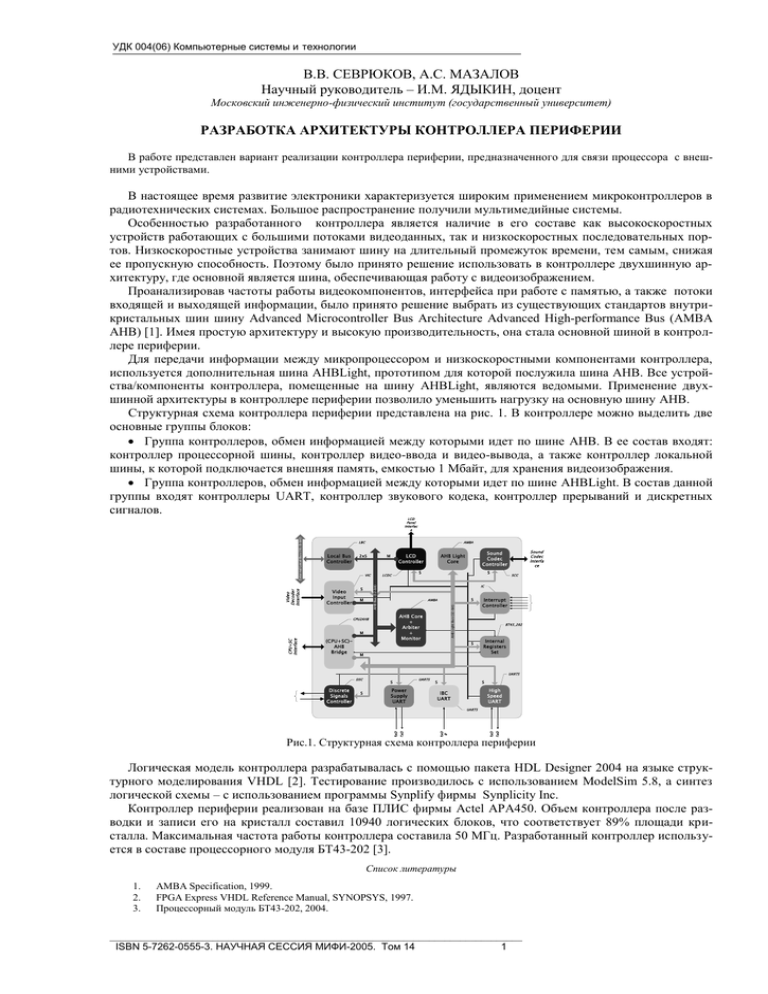

УДК 004(06) Компьютерные системы и технологии В.В. СЕВРЮКОВ, А.С. МАЗАЛОВ Научный руководитель – И.М. ЯДЫКИН, доцент Московский инженерно-физический институт (государственный университет) РАЗРАБОТКА АРХИТЕКТУРЫ КОНТРОЛЛЕРА ПЕРИФЕРИИ В работе представлен вариант реализации контроллера периферии, предназначенного для связи процессора с внешними устройствами. В настоящее время развитие электроники характеризуется широким применением микроконтроллеров в радиотехнических системах. Большое распространение получили мультимедийные системы. Особенностью разработанного контроллера является наличие в его составе как высокоскоростных устройств работающих с большими потоками видеоданных, так и низкоскоростных последовательных портов. Низкоскоростные устройства занимают шину на длительный промежуток времени, тем самым, снижая ее пропускную способность. Поэтому было принято решение использовать в контроллере двухшинную архитектуру, где основной является шина, обеспечивающая работу с видеоизображением. Проанализировав частоты работы видеокомпонентов, интерфейса при работе с памятью, а также потоки входящей и выходящей информации, было принято решение выбрать из существующих стандартов внутрикристальных шин шину Advanced Microcontroller Bus Architecture Advanced High-performance Bus (AMBA AHB) [1]. Имея простую архитектуру и высокую производительность, она стала основной шиной в контроллере периферии. Для передачи информации между микропроцессором и низкоскоростными компонентами контроллера, используется дополнительная шина AHBLight, прототипом для которой послужила шина AHB. Все устройства/компоненты контроллера, помещенные на шину AHBLight, являются ведомыми. Применение двухшинной архитектуры в контроллере периферии позволило уменьшить нагрузку на основную шину AHB. Структурная схема контроллера периферии представлена на рис. 1. В контроллере можно выделить две основные группы блоков: Группа контроллеров, обмен информацией между которыми идет по шине AHB. В ее состав входят: контроллер процессорной шины, контроллер видео-ввода и видео-вывода, а также контроллер локальной шины, к которой подключается внешняя память, емкостью 1 Мбайт, для хранения видеоизображения. Группа контроллеров, обмен информацией между которыми идет по шине AHBLight. В состав данной группы входят контроллеры UART, контроллер звукового кодека, контроллер прерываний и дискретных сигналов. LBC AMBA 2xS VIC Video Input Controller LCD Controller M S LCDC S M S AMBA AHB Core + Arbiter + Monitor M CPU+SC Interface S SCC IC CPU2AHB (CPU+SC)AHB Bridge Sound Codec Interfa ce Sound Codec Controller AHB Light Core AHB Light Bus (32-bit) Local Bus Controller AHB Bus (32-bit) Video Decoder Interface External Local Bus (16/8-bit) LCD Panel Interfac e Interrupt Controller BT43_202 S M Internal Registers Set UARTS DSC Discrete Signals Controller S UARTS S Power Supply UART S S High Speed UART IBC UART RxD TxD RxD 0 TxD RxD UARTS Рис.1. Структурная схема контроллера периферии Логическая модель контроллера разрабатывалась с помощью пакета HDL Designer 2004 на языке структурного моделирования VHDL [2]. Тестирование производилось с использованием ModelSim 5.8, а синтез логической схемы – с использованием программы Synplify фирмы Synplicity Inc. Контроллер периферии реализован на базе ПЛИС фирмы Actel АРА450. Объем контроллера после разводки и записи его на кристалл составил 10940 логических блоков, что соответствует 89% площади кристалла. Максимальная частота работы контроллера составила 50 МГц. Разработанный контроллер используется в составе процессорного модуля БТ43-202 [3]. Список литературы 1. 2. 3. AMBA Specification, 1999. FPGA Express VHDL Reference Manual, SYNOPSYS, 1997. Процессорный модуль БТ43-202, 2004. ________________________________________________________________________________ ISBN 5-7262-0555-3. НАУЧНАЯ СЕССИЯ МИФИ-2005. Том 14 1 УДК 004(06) Компьютерные системы и технологии ________________________________________________________________________________ ISBN 5-7262-0555-3. НАУЧНАЯ СЕССИЯ МИФИ-2005. Том 14 2