IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 34, NO. I, JANUARY... 0018-9200/99$10.00 © 1999 IEEE

реклама

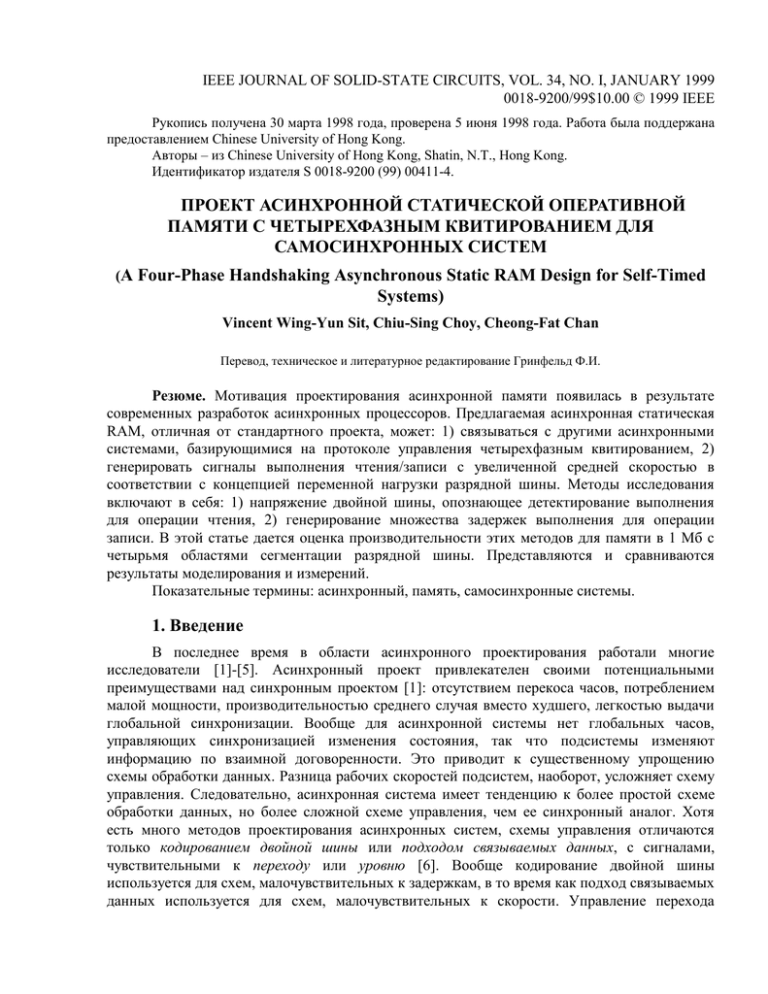

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 34, NO. I, JANUARY 1999 0018-9200/99$10.00 © 1999 IEEE Рукопись получена 30 марта 1998 года, проверена 5 июня 1998 года. Работа была поддержана предоставлением Chinese University of Hong Kong. Авторы – из Chinese University of Hong Kong, Shatin, N.T., Hong Kong. Идентификатор издателя S 0018-9200 (99) 00411-4. ПРОЕКТ АСИНХРОННОЙ СТАТИЧЕСКОЙ ОПЕРАТИВНОЙ ПАМЯТИ С ЧЕТЫРЕХФАЗНЫМ КВИТИРОВАНИЕМ ДЛЯ САМОСИНХРОННЫХ СИСТЕМ (A Four-Phase Handshaking Asynchronous Static RAM Design for Self-Timed Systems) Vincent Wing-Yun Sit, Chiu-Sing Choy, Cheong-Fat Chan Перевод, техническое и литературное редактирование Гринфельд Ф.И. Резюме. Мотивация проектирования асинхронной памяти появилась в результате современных разработок асинхронных процессоров. Предлагаемая асинхронная статическая RAM, отличная от стандартного проекта, может: 1) связываться с другими асинхронными системами, базирующимися на протоколе управления четырехфазным квитированием, 2) генерировать сигналы выполнения чтения/записи с увеличенной средней скоростью в соответствии с концепцией переменной нагрузки разрядной шины. Методы исследования включают в себя: 1) напряжение двойной шины, опознающее детектирование выполнения для операции чтения, 2) генерирование множества задержек выполнения для операции записи. В этой статье дается оценка производительности этих методов для памяти в 1 Мб с четырьмя областями сегментации разрядной шины. Представляются и сравниваются результаты моделирования и измерений. Показательные термины: асинхронный, память, самосинхронные системы. 1. Введение В последнее время в области асинхронного проектирования работали многие исследователи [1]-[5]. Асинхронный проект привлекателен своими потенциальными преимуществами над синхронным проектом [1]: отсутствием перекоса часов, потреблением малой мощности, производительностью среднего случая вместо худшего, легкостью выдачи глобальной синхронизации. Вообще для асинхронной системы нет глобальных часов, управляющих синхронизацией изменения состояния, так что подсистемы изменяют информацию по взаимной договоренности. Это приводит к существенному упрощению схемы обработки данных. Разница рабочих скоростей подсистем, наоборот, усложняет схему управления. Следовательно, асинхронная система имеет тенденцию к более простой схеме обработки данных, но более сложной схеме управления, чем ее синхронный аналог. Хотя есть много методов проектирования асинхронных систем, схемы управления отличаются только кодированием двойной шины или подходом связываемых данных, с сигналами, чувствительными к переходу или уровню [6]. Вообще кодирование двойной шины используется для схем, малочувствительных к задержкам, в то время как подход связываемых данных используется для схем, малочувствительных к скорости. Управление перехода 2 сложнее управления чувствительности к уровню, но схемы, чувствительные к уровню, должны быть сброшены в конце каждой операции. Проектируя асинхронную систему, следует быть очень осторожным с проблемами состязаний и риска сбоев [7], которые могут быть всегда решены назначением соответствующих состояний и добавлением избыточных состояний. Мотивация проектирования асинхронной памяти исходит из современного развития различных типов асинхронных процессоров. Например, Garside [8] разработал самосинхронное арифметико-логическое устройство CMOS как часть микропроцессора ARM. Muscato и Albicki [9] также разработали локально синхронизированный последовательный CMOS-микропроцессор. Tierno и другие [10] реализовали асинхронный GaAs-микропроцессор на 100 MIPS. Chang и Lu [11] выполнили статический процессор потока множества команд/данных с использованием микроконвейеров. Следовательно, необходимо разработать блок памяти для этих асинхронных процессоров. Есть много способов разработки асинхронной памяти. В лекции премии Turing "Микроконвейеры" [12] Sutherland предложил использовать в проекте памяти микроконвейеры. Однако схема управления усложняется и не может быть легко использована другими асинхронными системами. Генерация сигналов выполнения для чтения/записи также ограничивает потенциальное увеличение скорости асинхронных проектов. Мы собираемся улучшать их другим путем. Принципиальная схема статической RAM (SRAM) на 1 Мб на рис. 1 показывает общую структуру предложенного проекта. Проект малочувствителен к скорости, и используется подход связываемых данных. В основном, кроме управляющей схемы, схемы выполнения чтения/записи и других малых дополнений, это та же стандартная SRAM-архитектура [13]. С новой архитектурой и четырехфазной схемой управления, показанной на рисунке, разработка может быть связана с другими системами в соответствии с протоколом управления четырехфазным квитированием. Мы изобрели также метод дифференцирования времени обращения к элементам памяти различных ячеек. Со схемами выполнения чтения/записи система способна генерировать истинные сигналы выполнения, если только операция чтения/записи заканчивается так, что характеристика средней скорости улучшается. 3 Рис. 1. Принципиальная схема предложенной асинхронной памяти Таково краткое введение. Методы генерации сигналов выполнения чтения/записи излагаются в разделе II. Реализация предложенных методов для SRAM 1 Мб описана в разделе III. Результаты моделирования содержатся в разделе IV. Микросхема тестирования и результаты измерений приведены в разделе V. Сравнение предложенных методов и некоторых возможных дальнейших усовершенствований предложенной системы обсуждается в разделе VI. Наконец, успехи суммированы в разделе VII. II. Методы и схемы Чтобы гарантировать правильную работу асинхронного SRAM, время, принимаемое для генерации сигнала подтверждения, инициированного входом запроса, должно быть достаточным для завершения доступа к памяти для чтения или записи. В проекте обычной памяти это время доминирует над загрузкой на разрядной шине – очень длинному тракту. Так как эта разрядная шина – фиксированная, и ее загрузка предсказуема, время доступа к памяти достаточно постоянно и легко эмулируется фиксированным элементом задержки. В нашем предлагаемом проекте представлен простой метод наблюдения за различной загрузкой разрядный шины по элементам памяти в различных физических ячейках. Поскольку время доступа больше не постоянно, необходимы некоторые схемы для детектирования выполнения операций чтения и записи. Мы исследовали схему детектирования выполнения двухшинным считыванием напряжения (DVSCD – Dual-rail Voltage-Sensing Completion Detection) для генерации сигнала выполнения чтения. Она выбрана, потому что данные двухшинно кодируются внутри схем запоминания. К тому же этот метод требует только стандартных логических компонентов для формирования схемы обнаружения выполнения, простой в реализации. Схема DVSCD показана на рис. 2. Используемые усилители считывания идентичны усилителю считывания данных, описанному в [13] и [16]-[22]. Когда пара разрядных шин предзаряжается до VDD, выходы SAВ и SABB подтягиваются к LOW, а VCOMP подтягивается к HIGH. После предзарядки содержимое ячейки памяти считывается усилителем считывания данных как SAВ и SAВВ. Когда усилитель считывания данных закончит считывать, выход SAВ или SABB будет подтягиваться к HIGH, так как одна из разрядных шин будет на низком уровне. В это время VCOMP будет подтянут к LOW, что означает выполнение чтения. Рис. 2. Схема выполнения чтения DVSCD 4 При операции записи такая же схема применяться не может. Поскольку критическая схема – элемент памяти, трудно и непрактично добавлять датчик к каждому элементу памяти, чтобы выполнять считывание и генерировать сигнал выполнения. Мы исследовали схему генерации выполнения множества задержек (MDCG – Multiple Delays Completion Generation) для выработки сигнала выполнения записи. Если загрузка разрядной шины может быть сделана переменной разбиением разрядной шины на сегменты, для генерации сигнала выполнения записи во время каждого цикла может использоваться уникальная задержка худшего случая для каждого сегмента. Следовательно, среднее время записи сокращается сравнительно со стандартным использованием одной отдельной задержки. MDCG-схема показана на рис. 3. Каждый генератор задержки будет генерировать задержку худшего случая для соответствующего сегмента. В начале каждого цикла записи адресные биты целевого элемента памяти подаются на входы декодера сегмента. Декодер сегмента выбирает соответствующую задержку для этого отдельного сегмента. Если сигнал запроса разрешен, то сигнал выполнения записи генерируется в соответствии с задержанным сигналом запроса. Рис. 3. Схема выполнения записи MDCG (четыре области) III. Демонстрационный проект В любом проекте памяти организация матрицы ячеек памяти диктует компромиссы между размером, скоростью и питанием. Обычно оптимальна квадратная матрица с одним и тем же числом элементов памяти, связанных в строки и столбцы. Это организация, принятая в проекте SRAM 1 Мб (рис. 1) и используемая для демонстрации методов, обсуждавшихся в предыдущем разделе. SRAM 1 Мб выбран, потому что этот размер памяти: 1) достаточно велик, чтобы показать преимущество переменной загрузки разрядной шины, 2) является базисным модулем в формировании систем SRAM: большая система памяти может быть разработана с каскадированием нескольких блоков. 5 Простой способ получить переменную загрузку разрядной шины – разбиение разрядной шины на сегменты вставкой транзисторов прохода или схем передачи. Повидимому, возможная альтернатива – дальнейшее деление шины столбцов/битов мультиплексорами. Однако на самом деле это изменяет организацию памяти в сторону увеличения количества столбцов и вносит существенные изменения в компромиссы между размером, скоростью и питанием. В демонстрационном проекте разрядные шины разделены на четыре сегмента, как показано на рис. 4. Следовательно, вся матрица памяти разбита на четыре области доступа, управляемые адресными шинами A0 и А1. Теоретически чем больше сегментов разрядных шин, тем больше время доступа, которое может быть разрешено для повышения средней скорости. Однако вставка схем передачи также прибавляет загрузку разрядной шины и, в свою очередь, увеличивает время доступа. Для реализации 1 Мб было испытано и промоделировано различное число сегментов. Как видно из таблицы 1, предпочтительна сегментация три или четыре. В конце концов, выбрана сегментация четыре, потому что ее минимальное время доступа будет относительно ниже. Рис. 4. Принципиальная схема сегментированной связи с разрядной линией Таблица I Число сегментов Среднее время доступа (нс) Один Два Три Четыре Пять Шесть Семь Восемь Девять Десять 15,81 12,50 11,82 11,81 12,04 12,44 12,88 13,39 13,92 14,45 Схемы для детектирования выполнения операций чтения и записи показаны на рис. 2 и 3, соответственно. 6 Для выполнения управляющей схемы должны быть определены сигналы управления и связи между ними. Внешне управляющая схема должна быть способна: 1) обрабатывать сигнал запроса (REQ), вызывающий событие чтения\записи; 2) обрабатывать сигнал разрешения чтения (RW), дифференцирующий операции чтения и записи; 3) генерировать сигнал подтверждения (ACK), означающий конец операции. Внутренне для операции чтения управляющая схема должна быть способна: 1) генерировать сигнал предзагрузки (PC) для предварительной загрузки разрядной шины; 2) обрабатывать сигнал выполнения чтения (RC), сгенерированный схемой выполнения чтения; 3) генерировать сигнал разрешения для буфера чтения (CR), чтобы вывести данные чтения. Для операции записи управляющая схема должна быть способна: 1) генерировать сигнал разрешения для буфера записи (CW), чтобы ввести данные записи; 2) обрабатывать входной сигнал выполнения записи (WC), сгенерированный схемой выполнения записи. Диаграммы переходов сигналов для циклов чтения и записи показаны на рис. 5. Знак "+" означает переход из LOW в HIGH, а знак "-" означает противоположный переход. Схема управления выполнена на базе Булевой комбинации этих сигналов. Рис. 5. Диаграммы переходов сигналов при чтении/записи IV. Результаты моделирования Схема моделировалась моделирующим устройством HSPICE. Поскольку протокол управления предложенной системы памяти отличается от стандартного, в интерпретации результатов моделирования определены и применяются новые спецификации синхронизации. Идеализированные временные диаграммы с обозначенными подробностями синхронизации показаны на рис. 6. SRAM 1 Мб без сегментации используется как эталонный тест. В таблице II показаны существенные параметры синхронизации эталонной схемы. 7 Демонстрационный проект SRAM 1 Мб также моделировался, и результаты суммированы на рис. 7. Рис. 6. Временные диаграммы критических сигналов управления для чтения/записи Таблица II Параметры синхронизации нс Выполнение чтения 19,73 Подтверждение Выполнение чтения записи 23,01 17,47 Подтверждение записи 19,64 8 Рис. 7. Результаты моделирования Как ожидается, худшее время подтверждения немного больше, чем для эталонного теста, из-за задержки схемы передачи. Однако минимальные времена подтверждения чтения и записи низкие – 11,92 и 8,84 нс, соответственно. Следовательно, практически сегментированный SRAM в среднем функционирует быстрее. V. Результаты испытаний Производительность моделирования предложенных асинхронных методов может быть полностью измерена при моделировании одного столбца памяти. Эта идея применяется также в тестовой микросхеме, состоящей из отдельных столбцов элементов памяти. Были использовались два типа усилителей считывания: 1) стандартный пятитранзисторный усилитель [13], [16]-[19], [22], 2) модифицированный усилитель считывания, сформированный совместным подключением двух входов двух стандартных усилителей считывания, два выхода которых связаны с двумя вершинами кольца, сформированного двумя инверторами. Мы сосредоточимся только на двух столбцах, использующих модифицированный усилитель считывания. Один столбец используется для тестирования предложенных асинхронных методов, а другой – как эталонный тест. Вид микросхемы тестирования асинхронной памяти показан на рис. 8. Тестовая микросхема содержит также несколько цепочек логических элементов для временного анализа [23], [24]. Микросхема изготовлена по CMOS-технологии ATMEL ES2 0,7 мкм с размером кристалла 3710 5870 мкм2. Было изготовлено десять микросхем, и восемь из них были тестированы на функциональную корректность. Все измеренные результаты – средние результаты, принятые для этих восьми микросхем. 9 Рис. 8. Вид испытательной микросхемы Согласно спецификации синхронизации, показанной на рис. 6, невозможно непосредственно измерить время подтверждения чтения. Вместо этого измерялось время между активными фронтами входа запроса и выхода подтверждения чтения. Чтобы получить фактическое время подтверждения чтения, из измеряемых значений вычитались соответствующие задержки, оцененные по логическим цепочкам. На рис. 9 показаны измеренные времена подтверждения чтения в сравнении с результатами моделирования. Время подтверждения чтения изменяется от 16,51 до 26 нс. Разница между областями не так велика по сравнению с моделированием. Это очень хорошо, потому что фактическая загрузка разрядной шины не столь высока, как ожидалось. Это, в свою очередь, сокращает доминирующий эффект загрузки разрядной шины. Рис. 9. Сравнение времени подтверждения чтения при моделировании и измерении Время подтверждения записи очень хорошо управляется элементами задержки в схеме MDCG. Эти элементы могут быть настроены по напряжению. Цель – спроектировать элемент задержки так, чтобы его минимальное значение было меньше фактического времени записи. Таким образом, задержка может быть настроена до получения успешной операции записи. Однако никакие реалистические результаты для времени подтверждения записи не могли быть получены, потому что успешные операции записи всегда достигаются даже при настройке задержки на минимум. Единственное заключение, которое может быть выведено: время подтверждения записи должно быть меньше 9,52 нс (минимальная задержка). Погрешность в проектировании элементов задержки отражает неточность в используемых параметрах модели моделирования. VI. Обсуждение Концепция сегментированной разрядной шины предложена в асинхронном проекте SRAM. Эта концепция ведет к двум методам детектирования выполнения – DVSCD и MDCG. Оба метода были проверены функционально моделированием и тестовой микросхемой. С сегментированной линией загрузки время доступа к памяти может быть сокращено на 40 %. Дополнительная задержка из-за схем передачи может быть получена вычитанием худшей производительности (область 1) из эталонной. Из моделирования эти издержки – приблизительно 5 нс. Реально эти издержки – только около 1 нс от измеряемых результатов. 10 Вместе с увеличением площади приблизительно на 1,2 %, концепция сегментированной разрядной шины – привлекательный и простой способ разработки действительно асинхронной SRAM. В проекте SRAM 1 Мб размеры схем DVSCD и MDCG – 14342 и 21879 мкм2, соответственно. Они вместе представляют меньше 3 % размера столбца памяти. Схема DVSCD потребляет статический ток 5 мA и динамический ток 15 мA. Этот вид предположения мощности управляем и может быть всегда сокращен за счет скорости. Мощность, потребляемая схемой MDCG, минимальна. Как сказано в разделе III, предложенная система 1 Мб принята как базовый модуль для формирования системы SRAM. Чтобы сформировать больший блок памяти, можно легко связать вместе несколько систем 1 Мб с помощью мультиплексоров и декодеров. Это иллюстрирует, например, связь для асинхронной системы памяти 8 Мб, показанная на рис. 10. Все шины передачи данных (1 бит) и шины адреса (20 битов) систем 1 Мб связываются вместе. Мультиплексор используется для объединения восьми пар сигналов запроса и подтверждения, чтобы формировать одну пару сигналов запроса и подтверждения. Таким образом, эта асинхронная система памяти 8 Мб может использоваться тем же способом, что и проект 1 Мб. Сказанное объясняет, как использовать проект 1 Мб как макроэлемент. 11 Рис. 10. Асинхронная система памяти 8 Мб Поскольку время доступа к памяти предложенной асинхронной системы памяти зависит от ячейки памяти, средняя скоростная характеристика зависит от того, как обращаются к элементам памяти в различных областях. Практически большого времени требует только некоторый процент от объема системы. Следовательно, скорость может быть вообще оптимизирована распределением элементов памяти: сначала ближайшие (область 4), постепенно до самых дальних элементов памяти (область 1). Для случая, когда необходима целая матрица памяти 1 Мб, скорость может быть еще оптимизирована при первом делении данных: они будут размещены в отдельные классы согласно частоте использования. Далее, скорость может быть оптимизирована размещением данных, используемых чаще, в близких элементах памяти, а данных, используемых реже – в более далеких элементах. Наконец, способ оптимизации скорости зависит от различных типов приложений. Это может быть достигнуто модификацией программы, выполняемой устройством управления. Усилители считывания помещаются теперь в конце шин загрузки. Производительность может быть далее улучшена, если имеется участок памяти в середине разрядной шины (столбец памяти), чтобы вставить эти усилители. Это трудности при разработке новой асинхронной SRAM. VII. Заключение Мы определили предложенную асинхронную память как память, которая может быть связана с другими асинхронными системами и способна генерировать истинные сигналы выполнения чтения/записи. Сигнал выполнения генерируется при комбинировании концепции переменной загрузки разрядной шины с 1) методом детектирования выполнения, чувствительным к двухшинному напряжению – для операции чтения и 2) методом генерации выполнения множества задержек – для операции записи. Методы реализованы нами в SRAM 1 Мб с четырьмя областями сегментации и четырехфазным Протоколом Управления Квитированием. Методы были сначала оценены моделированием. Были определены новые временные спецификации памяти, и выполнено эталонное моделирование памяти для сравнения. Эти методы были также оценены тестовой микросхемой. Наконец, для DVSCDметодики она годится для генерации сигнала выполнения чтения. Она хорошо работает с концепцией сегментации разрядной шины. Это не требует большой площади, но должен быть отмечен компромисс между мощностью и скоростью. То же самое может быть сказано и для MDCG-методики. Предложенный проект 1 Мб может использоваться в различных приложениях, а для формирования большой системы памяти несколько SRAM 1 Мб могут быть легко связаны вместе. Скоростная характеристика предлагаемой памяти может быть также оптимизирована разумным распределением памяти. Ссылки [1] S.Hauck, "Asynchronous design methodologies: An overview," Proc. IEEE, vol. 83, pp. 69-93, Jan. 1995. [2] C.L.Seitz, Introduction to VLSI System. Reading, MA: Addison-Wesley, 1980. ch. 7, pp. 218-262. 12 [3] J.Spares, C.D.Nielsen, L.S.Nielsen, and J.Staimstrup, "Design of self-timed multipliers: A comparison," in Proc. Worksihop Asynchronous Design Methodologies, Manchester, U.K., Mar. 1993. [4] Y.K.Tan and Y.C.Lim, "Self-timed system design technique," Electron. Lett., vol. 25, no. 5, pp. 284-286, Mar. 1990. [5] Y.W.Pang, C.S.Choy, C.F.Chan, and W.K.Cham, "New handshaking control circuit for self-timed systems," Electron. Lett., vol. 30, no. 23, pp. 1907-1909, Nov. 10, 1994. [6] L.E.M.Brackenbury, S.B.Furber, and R.Kelly, "Transforming architectural models into high performance concurrent implementations," Department of Computer Science, Manchester University, Manchester, U.K. [7] H.Taub, Digital Circuits and Microprocessors, international ed. New York: McGrawHill, 1985, ch. 7, pp. 310-316. [8] J.D.Garside, "A CMOS VLSI implementation of an asynchronous ALU," Department of Computer Science, Manchester University, Manchester, U.K. [9] S.J.Muscato and A.Albicki, "Locally clocked microprocessor," Proc. IEEE, vol. 81, pp. 47-51, 1993. [10] J.A.Tierno, A.J.Martin, D.Borkovic, and T.K.Lee, "A 100-MIPS GaAs asynchronous microprocessor," Proc. IEEE, vol. 82, pp. 43-49, 1994. [11] C.M.Chang and S.L.Lu, "Design of a static MIMD data flow processor using micropipelines," IEEE Trans. VLSI Syst., vol. 3, no. 3, pp. 370-378, Sept. 1995. [12] 1. E.Sutherland, "Micropipelines," Commun. ACM, vol. 32. no. 6, pp. 720-738, June 1989. [13] B.Prince, Semiconductor Memories. New York: Wiley, 1992, ch. 5, pp. 149-166. [14] V.W.Y.Sit, C.S.Choy, and C.F.Chan, "Use of current sensing technique in designing asynchronous static RAM for self-timed systems," Electron. Lett., vol. 33, no. 8, pp. 667-668, Apr. 1997. [15] M.E.Dean, D.L.Dill, and M.Horowitz, "Self-timed logic using current-sensing completion detection (CSCD)," Proc. IEEE, vol. 79, pp. 187-191, 1991. [16] E.Seevinck, "A current sense-amplifier for fast CMOS SRAM's," in Proc. VLSI Circuits Symp. Digital Technical Papers, 1990, pp. 71-72. [17] P.Y.Chee, P.C.Liu, and L.Siek, "High-speed hybrid current-mode sense amplifier for CMOS SRAM's," Electron. Lett., vol. 28, no. 9, pp. 871-873, Apr. 1992. [18] M.Izumikawa et al., "A 400MHz, 300mW, 8KB, CMOS SRAM macro with a current sensing scheme," in Proc. IEEE 1994 Custom Integrated Circuits Conf., 1994, pp. 595-598. [19] K.Ishibashi al., "A 12.5ns 16MB CMOS SRAM with common-centroid-geometrylayout sense amplifiers," IEEE J. Solid-State Circuits, vol. 29, pp. 411-416, Apr. 1994. [20] P.H.Voss et al., "A 14 ns 256 K x 1 CMOS SRAM with multiple test modes," IEEE J. Solid-State Circuits, vol. 24, pp. 874-880, Aug. 1989. [21] J.P.Uyemura, Circuit Design for CMOS VLSI. Norwell, MA: Kluwer Academic, 1993, ch. 8, pp. 345-394. [22] C.J.Nicol and A.G.Dickinson, "A scalable pipelined architecture for fast buffer SRAM's," IEEE J. Solid-State Circuits, vol. 31, pp. 419-429, Mar. 1996. [23] Y.W.Pang, "A novel asynchronous cell library for self-timed system design," master's thesis, Department of Electronic Engineering, The Chinese University of Hong Kong, Dec. 1994. [24] Y.W.Pang, W.Y.Sit, C.S.Choy, C.F.Chan, and W.K.Cham, "An asynchronous cell library for self-timed system designs," IEICE Trans. Inform. Syst., vol. E80-D, no. 3, pp. 296-307, Mar. 1997. 13