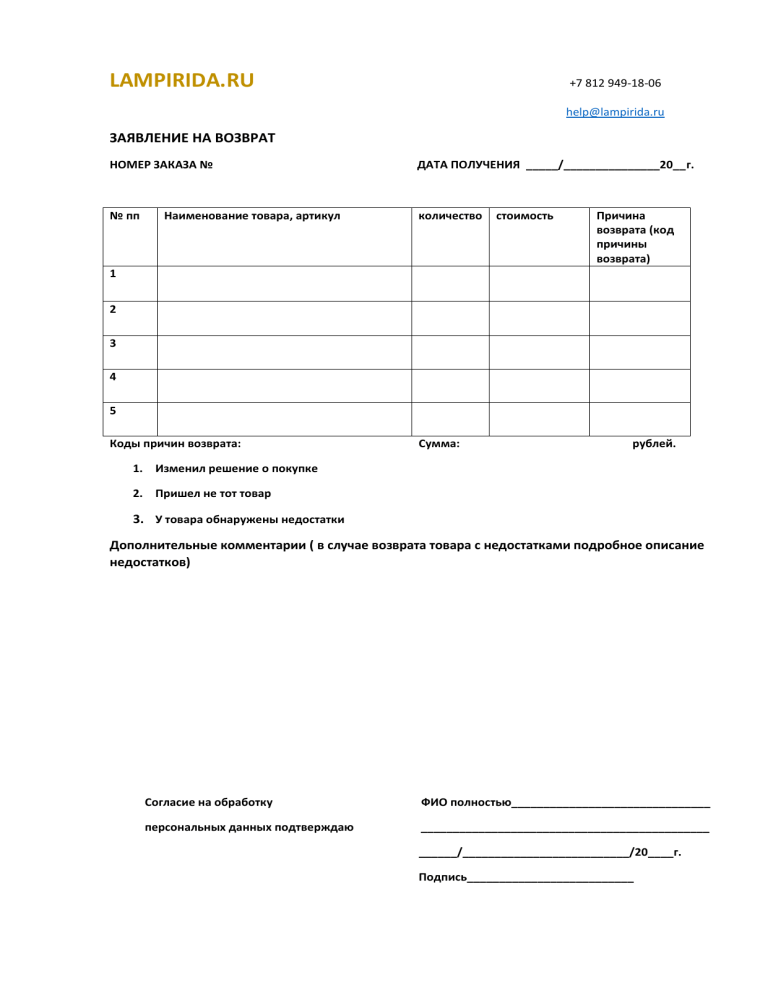

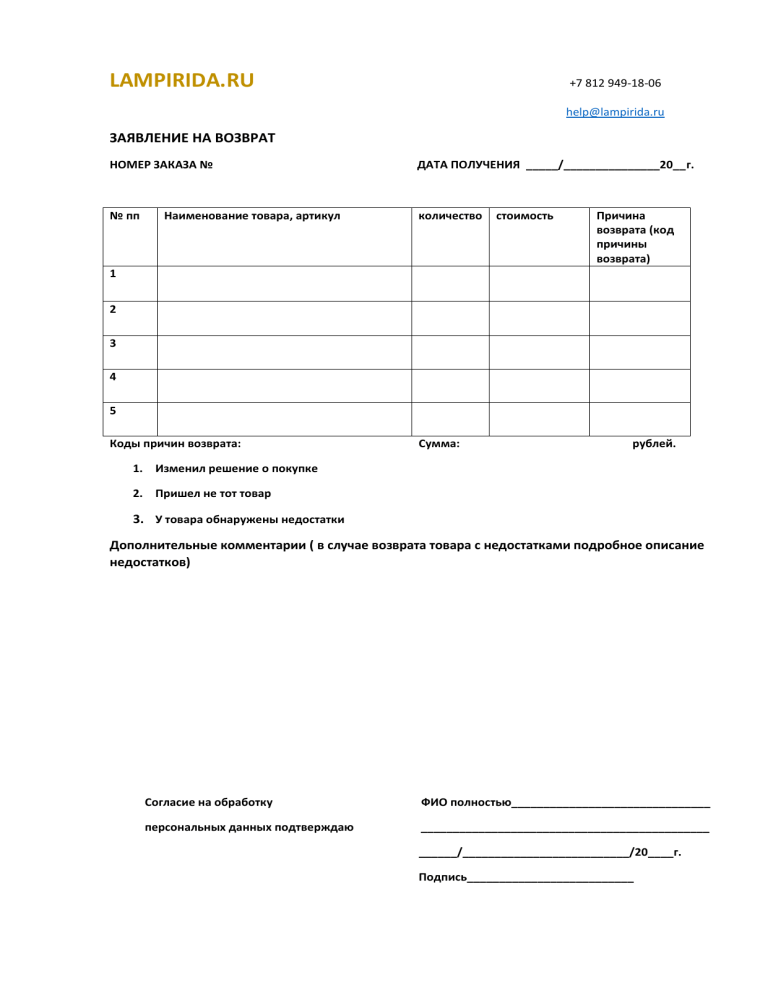

LAMPIRIDA.RU

+7 812 949-18-06

[email protected]

ЗАЯВЛЕНИЕ НА ВОЗВРАТ

НОМЕР ЗАКАЗА №

ДАТА ПОЛУЧЕНИЯ _____/_______________20__г.

№ пп

количество

Наименование товара, артикул

стоимость

Причина

возврата (код

причины

возврата)

1

2

3

4

5

Коды причин возврата:

Сумма:

рублей.

1. Изменил решение о покупке

2. Пришел не тот товар

3. У товара обнаружены недостатки

Дополнительные комментарии ( в случае возврата товара с недостатками подробное описание

недостатков)

Согласие на обработку

ФИО полностью_______________________________

персональных данных подтверждаю

_____________________________________________

______/__________________________/20____г.

Подпись__________________________