Программирование и вычислительная техника Вентили

реклама

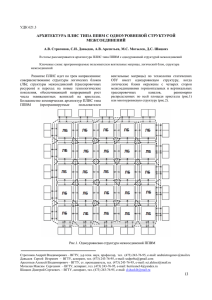

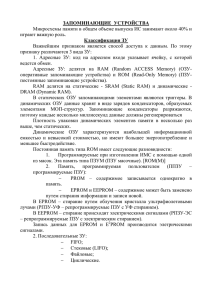

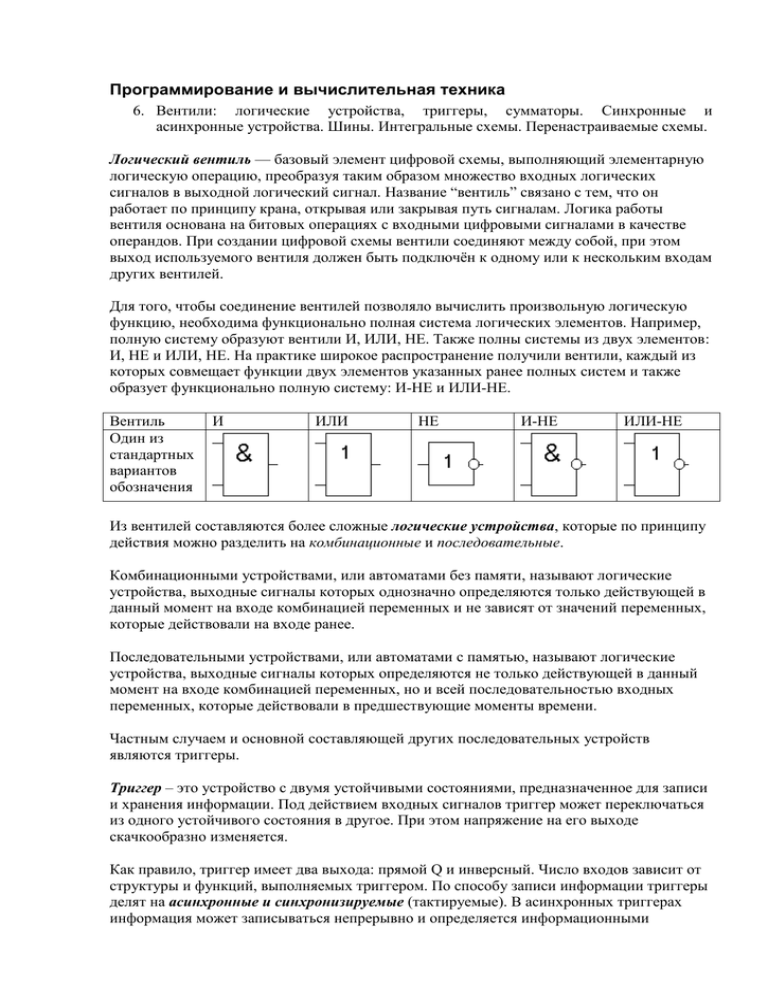

Программирование и вычислительная техника 6. Вентили: логические устройства, триггеры, сумматоры. Синхронные и асинхронные устройства. Шины. Интегральные схемы. Перенастраиваемые схемы. Логический вентиль — базовый элемент цифровой схемы, выполняющий элементарную логическую операцию, преобразуя таким образом множество входных логических сигналов в выходной логический сигнал. Название “вентиль” связано с тем, что он работает по принципу крана, открывая или закрывая путь сигналам. Логика работы вентиля основана на битовых операциях с входными цифровыми сигналами в качестве операндов. При создании цифровой схемы вентили соединяют между собой, при этом выход используемого вентиля должен быть подключён к одному или к нескольким входам других вентилей. Для того, чтобы соединение вентилей позволяло вычислить произвольную логическую функцию, необходима функционально полная система логических элементов. Например, полную систему образуют вентили И, ИЛИ, НЕ. Также полны системы из двух элементов: И, НЕ и ИЛИ, НЕ. На практике широкое распространение получили вентили, каждый из которых совмещает функции двух элементов указанных ранее полных систем и также образует функционально полную систему: И-НЕ и ИЛИ-НЕ. Вентиль Один из стандартных вариантов обозначения И ИЛИ НЕ И-НЕ ИЛИ-НЕ Из вентилей составляются более сложные логические устройства, которые по принципу действия можно разделить на комбинационные и последовательные. Комбинационными устройствами, или автоматами без памяти, называют логические устройства, выходные сигналы которых однозначно определяются только действующей в данный момент на входе комбинацией переменных и не зависят от значений переменных, которые действовали на входе ранее. Последовательными устройствами, или автоматами с памятью, называют логические устройства, выходные сигналы которых определяются не только действующей в данный момент на входе комбинацией переменных, но и всей последовательностью входных переменных, которые действовали в предшествующие моменты времени. Частным случаем и основной составляющей других последовательных устройств являются триггеры. Триггер – это устройство с двумя устойчивыми состояниями, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется. Как правило, триггер имеет два выхода: прямой Q и инверсный. Число входов зависит от структуры и функций, выполняемых триггером. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может записываться непрерывно и определяется информационными сигналами, действующими на входах в данный момент времени. Если информация заносится в триггер только в момент действия так называемого синхронизирующего сигнала, то такой триггер называют синхронизируемым или тактируемым. Обозначение, используемые входы и выходы Схема реализации на ИЛИНЕ и И-НЕ вентилях Асинхронный RS-триггер Синхронный D-триггер В асинхронном триггере используются раздельные входы: R для установки в нулевое состояние и S для установки в единичное состояние. В синхронном триггере используется общий информационный вход D, на который подается информация, предназначенная для занесения в триггер и вход синхронизации C. Существует триггер с единственным счетным входом T – счетный T-триггер. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. Безотносительно триггеров, асинхронные устройства отличаются от синхронных тем, что задержка между поступлением входных сигналов и появлением выходных в первом случае измеряется в физическом времени прохождения сигнала по схеме, а во втором – в количестве тактов. Синхронизация упрощает расчет схемы. Различные арифметические операции могут быть сведены к определенной последовательности сложений, поэтому основой арифметико-логического устройства является схема для сложения двоичных чисел – сумматор. Сумматоры строятся на триггерах и запоминающих элементах (цифровых автоматах) или на логических схемах без памяти (комбинационных схемах). Рассмотрим сложение двух двоичных цифр А и В в так называемом полусумматоре. При сложении цифр А и В, наряду с суммой S в младшем разряде, возможен перенос цифры P в старший разряд: А+В=PS Это соответствует комбинации слагаемых 0+0=00, 0+1=01, 1+0=01, 1+1=10 Название «полусумматор» и введено потому, что в общем случае необходимо сложение и третьей цифры для переноса единицы из предыдущего разряда. В рассматриваемом примере предполагается сложение, начинающееся с младшего разряда двоичного кода. Если рассматривать S и P как некоторые логические функции, то они должны принимать значения, указанные в таблице истинности. слагаемые результат Десятичный A B S P эквивалент 0 0 0 0 0 0 1 1 0 1 1 0 1 0 1 1 1 0 1 2 На основании данной таблицы истинности составим формулу для функций S и P: S = НЕ A И B ИЛИ A И НЕ B P=A И B На основании полученных функций построим логическую схему. Схема должна иметь два входа для переменных А и В и два выхода для функций S и P. Обозначение Схема реализации Полусумматор Сумматор Полный одноразрядный сумматор, учитывающий перенос из младших разрядов, как показано в таблице, можно построить из двух полусумматоров и вентиля ИЛИ. Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый разряд ставится одноразрядный сумматор, причем выход (перенос) сумматора младшего разряда подключен ко входу сумматора старшего разряда. Шина – это информационный канал, который объединяет все функциональные блоки микропроцессорной системы и обеспечивает обмен данными в виде двоичных чисел. Конструктивно шина представляет собой n проводников и один общий проводник (земля). Данные по шине передаются в виде слов, которые являются группами бит. В параллельной шине n бит информации передаются по отдельным линиям одновременно, в последовательной шине – по одной линии последовательно во времени. Все основные блоки микропроцессорной системы соединены с единой параллельной шиной, которая называется системной шиной. Системная шина содержит три шины: адреса, данных и управления. Шина адреса является однонаправленной. Она предназначена для передачи адреса ячейки памяти или устройства ввода/вывода. Направление передачи по шине адреса – от процессора к внешним устройствам. Шина данных является двунаправленной. Она предназначена для передачи данных между блоками микропроцессорной системы. Шина управления предназначена для передачи управляющих сигналов. Хотя направление управляющих сигналов может быть разным, эта шина не является двунаправленной, поскольку для сигналов разного направления используются отдельные линии. Интегральная схема — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле (или плёнке) и помещённая в неразборный корпус. Часто под интегральной схемой понимают собственно кристалл или плёнку с электронной схемой, а под микросхемой — интегральную схему, заключённую в корпус. Типичная ИС состоит из множества соединенных между собой микроэлектронных компонентов, таких, как транзисторы, резисторы, конденсаторы и диоды, изготовленные в поверхностном слое кристалла. Размеры кремниевых кристаллов лежат в пределах от примерно 1,31,3 мм до 1313 мм. Прогресс в области интегральных схем привел к разработке технологий больших и сверхбольших интегральных схем (БИС и СБИС). Эти технологии позволяют получать ИС, каждая из которых содержит многие тысячи схем: в одном чипе может насчитываться более 1 млн. компонентов. Интегральные схемы обладают целым рядом преимуществ перед своими предшественниками – схемами, которые собирались из отдельных компонентов, монтируемых на шасси. ИС имеют меньшие размеры, более высокие быстродействие и надежность; они, кроме того, дешевле и в меньшей степени подвержены отказам, вызываемым воздействиями вибраций, влаги и старения. Программируемая логическая интегральная схема (ПЛИС) — электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования. Для программирования используются отладочные среды, позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках Verilog, VHDL. Альтернативой ПЛИС являются заказные БИС, которые существенно дороже и компьютеры (микроконтроллеры), которые из-за программного способа реализации алгоритмов медленнее ПЛИС. Некоторые производители ПЛИС предлагают процессоры для своих ПЛИС, которые могут быть модифицированы под конкретную задачу, и затем встроены в ПЛИС, тем самым уменьшив место на печатной плате и упростив разработку для самой ПЛИС. Основные современные типы ПЛИС CPLD (complex programmable logic device — сложные программируемые логические устройства) содержат относительно крупные программируемые логические блоки — макроячейки, соединённые с внешними выводами и внутренними шинами. Функциональность CPLD кодируется в энергонезависимой памяти, поэтому нет необходимости их перепрограммировать при включении. FPGA (field-programmable gate array) содержат блоки умножения - суммирования (DSP),которые широко применяются при обработке сигналов, а также логические вентили и их блоки коммутации. FPGA обычно используются для обработки сигналов, имеют больше логических элементов и более гибкую архитектуру, чем CPLD. Программа для FPGA хранится в распределённой энергозависимой оперативной памяти микросхемы, поэтому требуется начальный загрузчик. Альтернативой ПЛИС FPGA являются более медленные цифровые процессоры обработки сигналов. FPGA применяются также, как ускорители универсальных процессоров в суперкомпьютерах.