Old manual_1_1

реклама

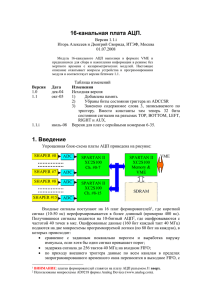

16-канальная плата АЦП. Версия 1.1 Игорь Алексеев и Дмитрий Свирида, ИТЭФ, Москва 24.10.2005 Модуль 16-канального АЦП выполнен в формате VME и предназначен для сбора и накопления информации в режиме без мертвого времени с калориметрических модулей. Настоящее описание охватывает вопросы устройства и программирования модуля и соответствует версии firmware 1.1. Версия 1.0 1.1 Дата дек-04 окт-05 Таблица изменений Изменения Исходная версия 1) Добавлена память 2) Убраны биты состояния триггера из ADCCSR 3) Заменено содержимое слова 3, записываемого по триггеру. Вместо константы там теперь 32 бита состояния сигналов на разъемах TOP, BOTTOM, LEFT, RIGHT и AUX. 1. Введение Упрощенная блок-схема платы АЦП приведена на рисунке: SHAPER #0 ADC SHAPER #7 ADC SHAPER #8 ADC SHAPER #15 SPARTAN II XC2S100 Ch. #0-7 SPARTAN II XC2S100 Ch. #8-15 SPARTAN II XC2S100 Memory & VME VME SDRAM ADC Входные сигналы поступают на 16 плат формирователей1, где короткий сигнал (10-50 нс) переформировывается в более длинный (примерно 400 нс). Получившиеся сигналы подаются на 10-битный АЦП2, где оцифровываются с частотой 40 точек в мкс. Оцифрованные данные (160 бит каждый такт 40 МГц) подаются на две микросхемы программируемой логики (по 80 бит на каждую), в которых происходит: сравнение с заданным поканально порогом и выработка наружу импульса, если хотя бы один сигнал превышает порог; задержка сигнала до 256 тактов 40 МГц на входном FIFO; по приходу внешнего триггера данные по всем каналам в пределах запрограммированного временного окна переносятся в выходное FIFO, с 1 2 ВНИМАНИЕ: платки формирователей ставятся на плату АЦП разъемом J1 вверх. Использованы микросхемы AD9218 фирмы Analog Devices (www.analog.com). добавлением 80-битного заголовка. Данные из выходного FIFO могут быть прочитаны по шине VME. В настоящей версии платы впаяна микросхема памяти (SDRAM) размером 32Мбайт. 2. Доступ по шине VME Модуль поддерживает только одну моду обмена – 32 бита адреса, 32 бита данных, непривилегированный доступ, что соответствует адресному модификатору VME 0x09. Номер модуля задается с помощью переключателей SW1:1-53, расположенных на плате. “ON” – соответствует биту 0, а “OFF” – 1. Базовый адрес вычисляется по формуле: 0xADC16000 + 0x100*N, где N – номер модуля. Формат регистров приведен в таблице: Адр.4 Название Значение 32-битные регистры в контроллере памяти и VME. 0x00 MCSR Биты: 31 – если этот бит установлен, то по триггеру данные будут автоматически передаваться во встроенную память. Бит сбрасывается по приходу сигнала конца сброса5. Когда этот бит установлен невозможен доступ к регистрам 0х40-0x80. 30 – установка этого бита приводит к инициализации контроллера памяти. 25 – этот бит ставится автоматически по приходу сигнала конца сброса5. 24 – переполнение буфера триггеров. 10:0 – длина триггера в 32-битных словах. Это число должно быть равно 5*(<длина окна>+1). Длина окна это биты 15:8 регистра WIN. Остальные биты зарезервированы. 0x04 MADDR Адрес в памяти в 32-битных словах. 0x08 MDATA Данные памяти. Запись/чтение приводит к записи/чтению 32битного слова памяти и к автоматическому увеличению адреса. 0x0C MTRIG Счетчик триггеров контроллера памяти. 0x10-0x3C Зарезервированы. Регистры в контроллерах каналов АЦП. Младшие 16 бит соответствуют каналам #0-7, старшие каналам #8-15. В большинстве случаев в младшие и старшие 16 бит имеет смысл писать одно и тоже. Запись разной длины окна полностью лишена смысла. ВНИМАНИЕ: переключатель SW1:6 управляет включением/выключением расположенного на плате кварцевого генератора и должен быть всегда в положении ‘OFF’. 4 Смещение относительно базового адреса модуля. 5 Сигнал конца сброса декодируется как активный уровень триггера длиннее 1 мкс. 3 0x40 0x44 0x48 0x4C 0x50 0x60-0x7C ADCCSR Биты: 3:0 – установка усиления для каждой из 4-х микросхем АЦП. 0 – 1 В пик-пик, 1 – 2 В пик-пик. 4 – разрешение внутреннего триггера, т.е. выработанный сигнал о превышении порога автоматически становится триггером. Этот режим предназначен исключительно для отладки. Кроме того, этот триггер не попадает на контроллер памяти, поэтому при использовании такого триггера 5 – разрешение внешнего входа триггера 8 – нет данных (‘1’, когда нет данных в выходном FIFO), (только чтение) 15 – переполнение выходного FIFO (‘1’), (только чтение) Остальные биты зарезервированы. WIN Биты: 7:0 – глубина входного FIFO; 15:8 – длина окна. TRIG Номер триггера (только чтение). Запись любого числа приводит к сбросу счетчика триггеров и всех FIFO. DATA Чтение данных. TBLK Биты 7:0 – длительность блокировки внутреннего триггера в тактах 40 МГц. THRS Поканальный порог для выдачи выходного импульса. Биты: 9:0 – значение порога 14 – полярность входного сигнала. 0 – положительная, 1 – отрицательная. 15 – включение данного канала (‘1’ – канал включен) Выходное FIFO организовано по 160 бит, которые вычитываются за 5 32битных обращений по шине VME. Одно событие занимает число 160-битных слов, равное длине окна плюс одно слово. Первое 160-битное слово FIFO служебное и его формат приведен ниже. Младшие 16 бит относятся к первым 8 каналам, а старшие к следующим 8. 32-битное слово 0, каждая из 16 битных половинок, содержимое регистра TRIG на момент прихода триггера: 15 0 номер триггера 32-битное слово 1, содержимое регистра WIN на момент прихода триггера: 15 8 7 0 длина окна задержка 32-битное слово 2, содержимое регистра CSR на момент прихода триггера: 15 8 3 2 1 0 переполнение выходное FIFO усиление для выходного FIFO пусто пар каналов 32-битное слово 3, биты признаков триггера, защелкнутые по его фронту: Биты Разъем Контакты 0-7 VME P2 (нижний) C17-C24 й 8-11 Передняя панель «верхний» (1 сверху) 1, 3, 5, 7 12, 13 Передняя панель «левый» (2й сверху) 1, 3 й 14, 15 Передняя панель «правый» (3 сверху) 1, 3 16-23 VME P2 (нижний) C25-C32 24-27 Передняя панель «нижний» (4й сверху) 28, 29 Передняя панель «левый» (2й сверху) 30, 31 Передняя панель «правый» (3й сверху) 32-битное слово 4: 15 константа 0xADC1 1, 3, 5, 7 5, 7 5, 7 0 Каждое следующее 160-битное слово содержит мгновенное значение напряжений для всех 16 каналов. Если прочитать 5 32-битных слов в массив data[5], то будет следующее соответствие данных и каналов: Канал Данные 0 ((data[0] >> 10) & 0x3F) | ((data[1] & 0x0F) << 6) 1 data[0] & 0x3FF 2 ((data[1] >> 14) & 0x03) | ((data[2] & 0xFF) << 2) 3 (data[1] >> 4) & 0x3FF 4 (data[3] >> 2) & 0x3FF 5 ((data[2] >> 8) & 0xFF) | ((data[3] & 0x03) << 8) 6 (data[4] >> 6) & 0x3FF 7 ((data[3] >> 12) & 0x0F) | ((data[4] & 0x3F) << 4) 8 ((data[0] >> 26) & 0x3F) | (((data[1] >>16) & 0x0F) << 6) 9 (data[0] >> 16) & 0x3FF 10 ((data[1] >> 30) & 0x03) | (((data[2] >> 16) & 0xFF) << 2) 11 (data[1] >> 20) & 0x3FF 12 (data[3] >> 18) & 0x3FF 13 ((data[2] >> 24) & 0xFF) | (((data[3] >>16) & 0x03) << 8) 14 (data[4] >> 22) & 0x3FF 15 ((data[3] >> 28) & 0x0F) | (((data[4] >>16) & 0x3F) << 4) Формат данных, читаемых из памяти в точности совпадает. 3. Передняя панель На передней панели расположены (сверху вниз): разъем межмодульной связи, предназначенный для выработки триггера по кластеру в калориметре. В текущей версии используется только для запоминания, связанной с триггером статусной информации. Сверху вниз идут: «верхний», «левый», «правый» и нижний». На каждом разъеме первая нога верхняя. 6 светодиодов, имеющих следующий смысл: 1. (верхний) Должен вспыхнуть на 1-2 секунды при включении питания. Если остался гореть работа с модулем невозможна. следует попробовать перевключить питание или нажать на кнопку сброса, расположенную на плате сверху вблизи от передней панели. 2. Мигает зеленым при доступе через шину VME, мигает красным при приходе триггера. 3. Мигает зеленым при доступе через шину VME, мигает красным при приходе триггера. 4. Горит зеленым если есть данные в выходном FIFO каналов 0-7, красным при переполнении. 5. Мигает зеленым при доступе через шину VME, мигает красным при приходе триггера. 6. (нижний) Горит зеленым если есть данные в выходном FIFO каналов 815, красным при переполнении. Практически, светодиоды 4 и 6 и 2, 3 и 5 дублируют друг друга. 3 разъема “LEMO”: 1. (верхний) Выход триггера, активный низкий. 2. Вход триггера, активный высокий. 3. (нижний) Вход внешней частоты (в настоящей версии не задействован. Сигналы имеют уровни TTL или LVTTL. Входные сигналы согласованы на 50 Ом. Выход триггера вырабатывается открытым коллектором активным низким и имеет внутри нагрузку 10 кОм на +3.3 В. Рекомендуется на принимающей плате поставить нагрузку 50-100 Ом на +2.0 В. На рисунке приведена простейшая схема выработки триггера с объединением модулей с помощью «проводного или»: +2.0 50 Ом Выход триггера АЦП АЦП АЦП Разветвитель Более правильная схема содержит преобразователи TTL-NIM, с входным согласованием 50 Ом на +2-3 В, логику триггера в стандарте NIM с выработкой блокировки триггеров ближе чем <длина окна><задержка>+200нс и преобразователей NIM-TTL. Кроме того в триггер необходимо подмешать сигнал конца сброса – триггерный импульс длительностью 5-10 мкс. Входной 34-контактный разъем. Верхние два контакта и все левые контакты – земля. Правые контакты – сигнальные. Самый нижний контакт – канал 0, следующий – 1 и т.д. Второй сверху контакт – канал 15. В настоящий момент входы согласованы на 100 Ом. 4. Регулировка смещения Снизу вблизи от входного разъема на плате расположены два подстроечных резистора и две точки для контроля напряжения, предназначенные для задания педесталов. Напряжения выставляются с помощью подстроечных резисторов, так чтобы установить нужный педестал и среднее арифметическое напряжений на контрольных точках было 1 В. Подстроечные резисторы Входной разъем Контрольные точки Земля 5. Алгоритм программирования 1 Подготовка модуля к работе: 1.1 Сбросить бит 31 в MCSR. 1.2 Запрограммировать регистры ADCCSR, WIN, TBLK и THRS. 1.3 Записать 0 в регистры TRIG, MTRIG и MADDR. 1.4 Запрограммировать MCSR со стоящим старшим битом. 2 Модуль готов к набору данных. В конце сброса нужно: 2.1 Дождаться бита 25 или отсутствия бита 31 или сбросить бит 31 руками. 2.2 Прочитать регистры MADDR, TRIG и MTRIG. Убедиться, что они находятся в правильном соответствии. содержимое MADDR это длина запомненных данных в 32-битных словах. 2.3 Записать 0 в MADDR. 2.4 Прочитать из регистра MDATA запомненные данные. 2.5 Записать 0 в регистры TRIG, MTRIG и MADDR. 2.6 Запрограммировать MCSR со стоящим старшим битом. 2.7 Перейти к пункту 2.1