ШПОРЫ Схемотехника

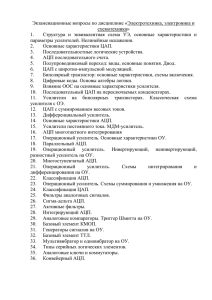

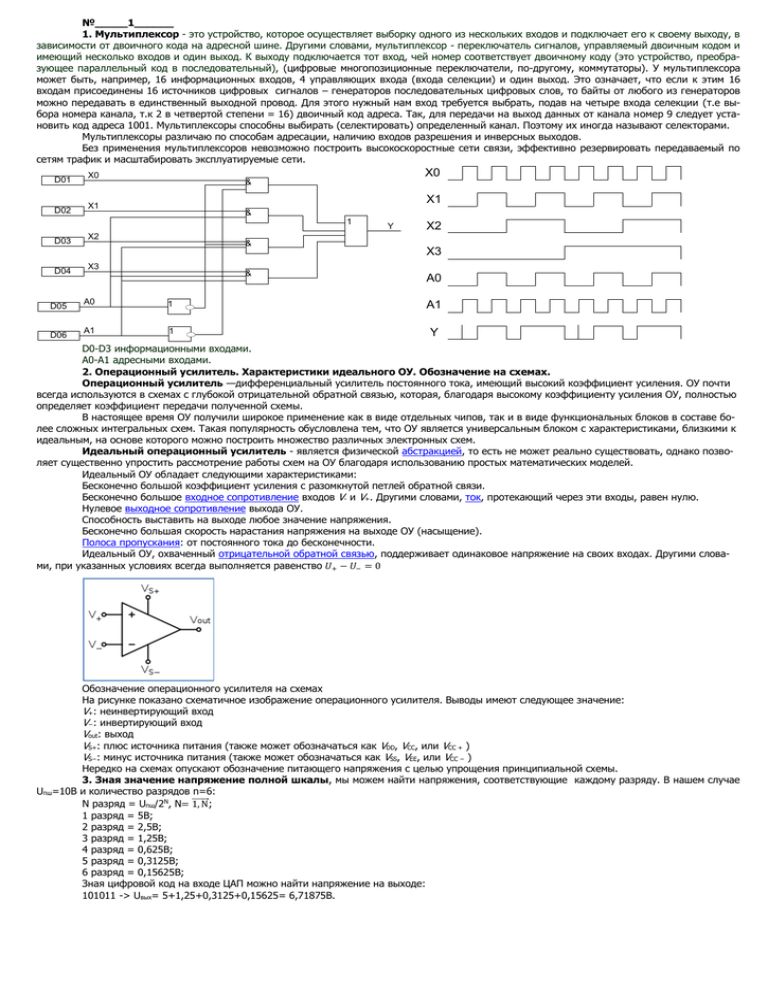

реклама