Интерфейс JTAG: тестИрованИе плат,

реклама

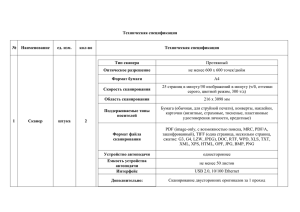

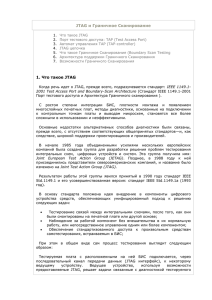

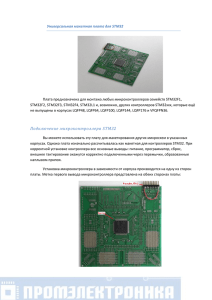

контроль и измерения Н.Кольский Интерфейс JTAG: тестирование плат, программирование и отладка У поминание о наличии интерфейса JTAG можно все чаще найти в описаниях современных микропроцессоров для встроенных приложений. Аббревиатура JTAG – это сокращение от названия созданной IEEE (Institute of Electrical and Electronics Engineers, Институт инженеров по электротехнике и радиоэлектронике) рабочей группы Joint Test Action Group (Joint Test Action Group, Объединенная рабочая группа по автоматизации тестирования). Ею подготовлены стандарты семейства IEEE 1149.х Test Access Port and Boundary-Scan Architecture (порт тестового доступа и архитектура граничного сканирования) и разрабатываются новые спецификации в этой области. Технология так называемого граничного сканирования была призвана дополнить методы проверки правильности разводки печатной платы и ее монтажа. Первоначально для этих целей применялись технологии и оборудование, основанные на подключении к контрольным точкам платы и выводам микросхем. Подобный "механистический" подход теряет свою эффективность или даже становится неприемлемым при использовании многослойных плат и плат с высокой плотностью монтажа, а также при использовании микросхем в современных корпусах (BGA, COB, QFP, SO и некоторых других): механические "игольчатые" щупы уже не могут "подобраться" к точкам тестирования. Кроме того, они могут искажать реальную картину сигналов. Например, прикосновение к точке непропаянного контакта может улучшить его работоспособность. Стандарты семейства IEEE 1149.х Test Access Port and BoundaryScan Architecture реализуют идею использования дополнительно интегрированных в электронные компоненты схем для организации тестирования готовой печатной платы и систем на основе печатных плат. В состав дополнительной логики входят внутренние ячейки граничного сканирования и соответствующие регистры, а также обвязка для коммутации. 36 ПЕЧАТНЫЙ МОНТАЖ 1/2009 Для обращения к этой дополнительной логике используется интерфейс JTAG, имеющий четыре (иногда пять, стандарт предусматривает необязательный пятый внешний вывод TRST или асинхронный сброс) контакта (TAP-выводы): TDI (Test Data In, вход тестовых данных), TDO (Test Data Out, выход тестовых данных), TMS (Test Mode Select, выбор тестового режима) и TCK (Test Clock, тестовая синхронизация). Эти же четыре дополнительных вывода должны быть сформированы и у платы, поддерживающей тестирование на основе стандарта IEEE 1149.х. Используя выводы JTAG-интерфейса, из микросхем, "отягощенных" дополнительной логикой для поддержки технологии граничного сканирования, формируется JTAG-цепочка, которая подключается к дополнительно сформированным JTAG-выводам платы. Для организации JTAG-цепочки на плате выход TDO "предыдущей" микросхемы соединяется с входом TDI "следующей". Для организации тестирования многоплатной системы вывод TDO "предыдущей" печатной платы соединяется с выводом TDI "последующей". Выводы TMS и TCK подключаются параллельно к соответствующим шинам JTAG-цепочки. Проверяемая плата с расположенными на ней микросхемами, оснащенными дополнительной логикой для поддержки Интерфейс JTAG: тестирование плат, программирование и отладка технологии граничного сканирования, подключается к рабочему месту оператора тестирования (на основе ПК, вычислительной PXI- или VXI-системы) через контроллер, обеспечивающий сопряжение данных между JTAG-интерфейсом и портом ввода/вывода рабочего места (это может быть шина PCI, порты Ethernet или USB или другие). Этот контроллер обеспечивает целостность сигналов, их передачу на значительные расстояния, которые могут разделять тестируемую систему и рабочее место оператора граничного сканирования в производственных условиях. На компьютерной системе рабочего места оператора запускается программа автоматического тестирования, в ходе которой по интерфейсу JTAG передаются сигналы управления/тестирования и регистрируются отклики микросхем на плате. На основании анализа этих откликов выносится "вердикт" о соответствии или несоответствии реальной работы платы запланированной и о возможных нарушениях контактов, отсутствии каких-либо микросхем или об их неправильной установке. Для создания программы тестирования для ПК (или в общем случае, хоста программно-аппаратного комплекса тестирования) нужно иметь исходные данные, в состав которых входят описание микросхем, поддерживающих технологию граничного сканирования, описание пути сканирования и описание тестируемой платы или системы в целом. Говоря об описании микросхем, мы имеем в виду наличие специального файла на языке BSDL (Boundary-Scan Description Language, язык описания граничного сканирования), содержащего ин- Рис.1 Питер ван ден Эйнден, директор компании JTAG Technologies: "...мы хотим расширить нашу деятельность и на российском рынке… Ведь данный шаг позволит нам внести свой вклад в развитие электронной промышленности в России и получить ощутимые преимущества от его постоянного роста" Периферийное сканирование для сложных печатных плат В декабре 2008 года на очередном семинаре компании PCB Technology с большим интересом был выслушан доклад Алексея Иванова (компания JTAG Technologies B.V., Израиль) "Технология тестирования печатных плат при помощи граничного сканирования JTAG. Требования к разработке". "Мы верим, что периферийное сканирование, основанное на стандарте IEEE 1149.1, – это лучшая и самая передовая технология для тестирования сложных печатных плат, диагностики и ремонта неисправностей, а также внутрисистемного программирования. Более 5000 установок периферийного сканирования от JTAG Technologies успешно работают на предприятиях всего мира. Мы поможем вам реализовать все возможности этой технологии на любом этапе жизненного цикла изделия – от разработки до опытного и серийного производства", – отметил докладчик. Технология периферийного сканирования помогает справиться с проблемами, возникающими при тестировании и программировании сложных печатных плат. Она позволяет решать проблемы доступа к электронным цепям, возникающие при использовании ИС в современных корпусах (BGA и другие). Эта технология основана на отраслевом стандарте IEEE 1149.1 и обеспечивает быстрое и точное тестирование и высокоскоростное внутрисистемное программирование плат с высокой плотностью монтажа. Компания JTAG Technologies является лидером в области создания решений и предоставления услуг для пользователей технологии периферийного сканирования. Успех ее применения зависит от надежности аппаратных средств. Контроллеры и вспомогательные модули компании JTAG Technologies обеспечивают высокую пропускную способность и идеальную целостность сигналов, что позволяет максимально использовать возможности периферийного сканирования. Обо всем этом подробно рассказано в статье Н.И.Кольского "Интерфейс JTAG: тестирование плат, программирование и отладка", опубликованной в журнале МКА: мир ВКТ (www.mka.ru) 3-2008, с разрешения которого мы печатаем ее в нашем журнале с небольшими сокращениями. Мы надеемся, что эта тема будет чрезвычайно интересна нашим читателям (ред. ПМ). формацию о том, какова структура логики, поддерживающей технологию граничного сканирования в микросхеме, как организован путь сканирования в элементе и какие функции, определенные стандартом IEEE 1149.х, поддерживаются. Этот файл предоставляется производителем микросхемы. Таким образом, технология граничного сканирования обеспечивает тестирование связей между микросхемами после того, как они были смонтированы на печатной плате, а также ПЕЧАТНЫЙ МОНТАЖ 1/2009 37 контроль и измерения Таблица 1. Возможности технологии IEEE 1149.х по обнаружению дефектов на платах Тип дефекта 1.4 Эффективность технологии IEEE 1149.x То же при совместном использовании с другими приемами диагностики Высокая Высокая Высокая Высокая Средняя Средняя Средняя Низкая Низкая Низкая Низкая Низкая Не выявляются Низкая Низкая Низкая Высокая Высокая Высокая Высокая Высокая Высокая Средняя или высокая Средняя или высокая Высокая Средняя или высокая Высокая Средняя Средняя Средняя Средняя или высокая Средняя или высокая Средняя Высокая Замыкания между контактами ввода/вывода Замыкания/разрывы Пропуск компонентов Неправильное размещение компонентов Применение дефектных компонентов Дефекты в аналоговых/радио/микроволновых подсистемах LVDT-дефекты Дефекты во время переходных процессов Дефекты задержек Замыкания внутри микросхем Дефекты из-за джиттера или пропуска битов Дефекты при повышенном напряжении Дефекты при больших токах Отклонения характеристик Уровень надёжности Прогностические дефекты BIST-дефекты обеспечивает наблюдение за работой компонентов без вмешательства в их нормальную работу. На платах могут устанавливаться помимо цифровых микросхем еще и аналоговые микросхемы, и пассивные элементы. "Путь" граничного сканирования на плате обходит элементы, не поддерживающие технологию IEEE 1149.х. В этом случае придется подумать о дополнительных процедурах испытаний, которые позволят выявить возможные неисправности в работе пропущенных областей. При этом необходимо отметить, что сегодня JTAG-интерфейс можно встретить и в аналоговой элементной базе. Так, компания National Semiconductor разработала монитор аналогового напряжения SCANSTA476, управляемый через шину JTAG. Он способен измерять напряжение в выборках из восьми аналоговых каналов или каналов смешанного сигнала в диапазоне от 0 до 5,5 В, необходимых, например, для проверки работы источника питания или критичных опорных напряжений на печатных платах. С технологией IEEE 1149.х тесно связана методология BIST (Built-in Self Test, встроенное самотестирование). Она основана на дополнении интегральной микросхемы аппаратными ресурсами или программным обеспечением для проведения самотестирования. Аналогом BIST считается самотестирование, проводимое BIOS компьютера Power-On Self-Test (POST), в ходе которого проверяется память RAM и шины питания. Технология BIST может внедряться средствами на уровне платы, но чаще всего это "черта" микросхемы. И если говорить о тестировании плат, то технология IEEE 1149.х имеет ряд ограничений по обнаружению дефектов, преодолеть которые можно лишь с использованием дополнительных приемов диагностики (табл.1), включая технологию BIST. При использовании BIST интерфейс JTAG может играть роль инструмента для передачи команд тестирования и сбора данных. Для этого в качестве опциональной возможности в стандарте IEEE 1149.1 введена команда RUNBIST. Сегодня ряд микропроцессоров поддерживает технологию BIST, работа которой реализуется через порт JTAG. Результаты BIST-проверок хранятся в регистрах данных, откуда информация в последовательном формате загружается через линию TDO. Объединение возможностей технологий JTAG и BIST позволяет обеспечить больший охват неисправностей, так как BIST помогает выявлять внутренние дефекты работы кристаллов микросхем и дефекты работы платы, возникающие в динамическом режиме ее работы, что недоступно технологии граничного сканирования. При использовании технологии BIST удобна иерархическая модель испытаний: сначала на системном уровне выявляются дефектные платы, а потом на уровне платы выявляются дефектные компоненты. Таблица 2. Ведущие производители оборудования и услуг для реализации технологии IEEE 1149.х на начало 21 века Рис.2 Высокоскоростной контроллер периферийного сканирования JT 3727/TSI 38 ПЕЧАТНЫЙ МОНТАЖ 1/2009 1 2 3 4 Компания Страна ASSET InterTech GOEPEL Electronic JTAG Technologies Corelis США Германия Нидерланды США Интерфейс JTAG: тестирование плат, программирование и отладка JTAG – история и компании Сегодня на рынке сформировался пул поставщиков, которые производят и предлагают готовые программно-аппаратные комплексы на базе ПК, предназначенные для разработки и применения программ тестирования на базе технологии граничного сканирования. Через 10 лет после принятия первого стандарта в семействе IEEE 1149.х согласно отчету Electronic Trend Publications на рынке таких комплексов сформировалась группа лидеров (табл.2). Лидер рынка, компания ASSET InterTech, была рождена "из ребра" корпорации Texas Instruments (TI). История ASSET Рис.3 Бюджетный вариант контроллера периферийного сканирования JT 3705/USB InterTech начинается с подразделения TI, образованного для развития работ в области технологии на базе стандарта ционного оборудования, медицинской, потребительской IEEE 1149.1. В 1995 году, аккумулировав 6-летний опыт ра- и авиационной электроники, в автомобильной и оборонботы в "стенах" TI, команда этого подразделения образо- ной промышленности по всему миру. Среди заказчиков вала самостоятельную компанию ASSET InterTech, унасле- JTAG Technologies такие компании, как Ericsson, Flextronics, довав и продуктовую линейку, и деловые связи. Нынешняя Honeywell, Medtronic, Motorola, Nokia, Philips, Raytheon, тройка лидеров состоит, по-видимому, из ASSET InterTech, Rockwell-Collins, Samsung и Sony. GOPEL Electronic и JTAG Technologies. Две последние компании – из Европы, которая тради- JTAG – что в имени твоем? ционно ближе к нашей стране, нежели Североамериканс- Говоря о JTAG-интерфейсе и о технологии граничного скакие штаты. нирования, следует различать ситуации, когда микросхема На выставке ЭкспоЭлектроника-2008 компания JTAG может полностью поддерживать стандарт IEEE 1149.х, имея Technologies официально объявила о своем повышенном стандартный JTAG-интерфейс и определенную стандартом интересе к российскому рынку. Руководство компании в ли- логику поддержки метода граничного сканирования, и когда це г-на Питера ван ден Эйндена (Peter van den Eijnden) уве- микросхема может включать лишь интерфейс JTAG, вероятно, рено в огромном потенциале российского рынка и хотело с некоторыми, не включенными в стандарты IEEE 1149.х возбы опередить здесь своих потенциальных конкурентов. Се- можностями, и не поддерживать технологию граничного скагодня компания помимо "европейской" Европы работает в нирования. В последнем случае JTAG-интерфейс используетСША и Китае. ся для иных целей, нежели тестирование плат. Говоря о "российских" амбициях компании, г-н Питер ван Внимательно изучив только что перечисленные возможден Эйнден отметил, что "...компания JTAG Technologies яв- ности решений от JTAG Technologies можно обнаружить, что ляется технологическим лидером. Мы шли к этому успеху на за более чем 15-летнюю историю стандарта интерфейс JTAG протяжении 15 лет, предоставляя решения и поддержку на- обрел новые "профессии". Помимо корректной разводки пешим клиентам по всему миру. Теперь мы хотим расширить на- чатной платы и ее монтажа сегодня компоненты технологии шу деятельность и на российском рынке. Мы с нетерпением граничного сканирования используются для программироваждем этого. Ведь данный шаг позволит нам внести свой вклад ния и отладки приложений. в развитие электронной промышленности в России и получить Но корни этих возможностей уходят в "седую" историю, ощутимые преимущества от его постоянного роста". когда в начале 90 годов прошлого века инженеры компаний Подтверждением технологического лидерства JTAG TI и ARM осознали возможность "проникновения" с помощью Technologies может быть тот факт, что компания первой (по интерфейса JTAG в отладочные регистры, а корпорация Intel, заявлению ее руководства) предложила рынку такие важные "экспериментируя" с программируемой логикой, "достигла" решения, как автоматическая генерация тестов, автоматичес- с помощью интерфейса JTAG конфигурационных регистров. кий анализ покрытия возможных неисправностей, автомати- Таким образом, приблизительно через три года после анонческий процесс программирования флеш-памяти и микро- са спецификации IEEE 1149.1 интерфейс JTAG стал использосхем программируемой логики. В комплект продукции JTAG ваться для отладки приложений для RISC-процессоров, ЦСП Technologies для граничного сканирования входят решения для и внутрисистемного программирования. подготовки и выполнения тестирования, анализа результатов и Если в 1994 году JTAG-интерфейс применяли для конфиприложения для внутрисистемного программирования. гурирования микросхем программируемой логики класса Более 5000 систем, установленных компанией JTAG CPLD компании AMD и Intel, то позже JTAG-порт был добавTechnologies, используются производителями коммуника- лен в микросхемы от Altera, Xilinx, Actel и Cypress & Xilinx. Для ПЕЧАТНЫЙ МОНТАЖ 1/2009 39 контроль и измерения Рис.4 Модуль цифрового ввода/вывода для тестирования разъемов типа DIMM JT2128 программирования же стал использоваться последовательный векторный формат (Serial Vector Format, SVF), стандарт которого совместно разработан компаниями TI, Tektronix и Teradyne. Фирма Xilinx для снижения объема SVF-файла предложила более компактный формат XSVF. Ну а открытым стандартом программирования ПЛИС (CPLD) стал IEEE 1532 Standard for Boundary-Scan-based In System Configuration of Programmable Devices (стандарт для внутрисистемного конфигурирования на основе технологии граничного сканирования). Работы по нему начаты в 1998 году, в ходе них язык BSDL был дополнен форматом ISC (InSystem Configuration, формат внутрисистемного конфигурирования). В составе рабочей группы по стандарту IEEE 1532 вошли компании Xilinx, Asset InterTech, Agilent, Alcatel, Cisco Systems, JTAG Technologies. Сегодня микросхемы программируемой логики (PLD) с поддержкой технологии IEEE 1532 предлагают Actel, Altera, Atmel, Cypress, Lattice Semiconductor и Xilinx, а программировать их позволяет инструментарий от JTAG Technologies, GOPEL Electronic и др. В связи с популярностью использования интерфейсов I2C и SPI в конструкциях микроконтроллерных микросхем компания Corelis включила поддержку прямого программирования памяти по этим шинам в свою программно-аппаратную платформу ScanExpress для поддержки технологии граничного сканирования. Это существенно ускорило процесс программирования по сравнению с программированием через порт JTAG. Однако возможности JTAG вполне конкурентоспособны для программирования небольших (менее 1 Мбайта) или средних (1–32 Мбайта) блоков флеш-памяти микросхем ПЛИС или FPGA. При их программировании для ускорения процесса можно сформировать укороченную псевдоцепочку граничного сканирования. Технология граничного сканирования может быть использована для программирования дискретных компонентов памяти – флеш и SPROM. При их подключении к компонентам, поддерживающим стандарт IEEE 1149.х, можно симулировать запись и чтение памяти, используя регистр граничного 40 ПЕЧАТНЫЙ МОНТАЖ 1/2009 сканирования. Этот же прием симуляции позволяет организовать и проверку памяти. Наряду со стандартной реализацией технологии IEEE 1149.х производители микроконтроллеров допускают отклонения от официальной спецификации для поддержки упомянутых выше новых возможностей использования интерфейса JTAG. Это можно обнаружить, например, в микроконтроллерах семейства |iPSD компании STMicroelectronics, где при соблюдении стандарта в части TAP-выводов конечный автомат (state machine) реализован с отходом от стандарта. 8-разрядные микроконтроллеры |iPSD разработаны с учетом опыта применения заказчиками PSD (Programmable System Device, архитектура программируемого Flash-устройства) и устойчивой популярности архитектуры 8051. Микроконтроллеры серий |iPSD32xx/|iPSD33xx представляют собой кристалл PSD-устройства с установленным поверх него кристаллом микроконтроллера 8032 и, по сути, являются однокристальной системой, заменяя до полутора десятка микросхем, с использованием которых строится стандартная микроконтроллерная система. Уникальные возможности микроконтроллеров |iPSD заключаются в преодолении ограничений стандартных 8051-микросхем. Стандартный микроконтроллер на основе архитектуры 8051 не способен производить запись в пространство кодов (память программ), что создает сложности при перепрограммировании в системе. В микроконтроллерах |iPSD при обновлении программы коды записываются в пространство данных и по завершении программирования возвращаются на прежнее место. Внутрисистемное программирование на основе интерфейса JTAG позволяет провести операцию в течение 10–25 с. Микроконтроллеры семейства MSP 430 корпорации TI официально имеют JTAG-интерфейс, но в их конструкцию не включен регистр граничного сканирования, поддерживающий классические операции тестирования, а также реализовано дополнительное мультиплексирование сигнала тактирования для вывода TDI. Что касается отладки, то в рамках стандартных режимов работы интерфейса JTAG отладка приложения реального времени не поддерживается. Однако конкретные компании реализуют поддержку отладки приложений реального времени с использованием интерфейса JTAG, "проприетарно", расширяя возможности технологии. В частности, такая возможность реализована корпорацией TI в технологии eXpressDSP для проектирования встроенных систем на базе ЦСП. Ее элементом помимо интерфейса JTAG, который имеется в каждом ЦСП Texas Instruments, является технология RTDX. Эта технология обмена данными интегрирует в JTAG-интерфейс возможности обмена данными в реальном времени (Real Time Data Exchange, RTDX) между ЦСП и хост-компьютером, на котором запускается отладочная среда.