Введение

реклама

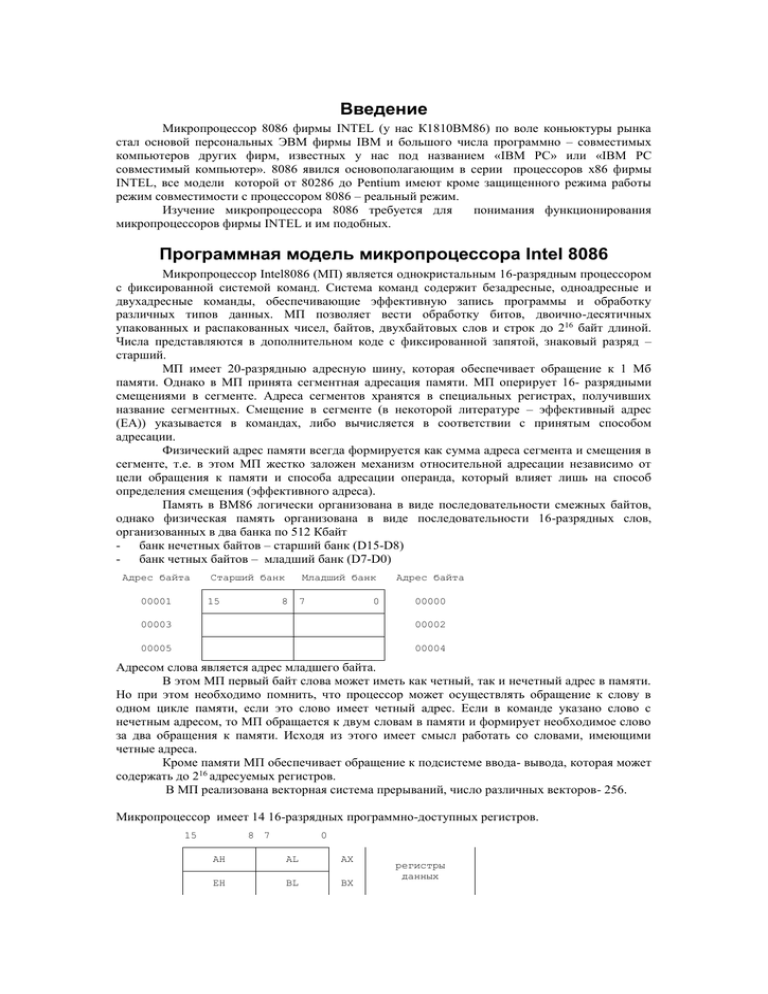

Введение Микропроцессор 8086 фирмы INTEL (у нас К1810ВМ86) по воле коньюктуры рынка стал основой персональных ЭВМ фирмы IBM и большого числа программно – совместимых компьютеров других фирм, известных у нас под названием «IBM PC» или «IBM PC совместимый компьютер». 8086 явился основополагающим в серии процессоров x86 фирмы INTEL, все модели которой от 80286 до Pentium имеют кроме защищенного режима работы режим совместимости с процессором 8086 – реальный режим. Изучение микропроцессора 8086 требуется для понимания функционирования микропроцессоров фирмы INTEL и им подобных. Программная модель микропроцессора Intel 8086 Микропроцессор Intel8086 (МП) является однокристальным 16-разрядным процессором с фиксированной системой команд. Система команд содержит безадресные, одноадресные и двухадресные команды, обеспечивающие эффективную запись программы и обработку различных типов данных. МП позволяет вести обработку битов, двоично-десятичных упакованных и распакованных чисел, байтов, двухбайтовых слов и строк до 216 байт длиной. Числа представляются в дополнительном коде с фиксированной запятой, знаковый разряд – старший. МП имеет 20-разрядныю адресную шину, которая обеспечивает обращение к 1 Мб памяти. Однако в МП принята сегментная адресация памяти. МП оперирует 16- разрядными смещениями в сегменте. Адреса сегментов хранятся в специальных регистрах, получивших название сегментных. Смещение в сегменте (в некоторой литературе – эффективный адрес (ЕА)) указывается в командах, либо вычисляется в соответствии с принятым способом адресации. Физический адрес памяти всегда формируется как сумма адреса сегмента и смещения в сегменте, т.е. в этом МП жестко заложен механизм относительной адресации независимо от цели обращения к памяти и способа адресации операнда, который влияет лишь на способ определения смещения (эффективного адреса). Память в ВМ86 логически организована в виде последовательности смежных байтов, однако физическая память организована в виде последовательности 16-разрядных слов, организованных в два банка по 512 Кбайт - банк нечетных байтов – старший банк (D15-D8) - банк четных байтов – младший банк (D7-D0) Адрес байта 00001 Старший банк Младший банк 15 7 8 0 Адрес байта 00000 00003 00002 00005 00004 Адресом слова является адрес младшего байта. В этом МП первый байт слова может иметь как четный, так и нечетный адрес в памяти. Но при этом необходимо помнить, что процессор может осуществлять обращение к слову в одном цикле памяти, если это слово имеет четный адрес. Если в команде указано слово с нечетным адресом, то МП обращается к двум словам в памяти и формирует необходимое слово за два обращения к памяти. Исходя из этого имеет смысл работать со словами, имеющими четные адреса. Кроме памяти МП обеспечивает обращение к подсистеме ввода- вывода, которая может содержать до 216 адресуемых регистров. В МП реализована векторная система прерываний, число различных векторов- 256. Микропроцессор имеет 14 16-разрядных программно-доступных регистров. 15 8 7 0 AH AL AX EH BL BX регистры данных CH CL CX DH DL DX 15 регистры общего назначения 0 Индексн. рег. источн. SI Индексн. рег. приемн. DI Указатель базы BP Указатель стека SP Указатель команд IP регистры адреса – "программный счетчик" Восемь регистров считаются регистрами общего назначения, поскольку во время выполнения программы в них могут храниться адреса и данные. Однако эти регистры имеют и закрепленные функции, что делает их неодинаковыми с точки зрения использования. Четыре регистра общего назначения AX, BX, CX, DX являются регистрами данных, т.к. их основное назначение – хранение операндов и результатов операций. Система команд допускает использование этих регистров целиком и в виде старшей и младшей половин. В команде, операндами которой являются слова, используется весь регистр целиком. В тех командах, где операнды являются байтами, может быть указана любая половина любого из четырех регистров данных (например, AL и AH). Кроме общих функций внутри этой группы имеется и более узкая специализация. При выполнении команд за этими регистрами по умолчанию закреплены различные функции. Это обстоятельство требует от программиста соблюдение определенных условий при распределении и использовании регистров. Закрепленные за регистрами функции приведены в таблице 1. сегмент команд CS сегмент данных DS сегмент стека SS Дополнит. сегмент ES регистр флагов F Регистр AX AL AH BX CX CL DX Сегментные Регистры – регистр состояния Назначение Аккумулятор Аккумулятор (мл. байт) Аккумулятор (ст. байт) Базовый регистр Счетчик Счетчик (мл. байт) Регистр данных и адреса ввода-вывода Закрепленные функции Ввод-вывод, умножение и деление слова Ввод-вывод, умножение и деление байтов, десятичная арифметика, преобразование кодов Умножение и деление байтов Базовый регистр, преобразование адресов Обработка строк. Подсчет циклов Динамические и циклические сдвиги Умножение и деление слов; Косвенная адресация регистров Ввода-вывода Следующие четыре общих регистра SP, BP, SI, DI применяются в основном для хранения 16-разрядных адресов, поэтому их можно отнести к адресным регистрам. И операнды, и адреса, хранимые в этих регистрах, могут быть только 16-разрядными. Регистр SP является системным указателем стека, используемым при прерываниях и обращении к подпрограммам. В этом регистре хранится и формируется текущий адрес внутри сегмента стека. Регистр BP является базовым регистром, используется при формировании адресов операндов (так же как BX). Регистры SI и DI являются индексными регистрами, используются при формировании адресов операндов и выполнении строковых операций. Регистр IP – указатель команд, фактически является регистром адреса команд или программным счетчиком. В этом регистре формируется адрес команды внутри сегмента памяти. Адреса, хранящиеся или формируемые с помощью этих регистров, не являются окончательными адресами памяти. Это адреса внутри сегмента или так называемые смещения. Окончательный адрес или физический адрес памяти определяется содержимым соответствующего сегментного регистра – CS, DS, SS, ES. Все регистры, участвующие в формировании адреса, имеют длину 16 разрядов, а физический адрес, вырабатываемый микропроцессором, содержит 20 разрядов. Дополнительные 4 бита образуются при сложении 16-разрядного смещения с содержимым одного из сегментных регистров, сдвинутым на 4 разряда влево. Перенос из старшего разряда игнорируется. 15 0 – смещение + 15 0 Сегментный регистр 0000 19 – адрес сегмента 0 – физический адрес Например: формирование адреса команды производится по следующей схеме: 15 0 IP + 15 0 CS 0000 19 0 Адрес команды Применение сегментных регистров разделяет пространство памяти на 64 Кбайтные сегменты, располагающиеся в памяти с адресов, кратных 16. В большинстве случаев использование сегментного регистра при формировании физического адреса происходит по умолчанию в соответствии с операцией и именем, присвоенным регистру. CS – сегментный регистр команд, используется при чтении команд. SS – сегментный регистр стека, используется при работе со стеком. DS – сегментный регистр данных, используется при обращении к операндами. ES – дополнительный сегментный регистр, используется при работе с операндами. В командах обработки данных можно нарушить правило умолчания. Для этого в командах используется явное указание сегментного регистра (префикс сегмента). Регистр состояния процессора имеет название регистра флагов и считается 16разрядным, хотя используется в этом регистре всего 9 разрядов. 15 14 13 12 11 10 9 8 7 6 CF DF IF TF SF ZF Содержимое отдельных разрядов управления. 5 4 AF 3 2 PF 1 0 CF называется флагом или флажком условий или Флаги состояния: SF – знак результата, установлен, если результат <0. ZF – нуль результата, устаговлен, если результат =0. FF – паритет, установлен если младший байт результата содержит четное число единиц. CF – перенос, устанавливается если результат выходит за разрядную сетку. AF– вспомогательный перенос, признак десятичной коррекции при обработке двоичнодесятичных чисел OF – переполнение, устанавливается при переполнении числовых разрядов разрядной сетки Флаги управления: DF – направление. Применяется в командах обработки строк. Если этот флажок сброшен, цепочка обрабатывается с первого элемента, имеющего наименьший адрес. В противном случае цепочка обрабатывается от наибольшего адреса к наименьшему. IF – разрешение прерываний. Если флажок сброшен, то прерывания запрешены, установленразрешены. TF – трассировка. Если этот разряд установлен, то после выполнения каждой команды генерируется внутреннее прерывание. Разряды регистра флагов программно доступны как для чтения, так и для записи. Структура и формат команд Основные команды могут иметь длину от 1 до 6 байт. Код операции всегда содержится в первом байте команды, а последующие байты, если они имеются, содержат адресную информацию. В этом микропроцессоре широко используется закрепление функций и режимов по умолчанию. Это позволяет экономить на длине команд и времени их выполнения. Для того чтобы отменить определенный режим вызова операции, установленный по умолчанию, перед байтом кода операции могут быть помещены один или несколько байтов, называемых «префиксом команды». «Префикс команды» можно рассматривать по-разному. На языке ассемблера префикс рассматривается как часть команды, т.к. его действие распространяется только на одну команду или ее часть. На уровне машинных команд префикс удобно рассматривать как специальную команду, устанавливающую режим выполнения следующей команды. Команды МП оперируют с операндами, хранящимися в памяти ЭВМ. Способы определения операнда называются режимом или способом адресации. В некоторых командах способ адресации операнда задается в первом байте команды, в других – информация о способе адресации содержится во втором байте команды, называемом постбайтом. Постбайт может определять один или два операнда. Структура постбайта имеет вид: 7 КОП OP1, OP2 6 5 MOD 4 3 REG / OP 2 1 0 R / M Поля MOD и R/M определяют первый операнд, поле REG/OP – второй. Обычно OP1 является приемником, а OP2 источником. В некоторых командах допускается изменение направления передачи данных. В таких командах в первом байте вводится поле d, определяющее направление передачи данных, если d=1 то в регистр, если d=0 то из регистра. Второй операнд, если он имеется, всегда находится в регистре, задаваемым полем REG/OP. В командах с одним операндом поле REG/OP используется для расширения кода операции, записанного в первом байте команды. Регистр, используемый командой, задается в поле REG/OP номером и кодом операции первого байта, что позволяет использовать один и тот же номер для обозначения разных регистров. Если команда оперирует с сегментными регистрами, то содержимое поля REG расценивается как номер сегментного регистра, иначе как номер регистра общего назначения. При этом, если команда может оперировать и байтом и словом, то в коде операции есть бит W, который определяет длину операнда ( W=0 - байт, W=1 - слово). Используемые регистры и их номера приведены в таблице 2. Номер регистра 000 Рег. общего назначения W = 1 W = 0 AX AL Сегмент. Регистры Короткий номер сегментного регистра ES 00 001 010 011 100 101 110 111 CX DX BX SP BP SI DI CL DL BL AH CH DH BH CS SS DS 01 10 11 Операнд, указываемый полями MOD и R/M, определяется в соответствии с имеющим место режимом адресации. Все способы адресации операндов в памяти обеспечивают формирование 16-разрядного адреса внутри сегмента или, как принято называть в технической документации, эффективного адреса, который обозначают буквами ЕА. Способ формирования эффективного адреса и используемый по умолчанию сегментный регистр в зависимости от значения полей MOD и R/M приведен в таблице 3. Операнд в регистре Операнд в памяти MOD 11 00 01 10 DS: (BX)+(SI)+D8 DS: (BX)+(DI)+D8 SS: (BP)+(SI)+D8 SS: (BP)+(DI)+D8 DS: (SI)+D8 DS: (DI)+D8 SS: (BP)+D8 DS: (BX)+D8 DS: (BX)+(SI)+D16 DS: (BX)+(DI)+D16 SS: (BP)+(SI)+D16 SS: (BP)+(DI)+D16 DS: (SI)+D16 DS: (DI)+D16 SS: (BP)+D16 DS: (BX)+D16 R/M 000 001 010 011 100 101 110 111 DS: (BX)+(SI) DS: (BX)+(DI) SS: (BP)+(SI) SS: (BP)+(DI) DS: (SI) DS: (DI) DS: D16 DS: (BX) W = 0 W = 1 AL AX CL CX DL DX BL BX AH SP CH BP DH SI BH DI где D8 - 8-битное смещение,указываемое в команде D16 – 16-битное смещение,указываемое в команде. При MOD=16 операнд находится в регистре, номер которого указан в поле R/M. По умолчанию в режимах адресации с привлечением регистра BP при получении физического адреса используется сегментный регистр SS, в остальных режимах адресации используется сегментный регистр DS. Чтобы изменить используемый сегментный регистр предусмотрена специальная однобайтовая команда – префикс замены сегмента. Он имеет следующий формат: 7 6 5 0 0 1 4 3 R E G 2 1 0 1 1 0 где REG – короткий адрес сегментного регистра (см. таблицу 2). Если перед командой стоит префикс замены сегмента, то при формировании адреса будет использоваться сегментный регистр, указанный в префиксе замены сегмента. Нельзя изменить сегментный регистр при: - чтении следующей команды (всегда CS); - обращение к стеку с участием SP (всегда SS); - цепочечных командах (сегментный регистр операнда-получателя всегда ЕS). Длина команд в микропроцессоре варьируется от 1 до 6 байт, не считая префиксов. В первых одном или двух байтах команды содержится код операции и указание способа адресации. После них могут находиться: - ни одного дополнительного байта; - двухбайтовый эффективный адрес (ЕА); - одно или двухбайтное смещение; - одно или двухбайтный непосредственный операнд; - одно или двухбайтное смещение и одно или двухбайтный непосредственный операнд; - двухбайтное смещение и двухбайтный сегментный адрес(только для прямого межсегментного перехода). Команда записывается в памяти в подряд идущие байты в стороны увеличения адресов, т.е. адрес первого байта команды будет младшим адресом байтов, занимаемых командой. Если длина смещения или непосредственных данных составляет два байта, первым всегда следует младший байт. Примеры некоторых форматов команд однобайтная операнд(ы) КОП КОП REG команда однобайтная регистре. КОП 11 REG R/M КОП MOD REG R/M – команда. неявный Операнд в - регистр-регистр регистр-память смещения без регистр-память со смещением КОП MOD REG R/M мл. байт данн. если ст. байт данн. смещение D16 непосредственный операнд в регистр КОП MOD КОП R/M мл. байт данн. ст. байт данн. - если данные 16-разрядные непосредственный операнд в память со смещением КОП MOD КОП R/M мл. байт ом. ст. байт см. 1 2 3 4 мл. байт данн. ст. байт данн. 5 6 Базовый - индексный способ адресации Эффективный адрес при этом способе адресации равен сумме содержимого базового и индексного регистров. MOD 00 00 00 R / M 100 101 111 Регистр SI DI BX Режим адресации задается постбайтом MOD=00; R/M=000, 001, 010, 011. Пример. Переслать в AX содержимое ячейки памяти с эффективным адресом (BP) + (SI). mov ax, [bp][si] 89 20 Относительный базовый – индексный способ адресации Эффективный адрес получается как сумма смещения, указанного в команде, содержимого базового и индексного регистров. ( BX ) EA = ( BP ) ( SI ) + 8-разрядн. Смещение 16-разрядн. Смещение ( DI ) Режим адресации задается постбайтом MOD=01, 10; R/M=000, 001, 010, 011. Пример. mov ax,3f[BX][DI] 89 21 ( BX ) EA = ( BP ) ( SI ) + ( BX ) EA = ( BP ) ( DI ) 8-разрядн. смещение ( SI ) + ( DI ) + 16-разрядн. смещение Система команд МП Intel8086 Команды перемещения данных Пересылка данных. MOV dst,src (dst) <- (src) - Из памяти или регистра в регистр MOV dst, src 100010 d w mod reg r/m - Непосредственные данные в регистр или память MOV dst, data 1100011 w mod reg r/m Данные Данные (w=0) - Непосредственные данные в регистр MOV reg, data 1011W red Данные Данные (w=0) - Из памяти в аккумулятор MOV A*, [Agp] - 1010000 w адрес мл. б. адрес ст. б. Из аккумулятора в память MOV [Agp], A* 1010001 w адрес мл. б. адрес ст. б. - Из регистра или памяти в сегментный регистр MOV sreg, src 10001110 mod reg r/m - Из сегментного регистра в регистр или память MOV src, sreg 10001100 mod reg r/m Загрузка в стек (с декрементом SP ) - Ячейки памяти или регистра PUSH src 11111111 mod 110 r/m - Регистра PUSH reg 01011 reg - Сегментного регистра PUSH sreg 000 reg 110 reg – короткий номер сегм. Регистра Извлечение из стека (с инкрементом SP) - В память или регистр POP dst 10001111 - В регистр POP reg 01011 reg - В сегментный регистр mod 000 r/m POP sreg 000 reg 111 reg – короткий номер сегм. Регистра Перестановка (источник и приемник обмениваются содержимым) - Между памятью или регистром и регистром XCHG dst, reg 1000011 w mod reg r/m - Между регистром и аккумулятором XCHG AX, RX 10010 reg Преобразование из кода в код - Загрузка из памяти по адресу (BX) +(AL) в регистр AL XLAT 11010111 Удобно использовать для табличного преобразования кодов. Загрузка регистра флагов в стек. PUSHF 10011100 Пересылка слова из стека в регистр флагов POPF 10011101 Загрузка регистра AH в младший байт регистра флагов SAHF 10011110 Загрузка эффективного адреса операнда в регистр LEA reg, src 10001101 mod reg r/m Загрузка двойного слова, определяемого операндом src в гегистры DS и reg LES reg, src 11000101 mod reg r/m Загрузка DS и POH физическим адресом LES reg, src 11000100 mod reg r/m Загрузка младшего байта регистра флагов в AH LAHF 10011111 Ввод из порта в AL или AX - Ввод из непосредственно адресуемого порта (не более 255 десятичн.) IN A*, PORT 1110010 w адр. порта - Ввод из порта, адресуемого через DX IN A*, DX 1110010 w Вывод из аккумулятора - Вывод в непосредственно адресуемый порт OUT PIRT, A* 1110011 w адр. порта - Вывод в порт, адресуемый через DX OUT DX, A* 1110111 w Арифметические операции Сложение ADD dst, src (dst = dst + src) - Содержимого регистра или памяти с содержимым регистра ADD dst, src 000100 d w mod reg r/m - Непосредственных данных с содержимым регистра или панели ADD dst, data 100000 s w mod 000 r/m данные Данные (w = 1) - Непосредственные данные с АХ ADD A*, data 0000010 w данные данные (w = 1) Сложение с учетом переноса - Регистра или памяти с регистром ADS dst, src 000100 d w mod reg r/m - Непосредственных данных с содержимым регистра или памяти ADC dst, data 100000 s w mod reg r/m данные Данные (w = 1) - Непосредственных данных с аккумулятором ADC A*, data 0001010 w Данные данные (w = 1) Инкремент - Регистра или памяти INC dst 1111111 w mod 000 r/m - Регистра INC reg 01000 reg Коррекция аккумулятора AL при сложении распакованных двоично-десятичных чисел (в коде ASCII) AAA 001100111 Коррекция аккумулятора AL при сложении упакованных двоично-десятичных чисел DAA 00100111 Вычитание SUB dst, src (dst = dst - src) - Регистра или памяти из регистра SUB dst, src 001010 d w mod reg r/m - Непосредственных данных из регистра или памяти SUB dst, data 100000 s w mod reg r/m данные данные (w = 1) - Непосредственных данных из аккумулятора SUB A*, data 0010110 w данные данные (w = 1) Вычитание с учетом заема - Регистра или памяти из регистра SBB dst, src 000110 d w mod reg r/m - Непосредственных данных из регистра или памяти SBB dst, data 100000 s w mod reg r/m данные данные (w = 1) - Непосредственных данных из аккумулятора SBB A*, data 0001110 w Данные данные (w = 1) Декремент - Регистра или памяти DEC dst 1111111 w mod 001 r/m - Регистра DEC reg 01001 reg Изменение знака NEG dst Сравнение 1111011 w mod 011 r/m ( dst – src ) CMP dst, src - Регистра или памяти и регистра - Непосредственных данных с регистром или памяти CMP dst, data 100000 s w mod 111 r/m данные данные (w = 1) Непосредственных данных с аккумулятором CMP A*, data 0011110 w Данные данные (w = 1) Десятичная коррекция распакованных чисел для сложения AAS 00101111 Десятичная коррекция распакованных чисел для вычитания DAS 00101111 Умножение без знака AL или AX на операнд src MUL src 1111011 w mod 100 r/m Умножение с учетом знака AL или AX на операнд src ( умножение целых чисел) IMUL src 1111011 w mod 101 r/m Десятичная коррекция AX при умножении распакованных чисел (код ASCII) AAM src 11010100 00001010 Беззнаковое деление содержимого DX, AX на операнд src DIV src 1111011 w mod 110 r/m Деление содержимого DX, AX на src с учетом знака (деление целых чисел ) IDIV src 1111011 m mod 111 r/m Десятичная коррекция AL при делении распакованных чисел (код ASCII) AAD src 11010101 00001010 Преобразование байта в слово CBW 10011001 Преобразование слова в двойное слово CWD 10011001 Логические операции Инвертирование NOT dst 1111011 w Логическое «И» mod 010 r/m ( dst = (dst) and (src) ) - Регистра или памяти и регистра AND dst, src 001000 d w mod reg r/m - Непосредственных данных и регистра или памяти AND dst, data 1000000 w mod 100 r/m данные данные (w = 1) - Непосредственных данных и аккумулятора AND A*, data 0010010 w Данные данные (w = 1) Логическое сравнение (установление регистра флагов) - Регистра или памяти и регистра TEST dst, src 1000010 w mod reg r/m - Непосредственных данных и регистра или памяти TEST dst, data 1111011 w mod 000 r/m данные данные (w = 1) - Непосредственных данных и аккумулятора Логическое «ИЛИ» - Регистром или памятью и регистром TEST A*, data 1010100 w данные данные (w = 1) - Непосредственными данными и регистром или памятью OR dst, src 000010 d w mod reg r/m - Непосредственными данными и аккумулятором OR dst, data 1000000 w mod 001 r/m данные данные (w = 1) Команды сдвигов Логический арифметический сдвиг dst на cnt разрядов влево XOR dst, src 001100 d w mod reg r/m Логический сдвиг вправо XOR dst, data 1000000 w mod 110 r/m данные данные (w = 1) Циклический сдвиг влево XOR A*, data 0011010 w данные данные (w = 1) Циклический сдвиг вправо SHL/SAL cnt dst, 110100 v w mod 001 r/m Циклический сдвиг влево через перенос SHR dst, cnt 110100 v w mod 101 r/m Циклический сдвиг вправо через перенос SAR dst, cnt 110100 v w mod 111 r/m Команды передачи управления Команда условного переноса Все команды условного перехода занимают 2 байта и имеют следующий машинный формат: КОП cмещение 8-байтовое смещение записывается в дополнительном коде, занимает второй байт команды и обеспечивает переход в диапазоне от –128 до +127 внутри сегмента относительно текущего значения указателя команд ( (IP) = (IP) + смещение). Переход осуществляется, если проверяемое условие выполняется, иначе выполняется следующая команда. На языке ассемблера в команде условного перехода указывается метка или адрес перехода. Смещение вычисляется ассемблером при трансляции, смещение= адрес перехода – IP (IP – адрес команды, следующей за командой перехода). Мнемоника JE/JZ JNE/JNZ JS JNS JO JNO JP/JFE JNP/JFO КОП 16-рич. 74 75 78 79 70 71 7A 7B ZF ZF GE SF GF GF PF PF = = = = = = = = Условие Перехода 1 0 1 0 1 0 1 0 JB/JNAE/JC 72 CF = 1 JNB/JAE/JNC 73 CF = 0 JBE/JNA 76 (CF) OR (ZF) = 1 JNBE/JA 77 (CF) OR (ZF) = 0 JL/JNGE JNL/JGE 7C 7D JLE/JNG 7E JNLE/JG 7F (SF) XOR (OF) = 1 (SF) XOR (OF) = 0 ((SF) XOR (OF)) OR (ZF) = 1 ((SF) XOR (OF)) OR (ZF) = 0 11101000 11101011 Смещение мл. б. Смысловое значение Если нуль или равно Если не нуль или не равно Если минус Если плюс Если переполнение Если нет переполнения Если четный паритет Если нечетный паритет Если перенос (не более или равно) Если нет переноса Если меньше или равно с учетом знака Если больше с учетом знака Если меньше Если не меньше Если меньше или равно Если больше смещение ст. б. смещение Команда безусловного перехода JMP – внутрисегментная команда с прямой адресацией относительно IP. В мнемонике в команде записывается метка или адрес перехода. При переходе к машинным командам смещение вычисляется аналогично командам условного перехода. Смещение записывается в дополнительном коде и может иметь 8 или 16 разрядов. Если смещение 8-разрядное, то переход называют коротким. JMP адрес перехода (метка) - в пределах сегмента. JMP src 11111111 Mod 100 r/m - Внутрисегментный с косвенной адресацией – адрес перехода в регистре или памяти 11101010 cмещ. мл. б. Смещ. ст. б. сегм. мл. б. сегм. ст. б. - Межсегментный с прямой адресацией – в команде указываются полный адрес перехода, включая значение сегментного регистра CS. В первом слове операнда находится новое содержимое IP, во втором находится CS. JMP (CS):смещение [FAR PTR МЕТКА] JMP src 11111111 Mod 100 r/m JMP 200:300 EA 0003 0002 - Межсегментный с косвенной адресацией 11101000 Смещение мл. б. Cмещение ст. б. Полный адрес перехода занимает в памяти двойное слово. Слово, указанное постбайтом, является смещением, а следующее – новым значением CS. (IP) = (EA) ; (CS) = (EA + 2) Вызов подпрограммы Структура и формат команды аналогичны командам безусловной передачи управления. Внутрисегментный переход с прямой адресацией CALL метка (адрес) (IP) = (IP) + смещение CALL src 11101010 11111111 mod 100 r/m Cмещ. мл. б. смещ. ст. б. сегм. мл. б. сегм. ст. б. сегм. мл. б. сегм. ст. б. - Внутрисегментный с косвенной адресацией 11101010 Cмещ. мл. б. смещ. ст. б. - Межсегментный с прямой адресацией CALL (CS):смещение [FAR PTR МЕТКА] Команда вызова подпрограммы CALL производит те же действия, что и команда JMP за исключением того, что перед выполнением команды адрес возврата помещается в стек. Если переход внутрисегментный, то в стек помещается лишь содержимое указателя команд IP. Если переход межсегментный, то в стек загружается сначала содержимое CS, затем IP. Возврат из подпрограммы RET При выполнении команды возврата из стека извлекается адрес возврата. Так как адрес возврата может иметь одно или два слова, для команды RET используют два кода. - Внутрисегментный возврат RET 11000011 - Межсегментный возврат RET FAR 11001011 Возврат из подпрограммы с увеличением указателя стека (SP) = (SP) + data - Внутрисегментный RET data 11000010 данные мл. б. данные ст. б. данные мл. б. данные ст. б. - Межсегментный RET data 11001010 Команды организации циклов Команды организации циклов обеспечивают уменьшение содержимого регистра CX и условный переход по результату. Команды организации циклов являются командами условного перехода, имеют такой же синтаксис и аналогично выполняются. КОП Смещение КОП 16-рич. E2 Условие Ветвления (CX) <> 0 LOOPE / LOOPZ E1 LOOPNE / LOOPNZ E0 JCXZ E3 (CX) <> 0 ZF = 1 (CX) <> 0 ZF = 0 (CX) = 0 Мнемоника LOOP Описание действия Декремент CX и переход, если (CX) не равно 0. Декремент CX и переход, если "равно" или "нуль". Декремент CX и переход, если "не равно" или "не нуль". Переход, если (CX) равно 0. Команды прерывания Команды прерывания обеспечивают действие, аналогичное сигналам прерывания, т.е. переключение с одной программы на другую. Адрес перехода содержится в таблице векторов в памяти ЭВМ. Команда INT имеет три формата INT 11001100 INTO 11001110 INT mun 11001101 Mun Тип прерывания задает адрес вектора в таблице векторов. Адрес=mun*4 INT – специальное прерывание по контрольной точке, соответствует INT# INTO – специальное прерывание по переполнению, соответствует INT4 При возникновении прерывания или выполнении команды прерывания в МП реализуется последоваельность прерывания, обеспечивающая запись в стек текущего значения регистров F, CS, IP. В IP и CS помещается новое значение из двойного слова таблицы векторов, адрес которого определяется типом прерывания. Флажки регистра флагов IF и TF сбрасываются. Новое значение IP и CS определяет начальный адрес процедуры прерывания. Возврат в прерванную программу осуществляется специальной командой: IRET 11001110 По этой команде извлекаются из стека три слова и загружается последовательно в регистры IP, CS и F. Тем самым восстанавливается состояние, имевшее место при прерывании. Команды строчной обработки Команды строчной обработки или цепочечные команды имеют длину один байт и могут оперировать как со словом, так и с байтом. Вне префикса повторения REP они оперируют только одним словом или байтом. Такие одиночные цепочечные команды называются примитивами. Независимо от формата примитива операнды определяются содержимым регистров SI, DI, DS, ES. Кроме выполнения указанной операции примитив автоматически вызывает инкремент или декремент регистров SI и (или) DI. Такое автоиндексирование позволяет повторяющееся использование примитива для последовательной обработки смежных байт или слов. Направление изменения индекса определяется флажком DF, если DF=0, то автоинкремент. Иначе – автодекремент. Использование цепочечных команд по сравнению с обычными дает следующие преимущества: - Длина команды – 1 байт - Оба операнда в памяти - Автоиндексирование делает ненужным явные команды изменения индексов, что увеличивает производительность. Циклы с примитивами могут быть организованы обычным образом, с помощью команд ветвления или LOOP, а также с помощью префикса повторения REP. Машинный код префикса REP 1111001Z Префикс REP обеспечивает автоматическое изменение регистра CX, проверку на конец и повторение указанного примитива. С префиксом REP=F3 примитивы MOVS, LODS, STOS (не изменяющие флажков в регистре F) повторяются в соответствии со следующими правилами: 1) Если CX = 0 закончить операцию 2) Декремент CX на 1 3) Выполнить примитив 4) Повторить сначала При работе с примитивами, изменяющими флажки регистра F (CMPS и SCAS) повторение будет идти со следующими правилами: 1) Если CX = 0 или Z = ZF закончить операцию (Z – нулевой бит кода операции REP) 2) Декремент CX на 1 3) Выполнить примитив 4) Повторить сначала - Пересылка байта/слова MOVS / MOVSB / MOVSW dst src 1010010 w dst src 1010011 w - Сравнить байты/слова CMPS / CMPSB / CMPSW (src) – (dst) и установка признаков - Сравнить байты/слова с содержимым аккумулятора SCAS / SCASB / SCASW dst src 1010111 w (src) – (dst) и установка признаков - Загрузка байта/слова в аккумулятор LODS / LODSB / LODSW src 1010110 w - Запись содержимого аккумулятора в память STOS / STOSB / STOSW dst 1010101 w Команды манипуляции со флажками Таблица 5. Мнемоника CLC CMC STC CLD STD CLI STI КОП 16-рич. F8 F5 F9 FC FD FA FB Название и действие Сброс признака переноса (CF = 0) Инвертирование признака переноса (CF = CF) Установка признака переноса (CF = 1) Сброс признака направления (DF = 0) Установка признака направления (DF = 1) Запрет прерывания (IF = 0) Разрешение прерывания (IF = 1) Команды управления микропроцессором - Останов HLT F4 11110100 - Ожидание сигнала на вход TEST микропроцессора WAIT 9B 10011011 90 10010000 - Нет операции NOP - Префикс захвата магистрали LOCK 11110000 - Выборка кода операции ORC и операнда srce для внешнего процессора (сопроцессор 1810ВМ87). ESC ops, srce 11001101 mun Доцент кафедры Вычислительная техника Кочешков А.А.