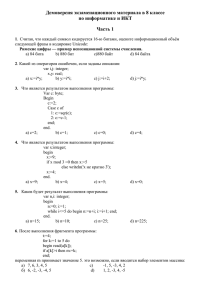

ЛАБ_ВТИТ_ОЛН

реклама

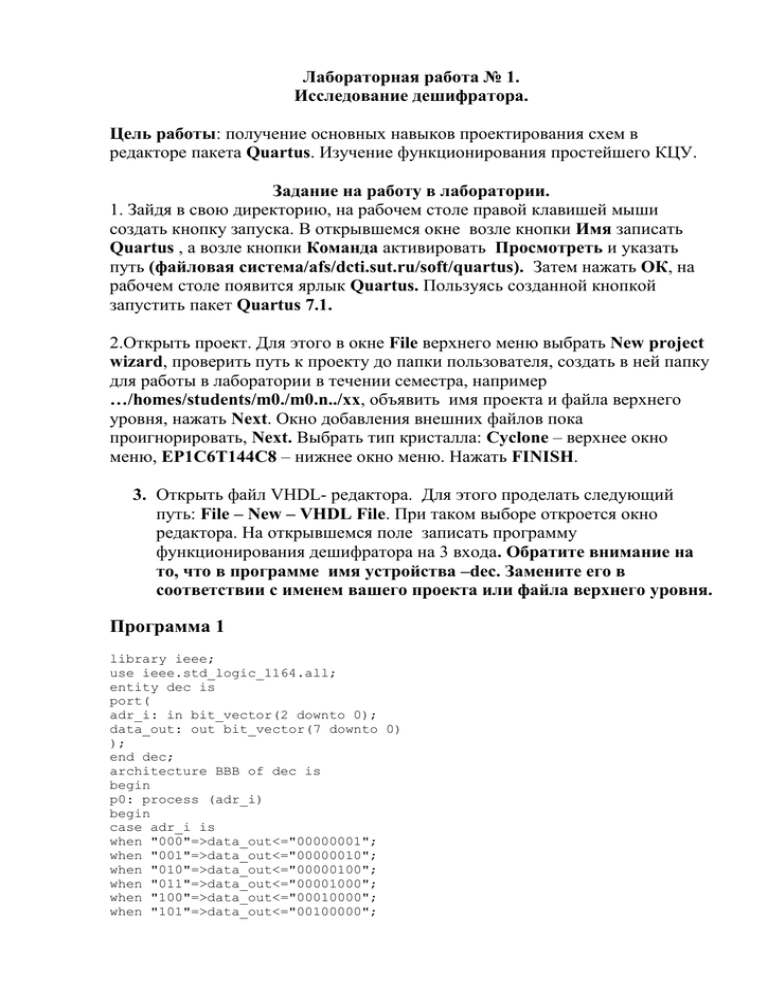

Лабораторная работа № 1. Исследование дешифратора. Цель работы: получение основных навыков проектирования схем в редакторе пакета Quartus. Изучение функционирования простейшего КЦУ. Задание на работу в лаборатории. 1. Зайдя в свою директорию, на рабочем столе правой клавишей мыши создать кнопку запуска. В открывшемся окне возле кнопки Имя записать Quartus , а возле кнопки Команда активировать Просмотреть и указать путь (файловая система/afs/dcti.sut.ru/soft/quartus). Затем нажать ОК, на рабочем столе появится ярлык Quartus. Пользуясь созданной кнопкой запустить пакет Quartus 7.1. 2.Открыть проект. Для этого в окне File верхнего меню выбрать New project wizard, проверить путь к проекту до папки пользователя, создать в ней папку для работы в лаборатории в течении семестра, например …/homes/students/m0./m0.n../xx, объявить имя проекта и файла верхнего уровня, нажать Next. Окно добавления внешних файлов пока проигнорировать, Next. Выбрать тип кристалла: Cyclone – верхнее окно меню, EP1C6T144C8 – нижнее окно меню. Нажать FINISH. 3. Открыть файл VHDL- редактора. Для этого проделать следующий путь: File – New – VHDL File. При таком выборе откроется окно редактора. На открывшемся поле записать программу функционирования дешифратора на 3 входа. Обратите внимание на то, что в программе имя устройства –dec. Замените его в соответствии с именем вашего проекта или файла верхнего уровня. Программа 1 library ieee; use ieee.std_logic_1164.all; entity dec is port( adr_i: in bit_vector(2 downto 0); data_out: out bit_vector(7 downto 0) ); end dec; architecture BBB of dec is begin p0: process (adr_i) begin case adr_i is when "000"=>data_out<="00000001"; when "001"=>data_out<="00000010"; when "010"=>data_out<="00000100"; when "011"=>data_out<="00001000"; when "100"=>data_out<="00010000"; when "101"=>data_out<="00100000"; when "110"=>data_out<="01000000"; when "111"=>data_out<="10000000"; end case; end process; end ; 5.Сохранить и откомпилировать полученный файл. Путь к компилятору: Processing – Start Compilation, или соответствующий значок верхнего меню редактора. Если компилятор указывает на ошибки, обратиться к преподавателю или лаборанту. 6. Построить временные диаграммы работы устройства. Для этого открыть файл временных диаграмм File – New – Others Files – Vector Waveform File. C помощью двух кликов мышью с левой стороны от вертикальной оси открыть окно Insert Node or Bus, выбрать в нем кнопку Node Finder. В разделе Filter выбрать Pins all, затем нажать List и проверить наличие списка выводов схемы в левом окне. Перенести список в правую часть с помощью кнопки >>, нажать OK. Временные интервалы – клик на обозначении вывода, обращение к опции C бокового меню, выбор в открывшемся окне пути Timing, установка временного интервала в ns. (20ns, 40ns, 80ns). Сохранить файл и обратиться к симулятору: Processing – Start Simulation или соответствующий значок верхнего меню редактора. При получении сообщения об ошибках обратиться к преподавателю или лаборанту. Если симуляция прошла без ошибок, проанализировать полученные диаграммы. Отчет должен содержать программу устройства и диаграммы его работы. В качестве проверки полученных знаний попробуйте самостоятельно составить программу работы шифратора на 4 входа и проанализировать временные диаграммы этого устройства. Внимание! При записи программы по образцу, указанному выше необходимо запись bit_vector заменить на std_logic_vector, adr_i на y_i и data_out на adr_out и, т.к. оператор требует записи всех комбинаций, последняя строка описания поведения устройства имеет следующий вид: when others=>adr_out<=”ZZ” Лабораторная работа № 2. Исследование работы демультиплексора. Цель работы: изучение принципов работы демультиплексора. Написание простейшей программы на VHDL. Постановка задачи. На примере демультиплексора на 3 адресных входа рассмотреть принцип функционирования данного типа КЦУ. Выходы устройства соединить со светодиодной панелью макета , адресные входы и информацию подключить к тумблерам. Имена адресных входов: Аdr_i[2..0], информационного входа - D, выходов Y[7..0], Рекомендуемые интервалы для временных диаграмм: Аdr_i[0] –40нс, Аdr_i[1] –80нс, Аdr_i[2] –160нс, D – 15нс. Порядок выполнения работы. Запустить Quartus 7.1. (/afs/dcti.sut.ru/soft/quartus). Открыть новый проект, прописав его в свою директорию ../homes/students/m0.../m0...n.../xx Создать файл VHDL File и записать в него программу для демультиплексора на 3 адресных входа по образцу, записанному в Прогр.1. Сохранить и откомпилировать файл. Открыть редактор временных диаграмм. Построить диаграммы работы устройства, следуя записанным рекомендациям. Выводы записывать в файл временных диаграмм списком. Для получения списка выводов шины кликнуть на знак + возле ее обозначения. Продемонстрировать временные диаграммы преподавателю. Вызвать планировщик (Pin Planer) и произвести разводку выводов схемы, руководствуясь схемой панели макета. В нижней части полученного окна будет представлен список выводов, в верхней – внешний вид кристалла. Против наименования каждого элемента списка в позиции Location двумя кликами мышью вызвать список выводов кристалла. Затем выбрать один для соединения с выводом устройства в соответствии с выданной схемой макета. (Или левой клавишей мыши отметить название вывода и, не отпуская клавиши, переместить его на ножку кристалла). Например: Аdr_i[0], Аdr_i[1], Аdr_i[2] соединяем с выводами 42, 40 и 38, D – с выводом 48, а выходы Y[7..0] – c выводами 57, 53, 51, 49, 47, 41, 39 и 37. Скомпилировать файл. Результат разводки продемонстрировать преподавателю! Вызвать программатор (Tools - Programmer). С помощью клавиши– Hardware Setup выбрать адаптер – Byteblaster MV. В строке с именем загружаемого файла поставить галочку на пункте Program/Configure. Убедится в том, что макет подключен и запустить программатор (клавиша Start). Результат работы продемонстрировать преподавателю. Отчет по данной работе должен содержать схему устройства, программу и графики работы. Программа. 2. library ieee; use ieee.std_logic_1164.all; entity dms is port( adr_i: in bit_vector(2 downto 0); d: in bit; data_out: out bit_vector(7 downto 0) ); end dms; architecture BBB of dms is begin process (adr_i) begin data_out(0)<=(not(adr_i(0)))and(not(adr_i(1)))and (not(adr_i(2)))and(d); data_out(1)<=(adr_i(0))and(not(adr_i(1)))and (not(adr_i(2)))and(d); data_out(2)<=(not(adr_i(0)))and(adr_i(1))and (not(adr_i(2)))and(d); data_out(3)<=(adr_i(0))and(adr_i(1))and(not(adr_i(2)))and(d ); data_out(4)<=(not(adr_i(0)))and(not(adr_i(1)))and(adr_i(2)) and(d); data_out(5)<=(adr_i(0))and(not(adr_i(1)))and(adr_i(2))and(d ); data_out(6)<=(not(adr_i(0)))and(adr_i(1))and(adr_i(2))and(d ); data_out(7)<=(adr_i(0))and(adr_i(1))and(adr_i(2))and(d); end process; end ; Лабораторная работа № 3 Проектирование 4-разрядного сумматора. Цель работы: Получение навыков работы в пакете Quartus; построение многоуровнего проекта, изучение функционирования простейшего КЦУ. Задание на работу в лаборатории. Построить схему четырехразрядного сумматора, взяв за основу схемы полусумматора и полного одноразрядного сумматора. В редакторе временных диаграмм задать форму входных сигналов и получить диаграммы выходов. Порядок выполнения работы. 4. Через ярлык на рабочем столе произвести загрузку пакета Quartus. 5. Создать новый проект в своей папке xx, назвав его summ. 6. Открыть VHDL файл и записать в него прогр. 1. Сохранить файл под именем add1 и установить его старшим в иерархии проекта. Для этого проделать путь от верхнего меню View –> Utility Windows –> Project Navigator. В левой верхней части экрана откроется окно навигатора. Список файлов открывается средней клавишей (Files). VHDL – файлы относятся файлам, образующим проект. Чтобы установить файл старшим в иерархии, необходимо выбрать его и кликом правой клавишей мыши выбрать Set a Top-Level Entity. 7. Откомпилировать файл. Во время компиляции обращайте внимание на сообщения компилятора, где указывается имя проекта и компилируемого файла. Эта информация всегда поможет вам избежать ошибок. 8. Пользуясь методикой работы 1, открыть файл временных диаграмм и построить диаграммы полусумматора, взяв интервал для a1 - 20ns, а для b1 – 30ns. Сохранить файл. Для симуляции временного файла надо воспользоваться строчкой Simulator Tool меню Processing. Через поиск найти название последнего временного файла и нажать Start. Просмотреть результат, нажав в том же окне справа Simulator Report. Проанализируйте полученный результат, запишите задержку. 9. Открыть новый VHDL файл и записать в него прогр. 2. Сохранить файл под именем add11 и установить его старшим в иерархии проекта. Откомпилировать файл. 10. Построить временные диаграммы одноразрядного сумматора, взяв интервалы для a1 - 20ns, для b1 – 30ns, для c1 – 50ns. Проанализировать результат симуляции. 11.Открыть новый VHDL файл и записать в него прогр. 3. Сохранить файл под именем add4 и установить его старшим в иерархии проекта. Откомпилировать файл. 12.Построить временные диаграммы четырехразрядного сумматора. При построении воспользуйтесь клавишей бокового меню, позволяющей изображать произвольные временные интервалы, на ней изображены два фронта со стрелкой в две стороны. Число a установить равным 10 на интервале 30ns и, затем, на интервале 50ns равным 3. Число b установить равным 7 на интервале 50ns и, затем на интервале 50ns равным 13. Для появления всех разрядов шины на диаграмме кликнуть на + возле имени шины. Проанализируйте результат симуляции. 13. Создать библиотечный модуль 4-разрядного сумматора. Для этого открыть VHDL-файл с прогр. 3, в меню File выберите последовательно Create/Update и Create Symbol Files for Current File. 14. Далее вам необходимо включить в свой проект два файла периферийных устройств. Имена файлов multiplexor, decoder. Все файлы лежат в папке материалы. Ваши действия: File – Open производите поиск afs – dcti.sut.ru – matherials – sk -3kurs – далее до списка файлов. Выбираете multiplexor, записываете в проект – File – Save As и производите поиск согласно пути к своему проекту, указанному в верхней строке экрана. Для записанного файла создайте библиотечный модуль. Аналогичные действия проделайте для файла decoder. 15. Открыть файл графического редактора File – New – Block Diagram/Schematic File. Двумя кликами мыши в поле листа вызвать библиотеку символов и последовательно вывести на лист редактора модули add4, multiplexor, decoder. Кроме этих символов вывести из библиотеки на лист символы gnd, input и output. Входы модуля add4 a[3..0], b[3..0] соединить с примитивами input, выходы суммы S[3..0] со входами data0[…..] модуля multiplexor, а выход c вывести и назвать линию c[0]. К примитиву gnd подвести 3 линии, поименовав их c[1], c[2] и c[3]. Вход data1 модуля multiplexor вывести и поименовать шину c[3..0]. Вход clk модуля multiplexor вывести через input. Выходы модуля multiplexor columns[3..0], определяющие количество используемых сегментных индикаторов, вывести и поименовать линию col[3..0], а выходы outputdata[] соединить со входами indata[3..0] модуля decoder. В таблицу значений параметров модуля multiplexor в строке значений WIDTH заменить 15 на 4. Для обозначения количества индикаторов взять отдельный примитив output. Выходы модуля decoder соединить с примитивом output. Поименовать входы и выходы полученного устройства. Для этого необходимо произвести два клика на названии pin name примитива input и output. Название может не совпадать с именем выводов модулей, но должно содержать одинаковое количество переменных. Например: A[3..0], B[3..0] для обозначения входов, COL[1..0], OUT[8..0] – для обозначения выходов. 16. Созданный файл графического редактора сохранить под именем проекта summ, установить старшим в иерархии и откомпилировать. 17. Открыть Pin Planner и произвести разводку выводов. Входы A[3..0] и B[3..0] соединить с тумблерами (38, 40, 42, 48; 50, 52, 56, 58), вход clk с генератором тактовой частоты макета(16). Выходы COL[1..0] с питанием индикаторов (109, 110), а выходы OUT[8..0] с сегментами, начиная с нулевого (74, 73, 72, 70, 61, 79, 75, 69, 71). Откомпилировать файл планировщика. 18. Подключить макет. Вызвать программатор и, убедившись что загружен нужный файл, подключен требуемый тип кристалла и ByteBlaster, поставить галочку в клетку Program/Configure и нажать Start. Продемонстрировать преподавателю работу устройства на макете. Программа. 3.1 library ieee; use ieee.std_logic_1164.all; entity add1 is port(a1,b1:in BIT;c1,s1:out BIT); end add1; architecture struct_1 of add1 is begin s1<= ((a1 and (not b1)) or ((not a1) and b1)); c1<= a1 and b1; end struct_1; Программа. 3.2 library ieee; use ieee.std_logic_1164.all; entity add11 is port(a2,b2,c1:in BIT;c2,s2:out BIT); end add11; architecture struct_1 of add11 is begin s2<=(a2 xor b2) xor c1; c2<= (a2 and b2) or ((a2 xor b2)and c1); end struct_1; Программа.3.3 library ieee; use ieee.std_logic_1164.all; entity add4 is port(a,b:in bit_vector(3 downto 0); s:out bit_vector(3 downto 0); c : out bit); end add4; architecture structural of add4 is component add1 port(a1,b1:in BIT;c1,s1:out BIT); end component; component add11 port (c1,a2,b2:in BIT; c2,s2:out BIT); end component; signal c_in: bit_vector(2 downto 0); begin p0: add1 port map(a1=>a(0),b1=>b(0),c1=>c_in(0),s1=>s(0)); p1: add11 port map(c1=>c_in(0),a2=>a(1),b2=>b(1),c2=>c_in(1),s2=>s(1)); p2: add11 port map(c1=>c_in(1),a2=>a(2),b2=>b(2),c2=>c_in(2),s2=>s(2)); p3: add11 port map(c1=>c_in(2),a2=>a(3),b2=>b(3),c2=>c,s2=>s(3)); end structural; Отчет должен содержать программы работы устройств с их названиями и временными диаграммами их работы. Лабораторная работа № 4. Исследование работы триггера. Цель работы: изучение принципов функционирования простейшего конечного автомата. Постановка задачи. На примере простейшей ячейки асинхронного RSтриггера и двух синхронных триггеров, D-триггера и JK-триггера, изучить назначение входов и принципы функционирования устройства. Для этого в пакете Quartus записать программы функционирования устройств на языке VHDL, а затем построить временные диаграммы. Рекомендуемые интервалы времени: RS-триггер: s – 80 нс с начальным уровнем 1, r – 50нс с начальным уровнем 0. D – триггер: для сигналов синхронизации – 20нс, информационного D-входа – 90нс с начальным уровнем 1, для s – входа при базовом уровне 1 короткий 0 от 110 до 130 нс, для r – входа при базовом уровне 1 короткий 0 от 270 до 290 нс. JK – триггер: для сигналов синхронизации – 20нс, информационных JKвходов J– 110нс с начальным уровнем 1 и K - 70 нс с начальным уровнем 0, , для s – входа при базовом уровне 1 короткий 0 от 150 до 170 нс, для r – входа при базовом уровне 1 короткий 0 от 30 до 50 нс. . Порядок выполнения работы. 1.Загрузить Quartus, создать проект. 2. Открыть VHDL файл, записать программу 4.1, отражающую работу асинхронного RS- триггера. 3. Сохранить файл, установить его старшим в иерархии и откомпилировать. 4. Открыть редактор временных диаграмм. Построить диаграммы работы. Интервалы выбрать из списка рекомендованных. Зарисовать диаграммы в отчет. 5. Открыть новый VHDL файл, записать программу 4.2, отражающую работу D – триггера. 6. Сохранить файл под другим именем, установить его старшим в иерархии и откомпилировать. 7. Открыть редактор временных диаграмм. Построить диаграммы работы . Интервалы выбрать из списка рекомендованных. Зарисовать диаграммы в отчет. 8. Открыть новый VHDL файл, записать программу 4.3, отражающую работу JK – триггера. 9. Дать имя файлу и сохранить его, установить старшим в иерархии и откомпилировать. 10. . Открыть редактор временных диаграмм. Построить диаграммы работы . Интервалы выбрать из списка рекомендованных. Зарисовать диаграммы в отчет. При получении временных диаграмм для каждого типа триггера результаты демонстрировать преподавателю. Отчет должен содержать программы работы устройств , подкрепленные проверкой на временной диаграмме. Программа 4.1 library ieee; use ieee.std_logic_1164.all; entity trs is generic (delay:time:=2 ns); port( r,s: in std_logic; q,nq: out std_logic ); end trs; architecture arch of trs is signal p,np: std_logic; begin process (r,s) begin if r='0' and s='0' then p<='1' after delay; np<='1' after delay; elsif r='0' and s='1' then p<='0' after 2*delay; np<='1' after delay; elsif r='1' and s='0' then p<='1' after delay; np<='0' after 2*delay; elsif r='1' and s='1'then p<='X'; np<='X'; end if; end process; q<=p; nq<=np; end arch; Программа 4.2 library ieee; use ieee.std_logic_1164.all; entity tr is port( data_i: in std_logic; clk_i: in std_logic; s : in std_logic; r : in std_logic; data_out: out std_logic ); end tr; architecture arch of tr is begin process (clk_i,s,r) begin if r='0' then data_out<='0'; elsif s='0' then data_out<='1'; elsif(rising_edge(clk_i)) then data_out <= data_i; end if; end process; end arch; Программа4.3 library ieee; use ieee.std_logic_1164.all; entity trjk2 is port( clk,s,r,j,k: in std_logic; data_out: out std_logic ); end trjk2; architecture arch of trjk2 is signal q: std_logic; begin process (clk,r,s) begin if r='0' then q<='0'; elsif s='0' then q<='1'; elsif(rising_edge(clk)) then if(j='1') then if(k='0') then q<='1'; elsif(k='1')then q<=(not(q)); end if; elsif (j='0') then if(k='0') then q<=(q or '0'); elsif (k='1') then q<='0'; end if; end if; end if; end process; data_out<=q; end arch; Лабораторная работа № 5. Исследование счетчиков. Цель работы: изучение функционирования схем синхронных счетчиков. Сравнительный анализ синхронных счетчиков. В работе предлагаются для изучения VHDL - программы двоичных четырехразрядных счетчиков: суммирующего, вычитающего и реверсивного. По диаграммам работы проверяется порядок счета счетчиков. Реверсивный счетчик проектируется для работы в кристалле Cyclone EP1C6T144C8. Порядок выполнения работы. Создать новый проект, открыть VHDL- файл и записать программу 5.1, отражающую функционирование синхронного суммирующего счетчика. Сохранить файл и установить его старшим в иерархии. Откомпилировать файл. Построить временные диаграммы работы счетчика, задав интервал синхроимпульсов 20нс. Сохраненный временной(.vwf) файл не хранится по умолчанию в корзине симулятора, поэтому симуляция должна следовать по пути: Processing – Simulator Tool – через поиск … находите необходимый файл – Start. По окончании симуляции нажмите Report и проанализируйте результат.. Открыть новый VHDL - файл и записать программу 5.2, отражающую функционирование синхронного вычитающего счетчика. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать. По методике, изложенной в п.2 построить временные диаграммы работы счетчика, задав интервал синхроимпульсов 20нс. Открыть новый VHDL - файл и записать программу 5.3, отражающую функционирование синхронного реверсивного счетчика. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать. Построить временные диаграммы работы счетчика. Тактовая частота аналогична первому варианту, интервал реверса – 650нс. Вернувшись в файл VHDL, cоздать библиотечный модуль реверсивного счетчика. Из папки материалы, пользуясь методикой, описанной в п. лабораторной работы №3 записать в свой проект 3 файла antiring, multiplexor и decoder и создать для каждого библиотечный модуль. В новом файле графического редактора объединить модули счетчика с вновь созданными модулями периферийных устройств. Синхросигнал завести от кнопки через модуль antiring, выходы счетчика соединить со входами data0[..] модуля multiplexor, вход clk модуля multiplexor обозначить теми же буквами, что записаны в примитиве input для входа clock модуля antiring. Выходы columns модуля multiplexor поименовать col[3..0], отдельно вывести output, назвав его col[0]. В таблице изменить WIDTH на 4, выходы данных модуля multiplexor связать со входами данных модуля decoder. Выходы модуля decoder вывести через output. Реверс установить от любого тумблера через input. Сохранить файл, установить его старшим в иерархии и откомпилировать. Произвести разводку в кристалл для полученного проекта. Контакты кнопки – pin 59, 60. Запрограммировать кристалл и убедиться в правильности работы схемы. Отчёт должен содержать: программы функционирования счётчиков и временные диаграммы их работы. Программа 5.1 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt44 is port( clk: in std_logic; ena : in std_logic; res : in std_logic; q: out std_logic_vector(3 downto 0) ); end cnt44; architecture arch of cnt44 is signal cnt: std_logic_vector(3 downto 0); begin process (clk,res) begin if (res = '0') then cnt<=(others=>'0'); elsif(rising_edge(clk)) then if(ena ='1') then cnt <=cnt + "0001"; end if; end if; end process; q <= cnt; end arch; Программа 5.2 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt441 is port( clk: in std_logic; ena : in std_logic; res : in std_logic; q: out std_logic_vector(3 downto 0) ); end cnt441; architecture arch of cnt441 is signal cnt: std_logic_vector(3 downto 0); begin process (clk,res) begin if (res = '0') then cnt<=(others=>'0'); elsif(rising_edge(clk)) then if(ena ='1') then cnt <=cnt - "0001"; end if; end if; end process; q <= cnt; end arch; Программа 5.3 llibrary ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt442 is port( clk: in std_logic; ena : in std_logic; res : in std_logic; rev : in std_logic; q: out std_logic_vector(3 downto 0) ); end cnt442; architecture arch of cnt442 is signal cnt: std_logic_vector(3 downto 0); begin process (clk,res) begin if (res = '0') then cnt<=(others=>'0'); elsif(rising_edge(clk)) then if(ena ='1') then if (rev ='0') then cnt <=cnt + "0001"; elsif (rev='1') then cnt <=cnt - "0001"; end if; end if; end if; end process; q <= cnt; end arch; Лабораторная работа № 6. Исследование регистров. Цель работы: знакомство с работой параллельных и последовательных регистров. В работе предлагаются для изучения регистры сдвига на 8 разрядов последовательный и последовательно-параллельный . А также параллельный четырехразрядный регистр (буферный и защелка) . Порядок выполнения работы. Последовательные регистры. Создать проект. Открыть новый VHDL- файл и записать программу 6.1, отражающую функционирование последовательного регистра на 8 разрядов. Сохранить файл, установить его старшим в иерархии и откомпилировать. Открыть редактор временных диаграмм. Изобразить диаграммы при интервалах синхроимпульса – 20нс, данные –при базовом уровне «0» на интервалах от 10нс до 50 нс уровень «1» и от 130нс до 200нс уровень «1». Зарисовать полученные диаграммы, записать задержки. (для изображения отдельных интервалов необходимо воспользоваться иконкой бокового меню, показанной на рисунке) 19.Открыть новый VHDL- файл и записать программу 6.2, отражающую функционирование последовательно-параллельного регистра на 8 разрядов. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать. 20.По методике, изложенной в п.2, построить временные диаграммы для последовательно-параллельного регистра. 21.Открыть новый VHDL- файл и записать программу 6.3, отражающую функционирование параллельного регистра на 4 разряда. Сохранить файл под новым именем, установить его старшим в иерархии и откомпилировать. 22.Построить диаграмму работы устройства при следующих параметрах: синхронизация – 20нс; данные – D0,D2 – 35нс, D1,D3 – 50нс; ena – 170нс; ctrl – 200нс. 23.Создать библиотечный модуль устройства. Отчет должен содержать программы работы исследуемых устройств и их временные диаграммы. Программа 6.1 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity regsdv is port(clk,d_in:in std_logic; d_out:out std_logic); end regsdv; architecture bb of regsdv is signal shift: std_logic_vector (6 downto 0); begin process (clk) variable i: integer range 7 downto 0; begin if(rising_edge(clk)) then shift(0)<=d_in; for i in 1 to 6 loop shift(i)<=shift(i-1); end loop; d_out<=shift(6); end if; end process; end bb; Программа 6.2 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity regsdv1 is port(clk,d_in:in std_logic; d_out:out std_logic_vector (7 downto 0)); end regsdv1; architecture bb of regsdv1 is signal shift: std_logic_vector (7 downto 0); begin process (clk) variable i: integer range 7 downto 0; begin if(rising_edge(clk)) then shift(0)<=d_in; for i in 1 to 7 loop shift(i)<=shift(i-1); end loop; end if; end process; d_out<=shift; end bb; Программа 6.3 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity reg4 is port( data_i: in std_logic_vector(3 downto 0); clk_i: in std_logic; ena : in std_logic; ctrl : in std_logic; data_out: out std_logic_vector(3 downto 0) ); end reg4; architecture arch of reg4 is signal regist: std_logic_vector(3 downto 0); begin process (clk_i) begin if(rising_edge(clk_i)) then if(ena ='1') then regist <= data_i; end if; end if; end process; data_out <= regist when ctrl = '1' else "ZZZZ"; end arch;